Адресное пространство процессора это

Обновлено: 07.07.2024

Системная шина процессора предназначена для обмена информацией микропроцессора с любыми внутренними устройствами микропроцессорной системы (контроллера или компьютера). В качестве обязательных устройств, которые входят в состав любой микропроцессорной системы, можно назвать ОЗУ, ПЗУ, таймер и порты ввода-вывода. Структурная схема простейшего микропроцессорного устройства приведена на рисунке 1.

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяется для увеличения производительности процессора и используется только в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных.

В понятие шины вкладывают разное значение при рассмотрении различных вопросов. В простейшем случае под понятием шина подразумевают параллельно проложенные провода, по которым передаЈтся двоичная информация. При этом по каждому проводу передаЈтся отдельный двоичный разряд. Информация может передаваться в одном направлении, как, например, для шины адреса или шины управления, или в различных направлениях (для шины данных). По шине данных информация передаЈтся либо к процессору, либо от процессора в зависимости от операции записи или чтения, которую в данный момент осуществляет процессор.

В любом случае все сигналы, необходимые для работы системной шины формируются микросхемой процессора как это рассматривалось при изучении блока обработки данных. Иногда для увеличения скорости обработки информации функции управления системной шины берЈт на себя отдельная микросхема (например контроллер прямого доступа к памяти или сопроцессор). Арбитраж доступа к системной шине при этом осуществляет контроллер системной шины (в простейшем случае достаточно сигнала занятости шины).

В некоторых случаях в понятие шина дополнительно включают требования по уровням напряжения, которыми представляются нули и единицы, передаваемые по еЈ проводам. В состав требований могут быть включены длительности фронтов передаваемых сигналов, типы используемых разъЈмов и их распайка, последовательность передаваемых сигналов и скорость их передачи.

Рисунок 1. Структурная схема подключения микропроцессорных устройств к системной шине.

При подключении различных устройств к системной шине возникает вопрос - как различать эти устройства между собой? Единственный способ сделать это использовать индивидуальный адрес для каждого устройства, подключенного к системной шине микропроцессора. Так как адресация производится к каждой ячейке устройства индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством и адресного пространства микропроцессорного устройства в целом.

Адресное пространство микропроцессорного устройства.

Адресное пространство микропроцессорного устройства изображается графически прямоугольником, одна из сторон которого представляет разрядность адресуемой ячейки этого микропроцессора, а другая сторона - весь диапазон доступных адресов для этого же микропроцессора. Обычно в качестве минимально адресуемой ячейки памяти выбирается восьмиразрядная ячейка памяти (байт). Диапазон доступных адресов микропроцессора определяется разрядностью шины адреса системной шины. При этом минимальный номер ячейки памяти (адрес) будет равен 0, а максимальный определяется из формулы:

Для шестнадцатиразрядной шины это будет число 65535 (64K). Адресное пространство этой шины и распределение памяти микропроцессорной системы, изображЈнной на рисунке 1, приведено на рисунке 2, а распределение памяти микропроцессорной системы, изображЈнной на рисунке 1, приведено на рисунке 3.

Рисунок 2. Адресное пространство шестнадцатиразрядной шины адреса.

Рисунок 3. Распределение памяти микропроцессора с шестнадцатиразрядной шиной адреса.

Микропроцессоры после включения питания и выполнения процедуры сброса всегда начинают выполнение программы с определЈнного адреса, чаще всего нулевого. Однако есть и исключения. Например процессоры, на основе которых строятся универсальные компьютеры IBM PC или Macintosh стартуют не с нулевого адреса. Программа должна храниться в памяти, которая не стирается при выключении питания, то есть в ПЗУ.

Выберем для построения микропроцессорной системы микросхему ПЗУ объЈмом 2 килобайта, как это показано на рисунке 1. При рассмотрении построения блока обработки сигналов мы договорились, что процессор после сброса начинает работу с нулевого адреса, поэтому разместим ПЗУ в адресном пространстве начиная с нулевого адреса. Для того, чтобы нулевая ячейка ПЗУ оказались расположенной по нулевому адресу адресного пространства микропроцессора, старшие разряды шины адреса должны быть равны 0.

При построении схемы необходимо декодировать старшие пять разрядов адреса (определить, чтобы они были равны 0). Это выполняется при помощи дешифратора адреса, который в данном случае вырождается в пятивходовую схему "ИЛИ-НЕ" Это связано с тем, что внутри ПЗУ уже есть одиннадцативходовый дешифратор адреса. При использовании дешифратора адреса, обращение к ячейкам памяти выше двух килобайт не приведЈт к чтению ячеек ПЗУ, так как на входе выбора кристалла CS уровень напряжения останется высоким.

Теперь подключим микросхему ОЗУ. Для примера выберем микросхему объЈмом 8 Кбайт. Для выбора любой из ячеек этой микросхемы достаточно тринадцатибитового адреса, поэтому необходимо дополнительно декодировать три оставшихся разряда адреса. Так как начальные ячейки памяти адресного пространства уже заняты ПЗУ, то использовать нельзя. Выберем следующую комбинацию цифр 001 и используем известные нам принципы построения схемы по произвольной таблице истинности. Дешифратор адреса выродится в данном случае в трЈхвходовую схему "И-НЕ" с двумя инверторами на входе. Схема этого дешифратора приведена на рисунке 1. ПриведЈнный дешифратор адреса обеспечивает нулевой уровень сигнала на входе CS только при комбинации старших бит 000. Обратите внимание, что так как объЈм ПЗУ меньше объЈма ОЗУ, то между областью адресов ПЗУ и областью адресов ОЗУ образовалось пустое пространство неиспользуемых адресов памяти.

И, наконец, так как все микропроцессоры предназначены для обработки данных, поступающих извне, то в любой микропроцессорной системе должны присутствовать порты ввода-вывода. Порт ввода-вывода отображается в адресное пространство микропроцессорного устройства как одиночная ячейка памяти, поэтому порт ввода вывода можно разместить по любому свободному адресу. Проще всего построить дешифратор числа FFFFh. В этом случае дешифратор превращается в обычную 16-ти входовую схему "И-НЕ", поэтому и выберем эту ячейку памяти в адресном пространстве микропроцессора для размещения порта ввода-вывода.

Способы расширения адресного пространства микропроцессора.

Известно, что размер адресного пространства определяется разрядностью счЈтчика команд микропроцессора. Достаточно часто при развитии микропроцессорной системы возможности адресного пространства исчерпываются. В таком случае приходится прибегать к методам расширения адресного пространства.

Для расширения адресного пространства можно воспользоваться параллельным портом. Внешние выводы параллельного порта при этом используются в качестве старших битов адресной шины. Такой метод расширения адресного пространства называется страничным методом адресации. Регистр данных параллельного порта при использовании его для расширения адресного пространства будет называться переключателем страниц. Схема использования параллельного порта в качестве переключателя страниц памяти приведена на рисунке 4.

Рисунок 4. Использование параллельного порта в качестве переключателя страниц памяти.

В этой схеме параллельный порт используется в качестве простейшего контроллера памяти микропроцессорного устройства. При применении восьмиразрядного параллельного порта в микропроцессорной системе появились дополнительные восемь линий адреса. В результате адресное пространство микропроцессорной системы увеличилось до 16 Мегабайт. Структура нового адресного пространства приведена на рисунке 5, а принцип формирования нового адреса с использованием переключателя страниц приведЈн на рисунке 6.

Рисунок 5. Структура страничного адресного пространства.

Рисунок 6. Формирование адреса с использованием переключателя страниц.

Метод страничной адресации прост в реализации и при формировании адреса физической памяти не приводит к дополнительным временным задержкам, но при использовании многозадачного режима работы процессора для каждой активной задачи выделяется целая страница в системной памяти микропроцессора. При такой работе в системной памяти процессора остаЈтся много неиспользуемых областей. Решить возникшую проблему позволяет метод сегментной организации памяти.

При сегментном методе организации памяти для расширения адресного пространства используется базовый регистр, относительно которого производится адресация команд или данных в программе. Разрядность базового регистра обычно выбирают равной разрядности счЈтчика команд. В качестве базового регистра, как и при страничной организации памяти, можно использовать параллельный порт.

Адресное пространство при использовании сегментного метода адресации приведено на рисунке 7.

Рисунок 7. Пример адресного пространства с разделением на сегменты.

Количество сегментов определяется количеством базовых регистров. Сегменты могут перекрываться в адресном пространстве, и тем самым может регулироваться размер памяти, который отводится под каждый конкретный сегмент памяти. В компьютерах семейства IBM PC имеются четыре базовых регистра, определяющих сегмент данных, сегмент программы, сегмент стека и дополнительный сегмент. Информацию в базовые регистры заносит операционная система при переключении задач.

Рисунок 8. Формирование адреса при сегментной адресации.

ЕщЈ одним распространЈнным способом увеличения адресного пространства является применение окон. При использовании окон производится расширение не всего адресного пространства, а только его части. Внутри адресного пространства выделяется некоторая область, которая называется окном. В это окно может отображаться часть другого адресного пространства.

При использовании окон может быть использован как страничный метод отображения адресного пространства, так и сегментный метод отображения адресного пространства в окно.

При использовании страничного метода отображения, конкретная страница другого адресного пространства, которая в данный момент отображается в окно памяти, определяется переключателем страниц, построенному по такому же принципу как это было рассмотрено на рисунке 4.

При использовании сегментного метода отображения, конкретная область адресного пространства, которая будет отображаться в окно, определяется содержимым базового регистра. Если разрядность адреса вспомогательного адресного пространства, отображаемого в окно основной памяти, совпадает с разрядностью базового регистра, то любая область вспомогательной памяти может быть отображена в основную память с точностью до байта.

Принцип построения оконной адресации при отображении страниц показан на рисунке 9.

Рисунок 9. Применение окна для расширения адресного пространства.

Оконная адресация часто используется при развитии микропроцессорных семейств, когда размера областей памяти, отведЈнных для конкретных задач в младших моделях семейства, не хватает для старших моделей семейства, а при этом нужно поддерживать аппаратную совместимость с младшими моделями семейства. В качестве примера можно привести микросхемы I81c96 фирмы INTEL или TMS320c5410 фирмы Texas Instrument, где для расширения области регистров специальных функций используется оконная адресация.

Адресное пространство — это набор всех возможных адресов определённых модулей вычислительной системы, то есть, ячеек памяти, дисковых секторов, сетевых узлов, которые можно использовать для обращения к этим модулям в определённых режимах работы.

Введение

Модуль центрального процессора может выполнять информационный обмен с устройствами вне его границ лишь тогда, когда эти устройства обладают адресами. Эти устройства (объекты) могут именоваться адресуемыми или доступными программными средствами.

Адресом является код, который определяет номер ячейки памяти, регистра, триггера, входа логических элементов и тому подобное. В сегодняшних персональных компьютерах устройства (модули) взаимодействуют между собой при помощи магистрали, именуемой общей шиной. Общая шина состоит из следующих компонентов:

- Шина адреса, которая предназначена для указания адресов устройств, выбранных для передачи данных.

- Шина данных, которая служит собственно для трансляции информационных данных.

- Шина управления, которая предназначена для трансляции специализированных сигналов.

Адресное пространство

Адресное пространство задаёт количество допустимых различных кодовых комбинаций, именуемых адресами, которые разрешается посылать на шину адреса активному устройству. Это, естественно, не значит, что каждому адресу ставится в соответствие доступный программно компонент. Адресное пространство задаёт только уровень возможностей системы, то есть наибольшее количество доступных программными методами компонентов, которые могут входить в её состав.

Старший двоичный разряд кодового представления адреса разделяет всё адресное пространство на пару равных частей, два старших разряда могут разделить его на четыре равновесные части. А шестнадцать адресных разрядов поделят адресное пространство, имеющее ёмкость 64 К ровно на 64 К элементов, то есть ячеек памяти.

Готовые работы на аналогичную тему

Получить выполненную работу или консультацию специалиста по вашему учебному проекту Узнать стоимостьНа некотором периоде развития вычислительных устройств возникла проблема нехватки адресного пространства, то есть 64 К стали слишком «тесными».Одной из причин этого стала разработка микросхем памяти увеличенной ёмкости.

Самыми перспективными методиками, позволяющими расширить адресное пространство, является следующие:

- Метод окна.

- Метод базовых регистров.

- Метод банков.

Метод окна даёт возможность несложного решения указанных проблем.

Суть метода изображена на рисунке ниже:

Рисунок 1. Метод окна. Автор24 — интернет-биржа студенческих работ

Слева показана геометрическая интерпретация идеи методики, а справа её схемное воплощение.

- $G$ является адресуемыми элементами ЭВМ, которые располагаются в зоне $L_G$ адресного пространства $P$ электронной вычислительной машины.

- $H$ является адресным пространством основной памяти.

- $L_o$ является свободной зоной адресного пространства, где выделяется окно $W$.

Суть метода заключается в представлении на «большом» отрезке только участка «малого» отрезка. Данный участок должен соответствовать свободным адресам компьютера и именуется окном. Основная память имеет емкость, равную $V = 2^$ ячеек. Если, к примеру, $d=8, g=12$, то $V = 2^= 1M$ ячеек. Основная память может рассматриваться как набор $2^d$ страниц, при этом каждая страница обладает размером $2^g$ ячеек, который совпадает с размером окна. То есть, следует полагать, что $2^d$ является числом проекций окна, которые примыкают плотно друг к другу, заполняя собой весь размер оси основной памяти.

Так как окно выбирается в области неприменяемых адресов внутреннего адресного пространства компьютера, то вероятность конфликтов, связанных с параллельным выбором двух адресуемых компонентов (внутри и вне компьютера), полностью исключена.

Обобщением метода окна считается метод базовых регистров. Идея метода состоит в выделении в адресном пространстве не одного, а целого набора окон. При любом выполнении обращения к основной памяти применяется только одно окно. Проекции окон на «ось» основной памяти могут располагаться в различных местах данной оси, а также могут иметь совпадения. Расположение окон в адресном пространстве формируется в строго определённом порядке при помощи дешифратора. Углы наклона лучей определяются базовыми регистрами. Принципы назначения адресов основной памяти такие же, как и в методе окон.

Метод базовых регистров даёт возможность переноса в адресное пространство компьютера параллельно несколько разных страниц основной памяти, к примеру, пару страниц из области информационных данных и одну страницу из программной области. Схемное воплощение метода базовых регистров близко к методу окна.

Метод банков, аналогично двум предыдущим, также достаточно широко распространён. Термин «банк», в данном случае, подразумевает отдельные блоки памяти, которые могут содержать как оперативные, так и постоянные составляющие. Кроме стандартных магистральных входов и выходов, такие блоки памяти обладают дополнительным входом, который управляет разрешением работы. При работе данной системы компьютерный процессор при посредстве программно-доступных регистров выполняет открытие требуемого банка и оперирует с находящейся в нём информацией. Другие банки логическими методами отключаются от магистрали. В этом методе основным является то обстоятельство, что компьютер может вообще не иметь собственной памяти.

Для адресации операндов в физическом адресном пространстве программы используют логическую адресацию. Процессор автоматически транслирует логические адреса в физические, выдаваемые затем на системную шину.

Архитектура компьютера различает физическое адресное пространство (ФАП) и логическое адресное пространство (ЛАП). Физическое адресное пространство представляет собой простой одномерный массив байтов, доступ к которому реализуется аппаратурой памяти по адресу, присутствующему на шине адреса микропроцессорной системы . Логическое адресное пространство организуется самим программистом исходя из конкретных потребностей. Трансляцию логических адресов в физические осуществляет блок управления памятью MMU .

В архитектуре современных микропроцессоров ЛАП представляется в виде набора элементарных структур: байтов, сегментов и страниц. В микропроцессорах используются следующие варианты организации логического адресного пространства:

- плоское (линейное) ЛАП: состоит из массива байтов, не имеющего определенной структуры; трансляция адреса не требуется, так как логический адрес совпадает с физическим;

- сегментированное ЛАП: состоит из сегментов - непрерывных областей памяти, содержащих в общем случае переменное число байтов; логический адрес содержит 2 части: идентификатор сегмента и смещение внутри сегмента; трансляцию адреса проводит блок сегментации MMU ;

- страничное ЛАП: состоит из страниц - непрерывных областей памяти, каждая из которых содержит фиксированное число байтов. Логический адрес состоит из номера (идентификатора) страницы и смещения внутри страницы; трансляция логического адреса в физический проводится блоком страничного преобразования MMU ;

- сегментно-страничное ЛАП: состоит из сегментов, которые, в свою очередь, состоят из страниц; логический адрес состоит из идентификатора сегмента и смещения внутри сегмента. Блок сегментного преобразования MMU проводит трансляцию логического адреса в номер страницы и смещение в ней, которые затем транслируются в физический адрес блоком страничного преобразования MMU .

Таким образом, основой получения физического адреса памяти служит логический адрес . В какой-то степени логическое адресное пространство , с которым имеет дело программист, можно сравнить со структурой книги, где аналогом сегмента выступает рассказ, страница книги соответствует странице ЛАП, а искомая информация - это некоторое слово . При этом если память организована как линейная, то номер искомого слова задается в явном виде и просто отсчитывается от начала книги. При сегментном представлении памяти искомое слово определяется его номером в заданном рассказе. Страничное представление памяти предполагает задание информации о слове в виде номера страницы в книге и номера слова на указанной странице. При сегментно-страничном представлении логический адрес слова задается номером слова в определенном рассказе. В этом случае по оглавлению книги определяется номер страницы, с которой начинается указанный рассказ. Затем, зная количество слов на странице и положение слова в рассказе, можно вычислить страницу книги и положение искомого слова на этой странице.

Формирование физического адреса в универсальном микропроцессоре при различных режимах работы

Микропроцессор способен работать в двух режимах: реальном и защищенном.

При работе в реальном режиме возможности процессора ограничены: емкость адресуемой памяти составляет 1 Мбайт, отсутствует страничная организация памяти, сегменты имеют фиксированную длину 2 16 байт .

Этот режим обычно используется на начальном этапе загрузки компьютера для перехода в защищенный режим.

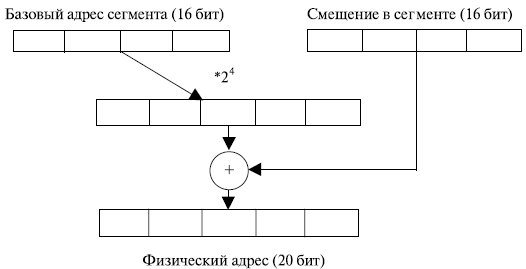

В реальном режиме сегментные регистры процессора содержат старшие 16 бит физического адреса начала сегмента. Сдвинутый на 4 разряда влево селектор дает 20-разрядный базовый адрес сегмента. Физический адрес получается путем сложения этого адреса с 16-разрядным значением смещения в сегменте, формируемого по заданному режиму адресации для операнда или извлекаемому из регистра EIP для команды (рис. 3.1). По полученному адресу происходит выборка информации из памяти.

Наиболее полно возможности микропроцессора по адресации памяти реализуются при работе в защищенном режиме. Объем адресуемой памяти увеличивается до 4 Гбайт, появляется возможность страничного режима адресации. Сегменты могут иметь переменную длину от 1 байта до 4 Гбайт.

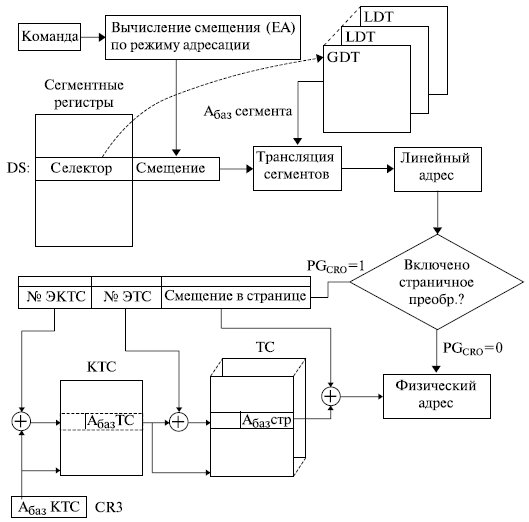

Общая схема формирования физического адреса микропроцессором , работающим в защищенном режиме, представлена на рис. 3.2.

Как уже отмечалось, основой формирования физического адреса служит логический адрес . Он состоит из двух частей: селектора и смещения в сегменте.

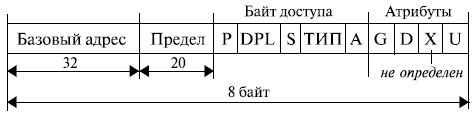

Селектор содержится в сегментном регистре микропроцессора и позволяет найти описание сегмента (дескриптор) в специальной таблице дескрипторов. Дескрипторы сегментов хранятся в специальных системных объектах глобальной ( GDT ) и локальных ( LDT ) таблицах дескрипторов. Дескриптор играет очень важную роль в функционировании микропроцессора , от формирования физического адреса при различной организации адресного пространства и до организации мультипрограммного режима работы. Поэтому рассмотрим его структуру более подробно.

Сегменты микропроцессора , работающего в защищенном режиме, характеризуются большим количеством параметров. Поэтому в универсальных 32-разрядных микропроцессорах информация о сегменте хранится в

Рис. 3.2. Формирование физического адреса при сегментно-страничной организации памяти

Структура дескриптора сегмента представлена на рис. 3.3.

Мы будем рассматривать именно структуру, а не формат дескриптора, так как при переходе от микропроцессора i286 к 32-разрядному МП расположение отдельных полей дескриптора потеряло свою стройность и частично стало иметь вид "заплаток", поставленных с целью механического увеличения разрядности этих полей.

32-разрядное поле базового адреса позволяет определить начальный адрес сегмента в любой точке адресного пространства в 2 32 байт (4 Гбайт).

Поле предела (limit) указывает длину сегмента (точнее, длину сегмента минус 1: если в этом поле записан 0, то это означает, что сегмент имеет длину 1) в адресуемых единицах, то есть максимальный размер сегмента равен 2 20 элементов.

Величина элемента определяется одним из атрибутов дескриптора битом G ( Granularity - гранулярность , или дробность):

Таким образом, сегмент может иметь размер с точностью до 1 байта в диапазоне от 1 байта до 1 Мбайт (при G = 0 ). При объеме страницы в 2 12 = 4 Кбайт можно задать объем сегмента до 4 Гбайт (при G = l ):

Так как в архитектуре IA-32 сегмент может начинаться в произвольной точке адресного пространства и иметь произвольную длину, сегменты в памяти могут частично или полностью перекрываться.

Бит размерности ( Default size ) определяет длину адресов и операндов, используемых в команде по умолчанию:

Конечно, этот бит предназначен не для обычного пользователя, а для системного программиста, применяющего его, например, для отметки сегментов для сбора"мусора" или сегментов, базовые адреса которых нельзя модифицировать. Этот бит доступен только программам, работающим на высшем уровне привилегий. Микропроцессор в своей работе его не меняет и не использует.

Байт доступа определяет основные правила обращения с сегментом.

Бит присутствия P (Present) показывает возможность доступа к сегменту. Операционная система (ОС) отмечает сегмент, передаваемый из оперативной во внешнюю память , как временно отсутствующий, устанавливая в его дескрипторе P = 0 . При P = 1 сегмент находится в физической памяти. Когда выбирается дескриптор с P = 0 (сегмент отсутствует в ОЗУ ), поля базового адреса и предела игнорируются. Это естественно: например, как может идти речь о базовом адресе сегмента, если самого сегмента вообще нет в оперативной памяти? В этой ситуации процессор отвергает все последующие попытки использовать дескриптор в командах, и определяемое дескриптором адресное пространство как бы"пропадает".

Возникает особый случай неприсутствия сегмента. При этом операционная система копирует запрошенный сегмент с диска в память (при этом, возможно, удаляя другой сегмент), загружает в дескриптор базовый адрес сегмента, устанавливает P = 1 и осуществляет рестарт той команды, которая обратилась к отсутствовавшему в ОЗУ сегменту.

Двухразрядное поле DPL ( Descriptor Privilege Level ) указывает один из четырех возможных (от 0 до 3) уровней привилегий дескриптора, определяющий возможность доступа к сегменту со стороны тех или иных программ (уровень 0 соответствует самому высокому уровню привилегий).

Бит обращения A (Accessed) устанавливается в"1" при любом обращении к сегменту. Используется операционной системой для того, чтобы отслеживать сегменты , к которым дольше всего не было обращений.

Пусть, например, 1 раз в секунду операционная система в дескрипторах всех сегментов сбрасывает бит А. Если по прошествии некоторого времени необходимо загрузить в оперативную память новый сегмент, места для которого недостаточно, операционная система определяет"кандидатов" на то, чтобы очистить часть оперативной памяти, среди тех сегментов, в дескрипторах которых бит А до этого момента не был установлен в"1", то есть к которым не было обращения за последнее время.

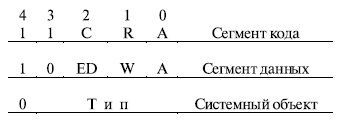

Поле типа в байте доступа определяет назначение и особенности использования сегмента. Если бит S ( System - бит 4 байта доступа) равен 1, то данный дескриптор описывает реальный сегмент памяти. Если S = 0 , то этот дескриптор описывает специальный системный объект , который может и не быть сегментом памяти, например, шлюз вызова, используемый при переключении задач, или дескриптор локальной таблицы дескрипторов LDT . Назначение битов <3. 0> байта доступа определяется типом сегмента (рис. 3.4).

В сегменте кода: бит подчинения, или согласования, C ( Conforming ) определяет дополнительные правила обращения, которые обеспечивают защиту сегментов программ. При C = 1 данный сегмент является подчиненным сегментом кода. В этом случае он намеренно лишается защиты по привилегиям. Такое средство удобно для организации, например, подпрограмм, которые должны быть доступны всем выполняющимся в системе задачам. При C = 0 - это обычный сегмент кода; бит считывания R ( Readable ) устанавливает, можно ли обращаться к сегменту только на исполнение или на исполнение и считывание, например, констант как данных с помощью префикса замены сегмента. При R = 0 допускается только выборка из сегмента команд для их выполнения. При R = 1 разрешено также чтение данных из сегмента.

Запись в сегмент кода запрещена. При любой попытке записи возникает программное прерывание .

В сегменте данных:

- ED ( Expand Down) - бит направления расширения. При ED = 1 этот сегмент является сегментом стека и смещение в сегменте должно быть больше размера сегмента. При ED = 0 - это сегмент собственно данных (смещение должно быть меньше или равно размеру сегмента);

- бит разрешения записи W(Writeable) . При W = 1 разрешено изменение сегмента. При W = 0 запись в сегмент запрещена, при попытке записи в сегмент возникает программное прерывание .

В случае обращения за операндом смещение в сегменте формируется микропроцессором по режиму адресации операнда, заданному в команде. Смещение в сегменте кода извлекается из регистра - указателя команд EIP .

Сумма извлеченного из дескриптора начального адреса сегмента и сформированного смещения в сегменте дает линейный адрес (ЛА).

Если в микропроцессоре используется только сегментное представление адресного пространства, то полученный линейный адрес является также и физическим.

Если помимо сегментного используется и страничный механизм организации памяти , то линейный адрес представляется в виде двух полей: старшие разряды содержат номер виртуальной страницы , а младшие смещение в странице. Преобразование номера виртуальной страницы в номер физической проводится с помощью специальных системных таблиц: каталога таблиц страниц (КТС) и таблиц страниц (ТС). Положение каталога таблиц страниц в памяти определяется системным регистром CR3. Физический адрес вычисляется как сумма полученного из таблицы страниц адреса физической страницы и смещения в странице, полученного из линейного адреса.

Рассмотрим теперь все этапы преобразования логического адреса в физический более подробно.

Евдокимов А.А., Майстренко Н.В., Майстренко А.В.

4.1. ПОНЯТИЕ АДРЕСНОГО ПРОСТРАНСТВА

Для одновременного размещения в памяти нескольких программ и для избегания ситуаций возникновения взаимных помех необходимо решить задачи по защите и перемещению.

Самым подходящим решением оказалась абстракция адресного пространства. Аналогично тому как абстракция процесса создает для своего запуска и выполнения виртуальный процессор, абстракция адресного пространства создает некую абстрактную память для существующих в системе приложений. Адресное пространство представляется в виде набора адресов, используемых процессом для обращения к ресурсу памяти. Каждый процесс имеет собственное адресное пространство, которое не зависит от адресных пространств других процессов, кроме случаев, когда процессам необходимо совместно использовать свои адресные пространства.

Чтобы понять, как реализовано адресное пространство, то есть как достигается соответствие адресов в памяти, выделяемых для приложений, и физической памяти, для начала рассмотрим самое простое решение, называемое динамическим перераспределением памяти. Адресное пространство процесса в данном решении проецируется на различные части физической памяти. Центральный процессор получает два специальных аппаратных регистра, называемых базовым и ограничительным регистрами. Используя данные регистры, приложения помещаются в последовательно расположенные незанятые области памяти, причем в процессе загрузки адреса не подвергаются изменению. В момент запуска процесса базовый регистр центрального процессора получает физический адрес, с которого размещается в памяти запущенная программа, а ограничительный регистр получает значение длины программы.

Если выполняющийся процесс обращается к памяти для извлечения команды или записи некоторых данных, центральный процессор прибавляет к полученному от процесса адресу значение из базового регистра, а затем выставляет результат на шину памяти. Также центральный процессор сравнивает полученный адрес со значением ограничительного регистра. В случае превышения данного значения будет сгенерирован отказ и доступ к памяти будет прерван.

Таким образом, использование специальных регистров центрального процессора является достаточно простым способом предоставления собственного адресного пространства каждому отдельному процессу, так как перед обращением к физической памяти всего лишь необходимо выполнить операцию сложения значения адреса, сгенерированного процессом, и значения базового регистра. Операционная система также может выполнять защиту базового и ограничительного регистров. При такой защите значения специальных регистров может изменить только сама система.

Необходимость использования операций сложения и сравнения при каждом обращении процесса к физической памяти является главным недостатком применения специальных регистров. Если операция сравнения может выполняться достаточно быстро, то операция сложения выполняется слишком медленно, так как вспомогательный сигнал переноса требует дополнительных затрат времени.

Читайте также: