Инициируется не процессором а внешним устройством

Обновлено: 06.07.2024

В МПС используются два основных способа организации передачи данных между памятью и периферийными устройствами: программно управляемая передача и прямой доступ к памяти ПДП ( Direct Memory Access - DMA ).

Программно управляемая передача данных осуществляется при непосредственном участии и под управлением процессора. Например, при пересылке блока данных из внешнего устройства в оперативную память процессор должен выполнить следующую последовательность шагов:

- сформировать начальный адрес области обмена ОП;

- занести длину передаваемого массива данных в один из своих внутренних регистров, который будет играть роль счетчика;

- выдать команду чтения информации из ВУ; при этом на шину адреса из МП выдается адрес ВУ, на шину управления - сигнал чтения данных из ВУ, а считанные данные заносятся во внутренний регистр МП;

- выдать команду записи информации в ОП; при этом на шину адреса из МП выдается адрес ячейки оперативной памяти, на шину управления - сигнал записи данных в ОП, а на шину данных выставляются данные из регистра МП, в который они были помещены при чтении из ВУ;

- модифицировать регистр, содержащий адрес оперативной памяти;

- уменьшить счетчик длины массива на длину переданных данных;

- если переданы не все данные, то повторить шаги 3-6, в противном случае закончить обмен.

Как мы видим, программно управляемый обмен ведет к нерациональному использованию мощности микропроцессора, который вынужден выполнять большое количество относительно простых операций, приостанавливая работу над основной программой. При этом действия, связанные с обращением к оперативной памяти и к внешнему устройству, обычно требуют удлиненного цикла работы микропроцессора, что приводит к еще более существенным потерям производительности.

Альтернативой программно управляемому обмену служит прямой доступ к памяти - способ быстродействующего подключения внешнего устройства, при котором оно обращается к оперативной памяти, не прерывая работы процессора. Такой обмен происходит под управлением отдельного устройства - контроллера прямого доступа к памяти (КПДП).

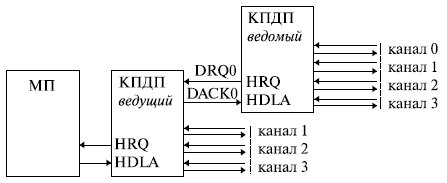

Схема включения КПДП в состав микропроцессорной системы представлена на рис. 8.4.

Рис. 8.4. Структура МПС с контроллером прямого доступа к памяти

Перед началом работы контроллер ПДП необходимо инициализировать: занести начальный адрес области ОП, с которой производится обмен, и длину передаваемого массива данных. В дальнейшем по сигналу запроса прямого доступа контроллер фактически выполняет все те действия, которые обеспечивал микропроцессор при программно управляемой передаче.

Последовательность действий КПДП при запросе на прямой доступ к памяти со стороны внешнего устройства следующая:

- Принять запрос на ПДП (сигнал DRQ ) от ВУ.

- Сформировать запрос к МП на захват шин (сигнал HRQ ).

- Принять сигнал от МП ( HLDA ), подтверждающий факт перевода микропроцессором своих шин в третье состояние.

- Сформировать сигнал, сообщающий устройству ввода-вывода о начале выполнения циклов прямого доступа к памяти ( DACK ).

- Сформировать на шине адреса компьютера адрес ячейки памяти, предназначенной для обмена.

- Выработать сигналы, обеспечивающие управление обменом ( IOR , MW для передачи данных из ВУ в оперативную память и IOW , MR для передачи данных из оперативной памяти в ВУ).

- Уменьшить значение в счетчике данных на длину переданных данных.

- Проверить условие окончания сеанса прямого доступа (обнуление счетчика данных или снятие сигнала запроса на ПДП ). Если условие окончания не выполнено, то изменить адрес в регистре текущего адреса на длину переданных данных и повторить шаги 5-8.

Прямой доступ к памяти позволяет осуществлять обмен данными между внешним устройством и оперативной памятью параллельно с выполнением процессором программы.

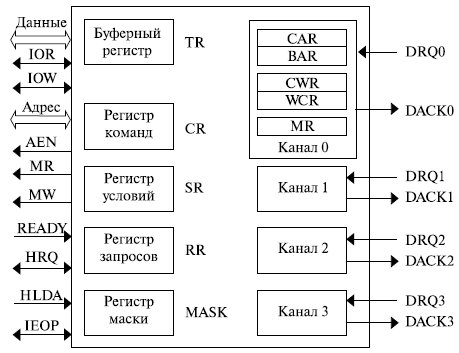

Структура КПДП представлена на рис. 8.5.

Рис. 8.5. Структура контроллера прямого доступа к памяти

Контроллер состоит из 4 идентичных каналов, позволяющих подключить к системе до четырех устройств, работающих в режиме ПДП .

В состав каждого канала входят следующие регистры:

- MR ( Mode Register ) - регистр режима. Определяет следующие параметры передачи:

- порядок изменения (увеличения или уменьшения) адреса ОП при передаче;

- возможность автоинициализации;

- режим обслуживания:

- одиночная передача (контроллер возвращает магистраль процессору после каждого цикла ПДП );

- блочная передача (контроллер владеет магистралью в течение передачи всего массива);

- по требованию (окончание передачи определяется снятием сигнала DRQ или подачей сигнала IEOP на внешний вход КПДП);

- каскадирование;

Значения в регистрах BAR и WCR устанавливаются при инициализации и в ходе циклов ПДП не меняются. В регистры CAR и CWR в начале выполнения ПДП заносятся значения из регистров BAR и WCR соответственно. При выполнении ПДП эти регистры изменяются.

Управляющие регистры, общие для всего контроллера:

- CR ( Command Register ) - регистр команд - определяет:

- режим память-память или обычный. В режиме память-память осуществляется обмен по схеме ПДП между двумя областями ОП (только для каналов 0 и 1) с использованием буферного регистра TR ( Temporary Register );

- запрет/разрешение ПДП ;

- порядок изменения приоритетов каналов:

- фиксированный приоритет;

- циклическое изменение приоритета после обработки запроса на ПДП по одному из каналов;

- явное указание наиболее приоритетного канала;

- уровень сигналов DRQ и DACK (настройка на активный уровень сигналов под особенности работы внешних устройств);

Во избежание ложных срабатываний внешних устройств, не использующих в данный момент режим прямого доступа, контроллер ПДП во время режима ПДП вырабатывает сигнал AEN , который блокирует работу остальных внешних устройств:

![AEN=\begin</p>

\mbox\\ \mbox \end]()

Для увеличения количества внешних устройств, которые могут быть подключены к микропроцессору в режиме ПДП , используется каскадное включение КПДП (рис. 8.6).

При этом ведомый КПДП подключается к одному из каналов ведущего контроллера по схеме подключения внешнего устройства, а непосредственно с микропроцессором связывается только ведущий контроллер . В стандартной конфигурации персональной ЭВМ применяются два КПДП (ведущий и ведомый), которые позволяют подключить до 7 внешних устройств, причем 2 канала закреплены за накопителями на жестком и гибком

![Каскадное включение контроллеров прямого доступа к памяти]()

Рис. 8.6. Каскадное включение контроллеров прямого доступа к памятидисках. В максимальной конфигурации при использовании ведущего и 4 ведомых КПДП, подключенных к каждому из каналов ведущего, к МП можно подключить до 16 внешних устройств, работающих в режиме ПДП .

Способы обмена информацией в микропроцессорной системе

В ЭВМ применяются три режима ввода/вывода:

- программно-управляемый ВВ (называемый также программным или нефорсированным ВВ);

- ВВ по прерываниям (форсированный ВВ);

- прямой доступ к памяти

Первый из них характеризуется тем, что инициирование и управление ВВ осуществляется программой, выполняемой процессором, а внешние устройства играют сравнительно пассивную роль и сигнализируют только о своем состоянии, в частности, о готовности к операциям ввода/вывода.

Во втором режиме ВВ инициируется не процессором, а внешним устройством, генерирующим специальный сигнал прерывания. Реагируя на этот сигнал готовности устройства к передаче данных, процессор передает управление подпрограмме обслуживания устройства, вызвавшего прерывание. Действия, выполняемые этой подпрограммой, определяются пользователем, а непосредственными операциями ВВ управляет процессор.

В режиме прямого доступа к памяти, который используется, когда пропускной способности процессора недостаточно, действия процессора приостанавливаются, он отключается от системной шины и не участвует в передачах данных между основной памятью и быстродействующим ВУ.

Во всех вышеуказанных случаях основные действия, выполняемые на системной магистрали ЭВМ, подчиняются двум основным принципам.

- В процессе взаимодействия любых двух устройств ЭВМ одно из них обязательно выполняет активную, управляющую роль и является задатчиком, второе оказывается управляемым, исполнителем. Чаще всего задатчиком является процессор.

- Другим важным принципом, заложенным в структуру интерфейса, является принцип квитирования (запроса - ответа): каждый управляющий сигнал, посланный задатчиком, подтверждается сигналом исполнителя. При отсутствии ответного сигнала исполнителя в течение заданного интервала времени формируется так называемый тайм-аут, задатчик фиксирует ошибку обмена и прекращает данную операцию.

Данный режим характеризуется тем, что все действия по вводу/выводу реализуются командами прикладной программы. Наиболее простыми эти действия оказываются для "всегда готовых" внешних устройств, например индикатора на светодиодах. При необходимости ВВ в соответствующем месте программы используются команды IN или OUT. Такая передача данных называется синхронным или безусловным ВВ.

Однако для большинства ВУ до выполнения операций ВВ надо убедиться в их готовности к обмену, т.е. ВВ является асинхронным. Общее состояние устройства характеризуется флагом готовности READY, называемым также флагом готовности/занятости (READY/BUSY). Иногда состояния готовности и занятости идентифицируются отдельными флагами READY и BUSY, входящими в слово состояния устройства.

Процессор проверяет флаг готовности с помощью одной или нескольких команд. Если флаг установлен, то инициируются собственно ввод или вывод одного или нескольких слов данных. Когда же флаг сброшен, процессор выполняет цикл из 2-3 команд с повторной проверкой флага READY до тех пор, пока устройство не будет готово к операциям ВВ (см. рис.). Данный цикл называется циклом ожидания готовности ВУ и реализуется в различных процессорах по разному.

![]()

Цикл программного ожидания готовности внешнего устройства

Основной недостаток программного ВВ связан с непроизводительными потерями времени процессора в циклах ожидания. К достоинствам следует отнести простоту его реализации, не требующей дополнительных аппаратных средств.

![Способы обмена данными]()

Основные способы обмена данными.

Между микропроцессорной системой (МС) и внешним устройством (ВУ) происходит обмен полезной информацией в виде слов данных (

) и служебной информацией в виде управляющих слов (

) и слов состояния (

). Служебная информация может занимать значительный объем. Поэтому в общем случае для обмена информацией отводится ряд портов ввода/вывода (ВВ), образующих пространство доступа к внешнему устройству (ВУ). Ввод и вывод всегда рассматриваются по отношению к микропроцессору. Обмен информацией между процессором и ВУ осуществляется по определенным правилам. Совокупность правил, называемых протоколом обмена, является основой для составления драйвера ВУ. Драйвер представляет собой набор подпрограмм, обслуживающих обмен ВУ с микропроцессором.

Существуют три способа обмена данными: программно управляемый обмен, обмен с прерыванием программы и обмен по каналу прямого доступа к памяти. Рассмотрим в общих чертах особенности каждого способа обмена.

Программно–управляемый обмен данными.

Обмен инициируется и выполняется процессором с помощью:

● специальных команд ввода–вывода,

при этом в формате команды должен содержаться код выполняемой операции и номер выбираемого порта ВУ;

● команд обращения к

ОЗУ, при этом каждый порт ВУ рассматривается как адрес, отличный от адресов других ячеек.

С точки зрения использования вспомогательных сигналов различают прямой и условный обмен.

Прямым, или безусловным,

вводом–выводом называется такая процедура, при которой для активизации обмена не требуется никаких условий и вспомогательных сигналов. Прямой ввод/вывод возможен только с внешними устройствами, которые всегда готовы к обмену. Он является составной частью более сложных протоколов обмена.

вводом–выводом называется такая процедура, при которой активизация обмена возможна при выполнении условия готовности к обмену ВУ.

Большинство ВУ работает асинхронно по отношению к процессору. При асинхронном обмене информацией важной задачей является проверка готовности ВУ. Поэтому ВУ должно иметь аппаратные средства для выработки информации о своем внутреннем состоянии. Микропроцессор считывает эту информацию, передает ее в аккумулятор, анализирует и на основе анализа принимает решение о готовности ВУ. При отсутствии готовности ВУ процессор переходит в состояние ожидания. Если обнаружено состояние готовности, то выполняются операции передачи данных. Таким способом достигается сопряжение во времени работы процессора и таких устройств, которые по быстродействию уступают процессору.

![рис. 3.2.1]()

Таким образом, условный ввод/вывод применяется для обмена с низкоскоростными внешними устройствами и сопровождается сигналом готовности ГтВУ, генерируемым ВУ. Сигнал готовности ГтВУ вводится в процессор в составе слова состояния и информирует его о готовности ВУ к обмену. После завершения операции обмена сигнал готовности ГтВУ должен быть снят и выставлен перед новой операцией. Для этого процессор информирует ВУ об окончании операции с помощью сигнала подтверждения Пт.

На рис. 3.2.1 приведены диаграммы условного ввода/вывода с помощью контроллера обмена. В этом случае могут быть также использованы сигналы готовности Гт контроллера и подтверждения ПтВУ внешнего устройства.

При вводе (рис. 3.2.1, а) процессы протекают в следующей последовательности:

● если сигнал подтверждения микропроцессора (контроллера) Пт = 0, ВУ выставляет на шине ШВУ новые данные и сигнал готовности ГтВУ = 1;

● так как ГтВУ = 1, процессор дает команду на ввод данных, и данные по ШД поступают в аккумулятор;

● процессор через контроллер выставляет сигнал подтверждения Пт = 1, извещая ВУ о том, что данные введены;

● при Пт = 1 ВУ снимает сигнал готовности (ГтВУ =0);

● при ГтВУ = 0 процессор снимает сигнал подтверждения (Пт = 0).

При выводе данных (рис. 3.2.1, б) процессы протекают в следующей последовательности:

● если сигнал готовности контроллера Гт = 0, ВУ осуществляет сброс сигнала подтверждения (ПтВУ = 0), после чего процессор на ШД выставляет новые данные;

● при сигнале подтверждения ПтВУ = 0 контроллер устанавливает сигнал готовности Гт = 1;

● данные по ШВУ выводятся в ВУ;

● при Гт = 1 ВУ устанавливает сигнал подтверждения (ПтВУ =1);

![рис. 3.2.2]()

● при ПтВУ = 1 процессор снимает ранее установленный сигнал готовности (Гт = 0).

Рассмотренный протокол обмена называется квитированием.

Возможны два вида условного обмена: с занятием цикла и совмещенного. При обмене с занятием цикла (рис. 3.2.2, а) в случае неготовности ВУ микропроцессор находится в режиме ожидания; при совмещенном обмене (рис. 3.2.2, б) после опроса ВУ микропроцессор возвращается к выполнению основной программы.

По способу кодирования различают обмен данными в параллельном и последовательном коде.

Необходимость передачи данных в последовательном коде обусловлена двумя факторами:

● наличием устройства (например, клавиатура, дисплей, телетайп), принцип работы которого базируется на использовании последовательного кода;

● удалением внешнего устройства от процессора на значительное расстояние. Дело в том, между отдельными проводниками соединительной линии между источником и приемником информации существует емкостная связь. С увеличением длины соединительной линии растет емкость между ее отдельными проводниками. Поэтому при передаче импульсных сигналов по одному проводнику в других проводниках наводятся помехи, уровень которых может быть соизмеримым с уровнем полезных сигналов.

В этих условиях обмен информацией между процессором и внешним устройством должен сопровождаться преобразованием параллельного кода в последовательный код при выводе данных и последовательного кода в параллельный — при вводе данных. Указанные функции возлагаются на контроллер обмена, который обычно выполняется в виде интегральной схемы.

К достоинствам программно–управляемого обмена данных относится его простота, к недостаткам — бесполезная трата времени на ожидание готовности ВУ и невозможность обеспечения своевременной реакции на внезапно возникшую потребность ВУ в обмене информацией.

Обмен с прерыванием программы.

При этом способе инициатором обмена является внешнее устройство, которое подает специальный сигнал ЗАПРОС ПРЕРЫВАНИЯ на соответствующий вход процессора. После выполнения текущей микрокоманды процессор прекращает выполнение основной программы, вырабатывает сигнал ПОДТВЕРЖДЕНИЕ ПРЕРЫВАНИЯ и переходит к подпрограмме обработки прерывания, расположенной в фиксированной области памяти. После выполнения этой подпрограммы происходит возврат к основной программе.

Обмен данными с помощью прямого доступа к памяти.

По этому способу используется канал прямого доступа к памяти (ПДП), по которому массивы данных передаются непосредственно между внешним устройством (ВУ) и ОЗУ, минуя процессор. Это позволяет достичь наибольшей скорости передачи, но требует определенных аппаратных затрат для организации канала. Аналогично случаю обмена по прерыванию ВУ посылает в процессор сигнал запроса на прямой доступ. После отправления сигнала подтверждения процессор прекращает работу по выполнению текущей программы, отключает свои буферные регистры от шин адреса и данных, а также прекращает выработку управляющих сигналов. Таким образом, процессор как бы замирает до окончания процедуры ПДП, чем этот режим и отличается от режима обработки прерывания. Все функции адресации, передачи данных и управления выполняет контроллер ПДП, содержащий счетчик адреса, счетчик числа слов в массиве, а также ряд триггеров и логических схем, которые внесены в блок управления.

До начала работы канала ПДП в счетчик адреса заносится адрес ячейки ОЗУ, с которой начинается массив данных, и в счетчик слов (в прямом или дополнительном коде) — число слов в массиве. При передаче каждого слова содержимое этих счетчиков изменяется на единицу и обмен данными производится автоматически, пока не будет передан весь массив слов.

В микропроцессорных системах встроены (или предусматриваются) интерфейсные схемы для организации ввода/вывода.

В состав микропроцессорной системы помимо микропроцессора может входить различное число других устройств. При этом должна обеспечиваться возможность связи между этими устройствами и обмена информацией между ними с необходимой скоростью. Микро ЭВМ взаимодействуют с внешней средой с помощью периферийных устройств. Для включения МП в информационную систему необходимо установить единые правила обмена информацией и требования к средствам сопряжения МП с остальными устройствами системы. Эти цели реализует унифицированный интерфейс. Под интерфейсом понимают совокупность технических средств и правил, устанавливающих единые принципы взаимодействия устройств системы (протокол обмена). В состав интерфейса входят:

- аппаратные средства (разъемы, линии связи, согласующие устройства)

- номенклатуры и характер связей

- описание электрофизических параметров сигналов.

Для интерфейса характерно выполнение четырех функций:

1. буферирование информации (необходимо для согласования и синхронизации процессора и периферийных устройств)

2. дешифрирование адреса (необходимо для выбора конкретного устройства в системе)

3. дешифрирование команды (производится для устройств, которые кроме передачи данных выполняют и другие функции: переключение диапазона АЦП, перемотка ленты, перемещение головок дисковых накопителей и т.д.),

4. синхронизация и управление процессом обмена (требуются при реализации любой из перечисленных функций)

В МП системах наиболее часто используется магистральный интерфейс (интерфейсы с разветвленными связями дороже и сложнее в реализации). Единая информационная магистраль связывает между собой все устройства МП системы и функционально состоит из информационных шин адреса, данных, сигналов управления (команд). Две или все три шины могут быть объединены в одну группу шин при реализации обмена информацией в режиме разделения времени (мультиплексированная магистраль). Шина адреса в простых МП системах является однонаправленной, т.к. в простейших системах только МП может вырабатывать сигналы кода адреса, а остальные устройства, подключенные к ША непрерывно выполняют операцию приема и опознавания кода адреса. В сложных или мультиплексорных системах ША может быть двунаправленной для части или всех ФБ системы.

Часть устройств системы по ШД может работать в двунаправленном режиме (МП, ОЗУ). Часть устройств может работать только на прием информации (устройство печати), другие только передавать информацию (ПЗУ). Разрядность ШД определяется разрядностью МП.

Организация взаимодействия и обмена информацией между устройствами (модулями) МП - системы должна обеспечивать:

- включение в систему новых устройств без каких-либо переделок в аппаратуре, а лишь путем добавления программ, обслуживающих эти устройства, возможность реализовать микропроцессорные системы с различной конфигурацией;

- возможность эффективной реализации обмена информацией в системе, содержащей устройства со значительно различающимися скоростями передачи данных, причем в условиях, когда запросы на операции ввода – вывода поступают в произвольные моменты времени (асинхронно относительно программы, выполняемой процессором) и имеют разную срочность исполнения;

- возможность параллельного во времени выполнения процессором программы, а периферийными устройствами операций ввода – вывода;

- унификацию программирования операций ввода – вывода с исключением необходимости учета особенностей того или иного периферийного устройства.

Указанные требования реализуются на основе следующих архитектурных решений, характерных для построения микропроцессорных средств.

Используется магистрально-модульная организация микропроцессорных систем – отдельные микропроцессорные средства выполняются в виде конструктивно законченных модулей (БИС), и эти модули объединяются в систему посредством общих шин (магистралей). Особенностью архитектуры микропроцессорных средств является связь системы прерывания с шинами и процедурами работы интерфейса.

Магистрально-модульная структура МП - системы.

![]()

Важной особенностью организации обмена информацией в микропроцессорных систем является использование специализированных интерфейсных БИС (контроллер прямого доступа, контроллер прерываний, программируемый периферийный адаптер, программируемый связной адаптер, программируемый таймер), позволяющих в значительной степени освобождать процессор от управления операциями ввода – вывода и выполнения вспомогательных процедур преобразования форматов данных, подсчета передаваемых байт и др. Программная настраиваемость интерфейсных БИС обеспечивает построение гибких и эффективных микропроцессорных систем управления и обработки данных.

В МП- системах используются три способа организации передачи информации: 1) программно-управляемая передача, инициируемая процессором; 2) программно-управляемая передача, инициируемая запросом прерывания от периферийного устройства; 3) прямой доступ к памяти (ПДП или DMA).

При программно-управляемой передачеобмен данными происходит через регистры процессора и производится соответствующими командами программы процессора. При первом способе передача инициируется самим процессором (точнее соответствующей командой в его программе), а при втором – запросом прерывания от периферийного устройства. Процедура передачи по прерыванию имеет ряд особенностей. При программно-управляемой передаче данных микропроцессор на все время этой операции отвлекается от выполнения основной программы, что ведет к снижению производительности МП – системы. Особенно это становится заметным при пересылке блока данных, когда микропроцессор для каждого передаваемого байта должен выполнить много команд, чтобы обеспечить буферизацию данных, подсчет количества переданных байт, формирование адресов в памяти и т.д. Более того, скорость передачи данных через микропроцессор может оказаться недостаточной для работы с высокоскоростными ПУ.

Для быстрого ввода – вывода блоков данных и разгрузки микропроцессоров от управления операциями ввода – вывода используют прямой доступ к памяти.

Прямым доступом к памяти (ПДП) называется способ обмена данными, обеспечивающий автономно от микропроцессора (ядром) установление связи и передачу данных между ОЗУ и внешним устройством (ВУ). Прямой доступ к памяти повышает предельную скорость ввода – вывода информации и делает МП- систему более приспособленной для работы в системах реального времени. Прямым доступом к памяти управляет контроллер ПДП, выполняющий следующие функции: управление инициируемой процессором или ВУ передачей данных между ОЗУ и ВУ; задание размера блока данных, который подлежит передаче, и области памяти, используемой при передаче; формирование адресов ячеек ОЗУ, участвующих в передаче; подсчет числа байт, передаваемых через интерфейс, определение момента завершения заданной операции ввода – вывода.

Читайте также: