Какой регистр процессора 8086 8088 определяет адрес ввода вывода

Обновлено: 07.07.2024

Описание микропроцессоров фирмы Intel мы начнем с процессоров i8086/8088. Именно заложенные в них архитектурные решения во многом определили архитектуру последующих моделей семейства Intel, поддерживающих совместимость с более ранними моделями. В том числе и с недостатками и ограничениями предыдущих моделей.

Одна из характерных особенностей процессоров i8086/8088 — принцип сегментирования памяти. То есть вся память представляется не в виде непрерывного пространства, а в виде нескольких кусков — сегментов заданного размера (по 64 Кбайта), положение которых в пространстве памяти можно программно изменять. Об этом уже говорилось в разделе 3.1.2 (см. рис. 3.5 и 3.6).

Процессор 8086/8088 имеет 14 регистров разрядностью по 16 бит. Об их назначении также уже говорилось в разделе 3.2.

Для ускорения выборки команд из памяти в процессоре 8086 предусмотрен внутренний 6-байтный конвейер (в процессоре 8088 — 4-байтный). Конвейер заполняется читаемыми из памяти командами во время выполнения предыдущей команды и сбрасывается (считается пустым) при выполнении любой команды перехода (даже если это команда перехода на следующий адрес).

Система команд процессора включает в себя 133 команды, поддерживающие 24 метода адресации операндов. Такое большое число команд может рассматриваться как достоинство (можно гибко выбирать команду, оптимально подходящую для каждого конкретного случая), но оно же заметно усложняет структуру процессора.

Каждая команда содержит 1, 2 или 4 байта кода команды, за которыми могут следовать 1, 2 или 4 байта операнда.

В процессоре предусмотрены программные и аппаратные прерывания, разделение внешней шины с другими процессорами или с контроллером прямого доступа к памяти, а также возможность подключения математического сопроцессора i8087, существенно увеличивающего производительность вычислений.

При старте процессора (по внешнему сигналу RESET) он переходит в адрес памяти FFFF0 и начинает выполнение программы, которая размещается начиная с этого адреса.

Процессор может обрабатывать 256 типов прерываний: внешних (аппаратных), программных и внутренних. Векторы прерываний представляют собой двойное слово (два слова по 16 разрядов), определяющее сегмент и смещение начального адреса программы обработки прерываний. Для векторов прерываний отведена область памяти с адресами 00000…003FF. Внутренние прерывания вырабатываются при особых ситуациях:

- прерывание 0 соответствует переполнению при делении на нуль;

- прерывание 1 вырабатывается после каждой команды при установленном флаге трассировки TF в регистре состояния процессора (см. раздел 3.2);

- прерывание 4 вырабатывается по специальной команде INTO, если установлен флаг переполнения OF в регистре состояния процессора (это условное прерывание по переполнению).

Особое место занимает немаскируемое прерывание NMI (Non-Masked Interrupt), которое вырабатывается при поступлении внешнего сигнала NMI и не зависит от состояния флага разрешения аппаратных прерываний IF. В компьютере оно используется для контроля четности памяти, контроля корректности обмена с памятью и устройствами ввода/вывода, а также для обработки так называемых исключений, то есть особых условий, возникающих в процессе работы. Немаскируемым оно называется именно потому, что его нельзя запретить.

Важная отличительная особенность процессора — разделение операций обмена с устройствами ввода/вывода и с памятью. Для обмена с устройствами ввода/вывода используются как отдельные команды ввода и вывода, так и специальные управляющие сигналы на шине управления. Адреса и данные как при обмене с памятью, так и при обмене с устройствами ввода/вывода передаются по одним и тем же шинам. Но если для обмена с памятью используются все 20 разрядов шины адреса (адресуется 1 Мбайт — адреса 00000 . FFFFF), то в циклах обмена с устройствами ввода/вывода — только 16 разрядов шины адреса (адресуется 64 Кбайта — адреса 00000 . 0FFFF). Такой подход имеет как свои преимущества (например, упрощение реализации прямого доступа к памяти), так и недостатки (усложнение системы команд, увеличение количества управляющих сигналов).

Микропроцессоры i8086/8088 выполнены в виде интегральной микросхемы в 40-выводном корпусе. Отличие в назначении выводов микросхемы между ними только одно: адрес в процессоре 8088 не мультиплексирован с данными (передается по отдельным линиям), а в процессоре 8086 — мультиплексирован.

Процессор работает от одного источника питания напряжением +5В и требует внешнего тактирующего сигнала с частотой, определяемой номером модели (от 4,77 МГц до 10 МГц).

Специальный управляющий сигнал MN/MX определяет минимальный или максимальный режим работы процессора. В минимальном режиме процессор сам вырабатывает сигналы управления для внешней шины. Этот режим используется для построения простейших систем. Для работы в составе компьютера применяется максимальный режим, при котором сигналы управления внешней шиной вырабатываются специальной микросхемой контроллера шины i8288.

Intel 8086 – один из самых влиятельных из когда-либо созданных компьютерных чипов. Он создал архитектуру x86, доминирующую в современных настольных и серверных компьютерах. Я занимался реверс-инжинирингом 8086 на основе фотографий кристаллов, и в данной статье я опишу реализацию регистрового файла (набора регистров).

Кристалл 8086. Отмечено место хранения регистров. Верхние регистры используются блоком интерфейса шины для доступа к памяти, а нижние регистры общего назначения используются исполнительным блоком. Буфер команд – это 6-байтная очередь, состоящая из заранее запрошенных команд.

На фото дано изображение процессора 8086 под микроскопом. Виден металлический слой сверху чипа, под которым прячется кремний. Расположенные по внешнему краю соединительные провода соединяют площадки на кристалле с 40 внешними контактами чипа.

Рамкой обведены пятнадцать 16-битовых регистров 8086 и шесть байтов очереди предварительного запроса команд (предвыборки кода). Регистры занимают значительную часть кристалла, хотя в сумме их наберётся всего на 36 байт. Из-за ограничений по площади у первых микропроцессоров было относительно небольшое количество регистров. Для сравнения, у современных чипов процессоров есть килобайты регистров и мегабайты кэшей.

8086 был одним из самых ранних микропроцессоров, реализовавших предвыборку кода, однако у Motorola 68000 (1979) немного раньше появился буфер предвыборки на 4 байта. В мейнфреймах предвыборка существовала у IBM Stretch (1961), CDC 6600 (1964) и IBM System/360 Model 91 (1966).

Количество регистров у современного процессора подсчитать сложно. Единственное точное число, найденное мною, содержалось в книге "Анатомия высокоскоростного микропроцессора" (1997), подробно описывающей процессор AMD K6. Из-за переименования регистров у современных процессоров физических регистров гораздо больше, чем архитектурных (тех, что видны программисту), а количество физических регистров в документации не указывается. У K6, кроме восьми регистров х86 общего назначения, было 16 микроархитектурных рабочих регистров для переименования.

У процессоров с поддержкой AVX-512 есть 32 512-битовых регистра, то есть для одной этой функции зарезервировано 2 кБ регистров. В таких случаях размер регистров подсчитать ещё сложнее. Что до размера кэша, то у передовых процессоров его объём доходит до 77 МБ.

Как регистры реализуются в кремнии

Начну с описания того, как 8086 создаётся из N-МОП транзисторов. Затем объясню, как делается инвертор, как при помощи инверторов хранятся одиночные биты, и как делается регистр.

8086, как и другие чипы той эпохи, создавались на основе транзисторов типа N-МОП. Эти чипы состояли из кремниевой подложки, в которую при помощи диффузии внедряли примеси из мышьяка или бора, формировавшие транзисторы. Находящиеся над кремнием проводники из поликремния формировали вентили транзисторов и соединяли все компоненты друг с другом. Находившийся ещё выше металлический слой содержал дополнительные проводники. Для сравнения, современные процессоры используют технологию КМОП, комбинирующую N-МОП и P-МОП транзисторы, и содержат множество металлических слоёв.

На схеме ниже показан инвертор, состоящий из N-МОП транзистора и резистора. При низком входном напряжении транзистор выключен, поэтому подтягивающий резистор подтягивает выход вверх. При высоком входном напряжении транзистор включается, соединяет землю и выход, подтягивая выход вниз. Таким образом входящий сигнал инвертируется.

На самом деле, подтягивающий резистор в вентиле N-МОП представляет собой транзистор особого рода. Работающий в режиме обеднения транзистор ведёт себя, как резистор, будучи при этом более компактным и эффективным.

На схеме показано, как из транзистора и резистора получается инвертор. На фото показана реализация на чипе. Металлический слой удалён, чтобы было видно кремний и поликремний.

На фото выше видно, как физически сделан инвертор у 8086. Розоватые участки – это кремний с примесями, делающими его токопроводящим, а линии медного цвета – это поликремний сверху. Транзистор появляется там, где поликремний пересекается с кремнием. Поликремний формирует вентиль транзистора, а участки кремния с двух сторон дают исток и сток. Большой прямоугольник поликремния формирует подтягивающий резистор между +5 В и выходом. Таким образом, схема чипа совпадает со схемой инвертора. Подобные цепи можно рассмотреть под микроскопом и подвергнуть реверс-инжинирингу.

Строительный блок регистра – два инвертора в цепи обратной связи, хранящих один бит (см. ниже). Если на верхнем проводнике 0, правый инвертор выдаст 1 на нижний проводник. Затем левый инвертор выдаст 0 на верхний проводник, завершая цикл. Таким образом цепь оказывается стабильной и «помнит» 0. И наоборот, если на верхнем проводнике 1, она превратится в 0 на нижнем проводнике, и обратно в 1 на верхнем. В итоге цепь может хранить 0 или 1, формируя однобитную память.

У 8086 два спаренных инвертора хранят в регистре один бит. Схема стабильно находится в состоянии 0 или 1.

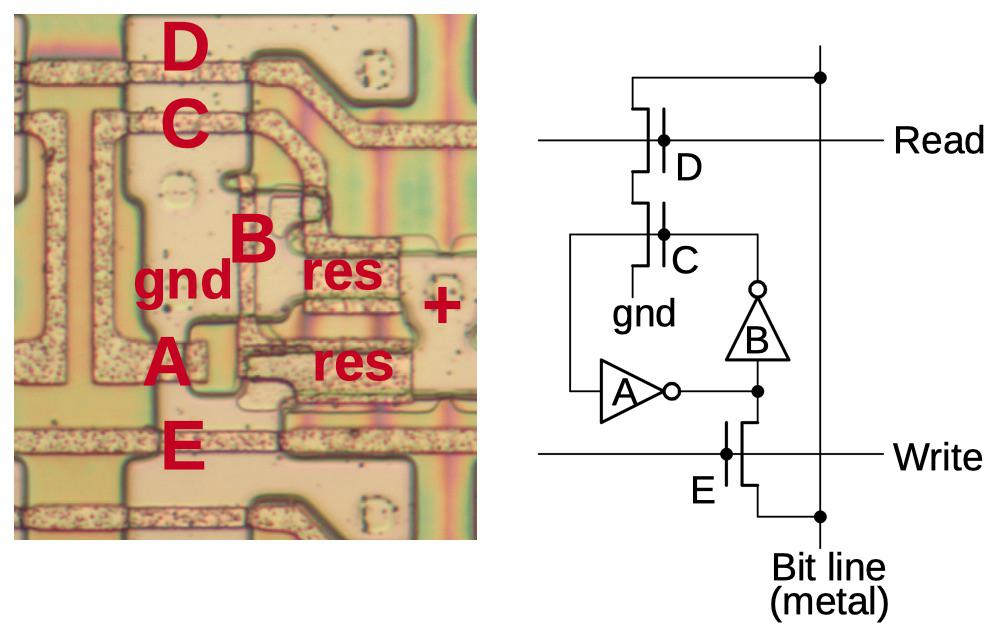

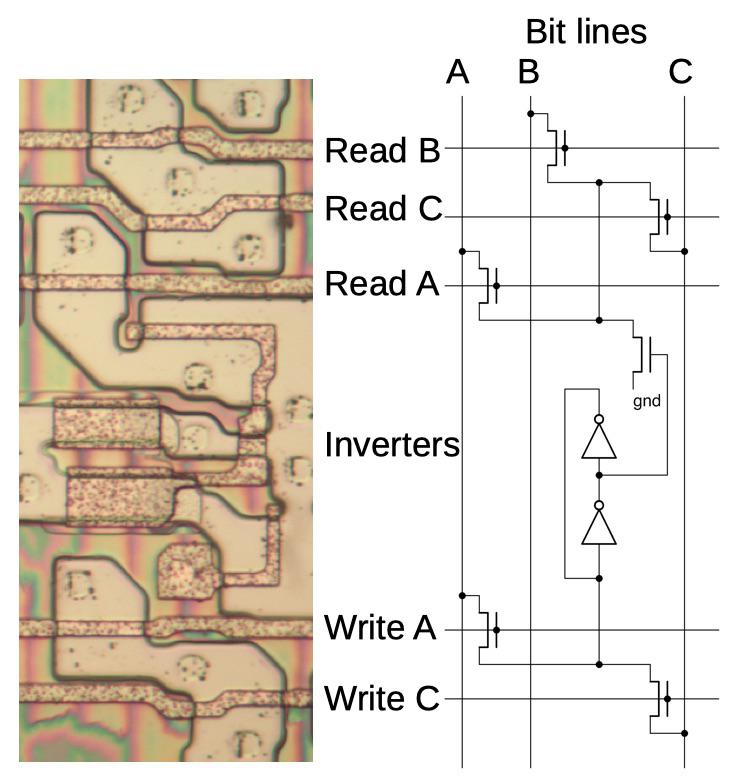

К паре инверторов добавляются три транзистора, чтобы получилась пригодная для использования ячейка регистра. Один транзистор выбирает ячейку для чтения, второй выбирает ячейку для записи, третий усиливает сигнал при чтении. В центре схемы ниже два инвертора хранят бит. Для чтения бита ток подаётся на красную шину. Это соединяет выход инвертора с разрядной шиной через усиливающий транзистор. Для записи бита ток подаётся на красную шину, соединяющую разрядную шину с инверторами. Подавая высокотоковые сигналы 0 или 1 на разрядную шину (и, соответственно, на хранящийся бит), мы заставляем инверторы переключаться на нужное значение. Отметьте, что разрядная шина используется и для чтения, и для записи.

В других процессорах используются несколько другие ячейки для хранения регистров. 6502 использует дополнительный транзистор в цепи обратной связи инвертора, чтобы разбивать цепь при записи нового значения. Z80 пишет одновременно в оба инвертора, что «облегчает» изменение, однако требует наличия двух проводников для записи. У 8086 есть усиливающий транзистор в каждой ячейке регистра для чтения, а другие процессоры считывают выходной сигнал с обоих инверторов и используют внешний дифференциальный усилитель для усиления сигнала. Базовая ячейка регистра 8086 состоит из 7 транзисторов (7Т), что больше, чем в типичной статичной ячейке RAM, использующей 6 или 4 транзистора, однако она использует только одну разрядную шину, а не две разных. Динамическая память (DRAM) работает гораздо эффективнее, и использует один транзистор и конденсатор, однако без обновления данных они будут утеряны.

Принципиальная схема хранящей бит ячейки регистра. Регистровый файл делается из массива таких ячеек.

Регистровый файл состоит из матрицы ячеек регистров, подобных описанному выше. Ширина матрицы составляет 16 ячеек, поскольку в регистрах хранятся 16-битные значения. Каждый регистр расположен по горизонтали, поэтому шина чтения или записи выбирает все ячейки определённого регистра. 16 вертикальных разрядных шин формируют единую шину, поэтому все 16 битов в выбранном регистре читаются и записываются параллельно.

На фото ниже показан увеличенный регистровый файл 8086 общего назначения, и видна матрица регистровых ячеек: 16 столбцов и 8 строк, 8 16-битных регистров. Затем дано увеличение одной регистровой ячейки в файле. Объясню, как реализована эта ячейка.

Фото кристалла 8086 с увеличением нижнего регистрового файла (восьми 16-битовых регистров), а потом и отдельной регистровой ячейки. Чтобы было видно кремниевые структуры, металлический и поликремниевый слои удалены.

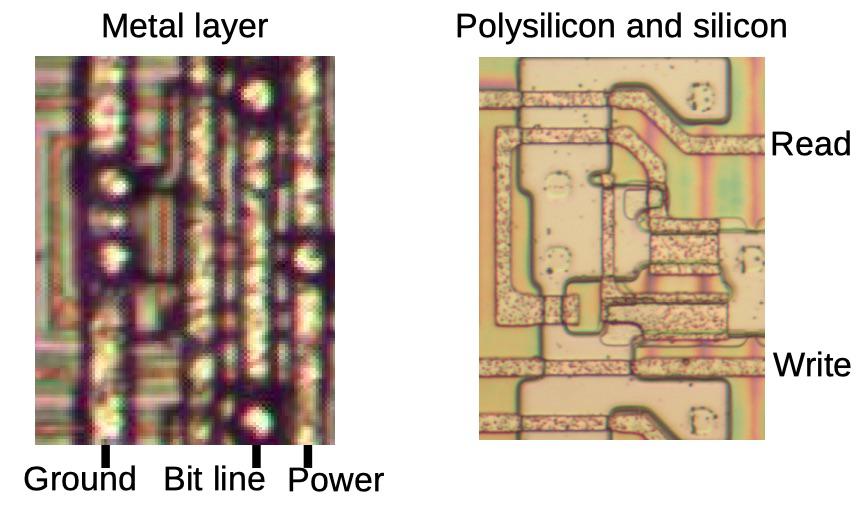

8086 делается из кремния с примесями и поликремниевых проводников с металлическими проводниками сверху. На левом фото ниже показаны вертикальные металлические проводники регистровой ячейки. Отмечены земля, питание и проводники разрядной шины (оставшийся проводник пересекает регистровый файл, но не контачит с ним). На фото справа металлический слой растворён, чтобы было видно поликремний и кремний. Шины чтения и записи – это горизонтальные поликремниевые проводники. Поскольку у чипа только один металлический слой, в регистрах для вертикальных шин используется металл, а для горизонтальных – поликремний, чтобы они не пересекались друг с другом). Сквозные соединения металла и кремния видны как более яркие круги на фото с металлом и как кружки на фото с кремнием.

Ячейка хранения регистра. На фото слева показан металлический слой, а справа – соответствующие слои поликремния и кремния.

На диаграмме ниже показано соответствие физической схемы регистровой ячейки с принципиальной. Инверторы состоят из транзистора А и В и регистров. Транзисторы C, D и E формируются отмеченными кусочками поликремния. Разрядная шина не видна, поскольку располагается в металлическом слое. Отметьте, что схема ячейки памяти сильно оптимизирована для минимизации размера. Также отметьте, что транзистор А гораздо меньше других. У инвертора А довольно слабый выходной ток, поэтому разрядная шина может преодолеть его при записи.

Регистровая ячейка от 8086 с соответствующей схемой

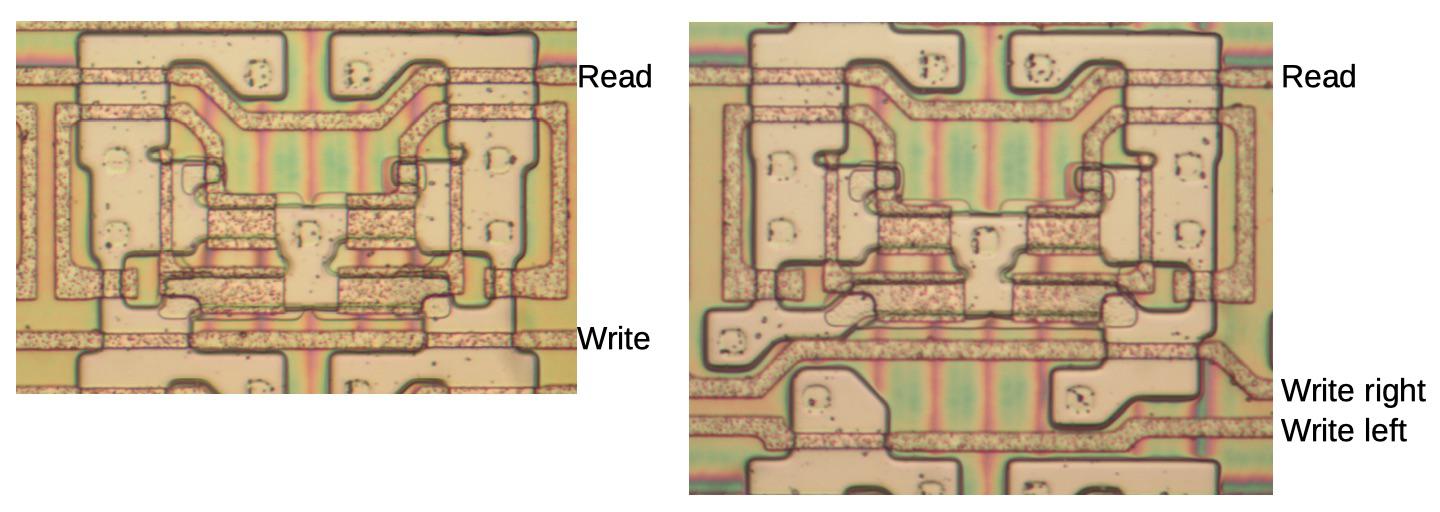

Регистровая ячейка на кристалле повторяются не единообразно – каждая вторая ячейка является зеркальным отражением предыдущей. Это увеличивает плотность регистровой ячейки – шина питания, идущая между двумя зеркальными ячейками, может питать их обе (то же касается и земли). Зеркальные повторения уменьшают количество требуемых шин питания и земли в два раза.

Две пары ячеек памяти с разными цепями. У ячеек слева одна шина записи, а справа – отдельные шины записи для левых и правых битов.

Многопортовые регистры

Пока что мы рассмотрели восемь «нижних регистров» общего назначения. У 8086 есть также семь «верхних регистров», используемых для доступа к памяти, включая печально известные сегментные регистры. У этих регистров схема работы более сложная, многопортовая, позволяющая одновременно вести несколько процессов чтения и записи. К примеру, многопортовый регистровый файл позволяет прочесть счётчик программы, сегментный регистр и записать другой сегментный регистр – и всё это одновременно.

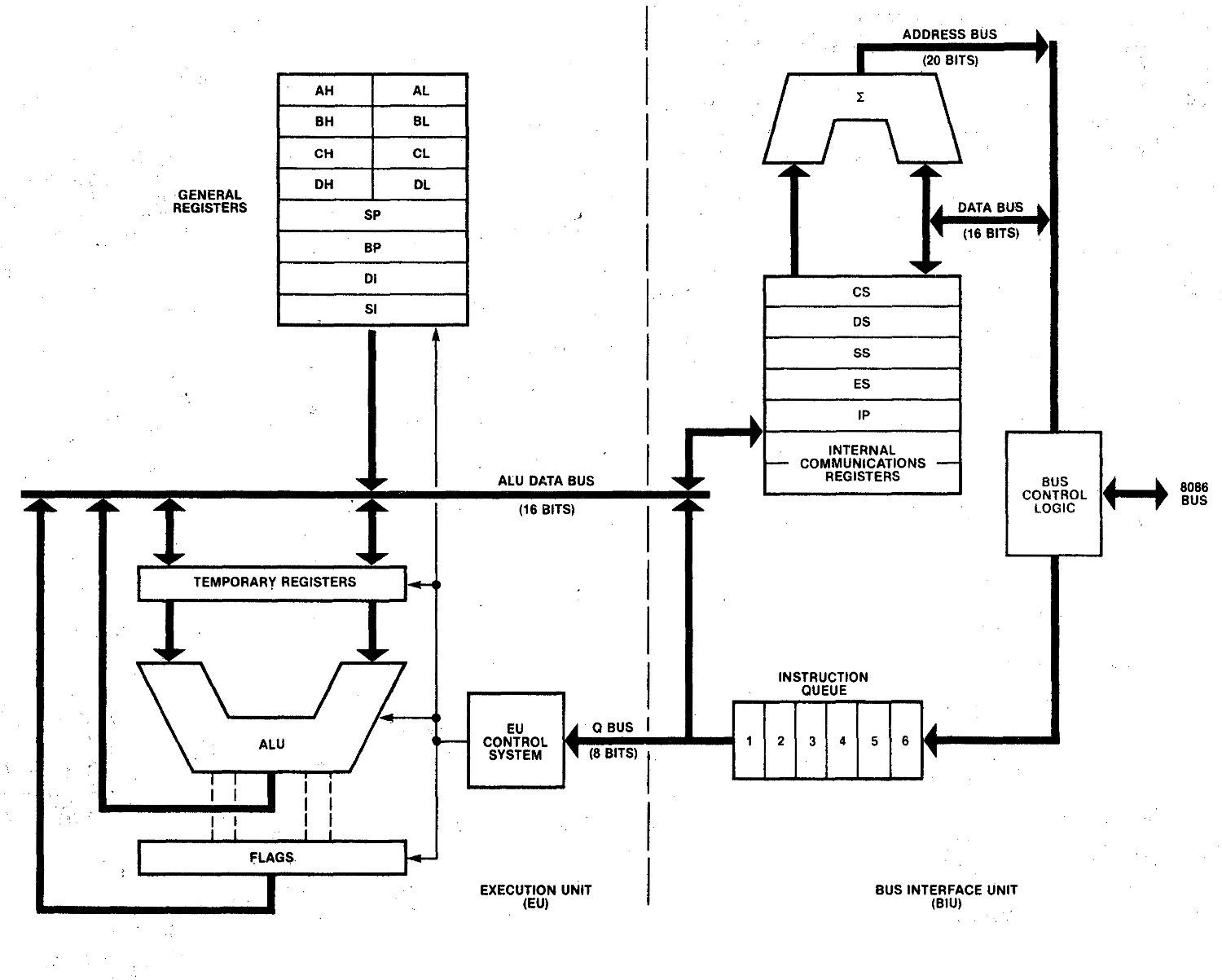

Приведённая ниже блок-схема отличается от большинства блок-схем для 8086, поскольку показывает реальную физическую реализацию процессора, а не ту, что представляет себе программист. В частности, на диаграмме показано два «регистра внутренних коммуникаций» среди регистров модуля интерфейса шины (справа) вместе с сегментными регистрами, совпадающими с 7 регистрами, которые можно рассмотреть на кристалле. Временные регистры, показанные ниже, физически являются частью АЛУ, поэтому в данной статье я их не рассматриваю.

В книжке "Разработка современных процессоров" обсуждаются сложные системы регистров в процессоре, начиная с 2000-х годов. Там написано, что сложность цепей быстро выходит за рамки трёх портов, а в некоторых передовых процессорах существуют регистровые файлы с 20 или более портами.

Многопортовая регистровая ячейка ниже создана на основе той же схемы из двух инверторов, однако у неё есть три разрядных шины (а не одна, как в предыдущем случае) и пять управляющих шин (вместо двух). Три шины чтения позволяют читать содержимое регистровой ячейки по любой из трёх разрядных шин, а две шины записи позволяют разрядной шине А или С вести запись в регистровую ячейку.

Многопортовая регистровая ячейка в процессоре 8086

У верхних регистров есть разное количество портов для чтения и записи: два регистра с 3 шинами чтения и 2 шинами записи, один регистр с 2 шинами чтения и 2 шинами записи, четыре регистра с 2 шинами чтения и 1 шиной записи. Три первых регистра – это, вероятно, счётчик программы, непрямой временный регистр и временный регистр операнда. Последние четыре – вероятно, сегментные регистры SS, DS, SS и ES. Также там есть три регистра буфера предварительной выборки команд, каждый с одной шиной для чтения и одной для записи.

Файл верхних регистров, состоящий из десяти 16-битных регистров. На фото видно кремний и поликремний. Вертикальные красные линии – остатки удалённого металлического слоя. Кликабельно.

Заключение

Хотя 8086 процессору уже 42 года, он до сих пор оказывает значительное влияние на современные компьютеры, поскольку архитектура х86 до сих пор очень часто используется. Регистры 8086 до сих пор существуют в современных компьютерах х86, хотя сегодня они уже имеют длину в 64 бита, а кроме этих регистров существует и множество других.

Кристалл 8086-го очень интересно изучать, поскольку его транзисторы можно рассмотреть под микроскопом. В своё время это был сложный процессор, поскольку на нём расположено 29 000 транзисторов, однако достаточно простой для того, чтобы отследить все цепи и понять, как они работают.

Учебный курс. Часть 4. Регистры процессора 8086

Автор: xrnd | Рубрика: Учебный курс | 13-03-2010 | Распечатать запись

Для того, чтобы писать программы на ассемблере, нам необходимо знать, какие регистры процессора существуют и как их можно использовать. Все процессоры архитектуры x86 (даже многоядерные, большие и сложные) являются дальними потомками древнего Intel 8086 и совместимы с его архитектурой. Это значит, что программы на ассемблере 8086 будут работать и на всех современных процессорах x86.

Все внутренние регистры процессора Intel 8086 являются 16-битными:

Всего процессор содержит 12 программно-доступных регистров, а также регистр флагов (FLAGS) и указатель команд (IP).

Индексные регистры предназначены для хранения индексов при работе с массивами. SI (Source Index) содержит индекс источника, а DI (Destination Index) — индекс приёмника, хотя их можно использовать и как регистры общего назначения.

Регистры-указатели BP и SP используются для работы со стеком. BP (Base Pointer) позволяет работать с переменными в стеке. Его также можно использовать в других целях. SP (Stack Pointer) указывает на вершину стека. Он используется командами, которые работают со стеком. (Про стек я подробно расскажу в отдельной части учебного курса)

Сегментные регистры CS (Code Segment), DS (Data Segment), SS (Stack Segment) и ES (Enhanced Segment) предназначены для обеспечения сегментной адресации. Код находится в сегменте кода, данные — в сегменте данных, стек — в сегменте стека и есть еще дополнительный сегмент данных. Реальный физический адрес получется путём сдвига содержимого сегментного регистра на 4 бита влево и прибавления к нему смещения (относительного адреса внутри сегмента). Подробнее о сегментной адресации рассказывается в части 31.

COM-программа всегда находится в одном сегменте, который является одновременно сегментом кода, данных и стека. При запуске COM-программы сегментные регистры будут содержать одинаковые значения.

Указатель команд IP (Instruction Pointer) содержит адрес команды (в сегменте кода). Напрямую изменять его содержимое нельзя, но процессор делает это сам. При выполнении обычных команд значение IP увеличивается на размер выполненной команды. Существуют также команды передачи управления, которые изменяют значение IP для осуществления переходов внутри программы.

Регистр флагов FLAGS содержит отдельные биты: флаги управления и признаки результата. Флаги управления меняют режим работы процессора:

- D (Direction) — флаг направления. Управляет направлением обработки строк данных: DF=0 — от младших адресов к старшим, DF=1 — от старших адресов к младшим (для специальных строковых команд).

- I (Interrupt) — флаг прерывания. Если значение этого бита равно 1, то прерывания разрешены, иначе — запрещены.

- T (Trap) — флаг трассировки. Используется отладчиком для выполнения программы по шагам.

Признаки результата устанавливаются после выполнения арифметических и логических команд:

- S (Sign) — знак результата, равен знаковому биту результата операции. Если равен 1, то результат — отрицательный.

- Z (Zero) — флаг нулевого результата. ZF=1, если результат равен нулю.

- P (Parity) — признак чётности результата.

- C (Carry) — флаг переноса. CF=1, если при сложении/вычитании возникает перенос/заём из старшего разряда. При сдвигах хранит значение выдвигаемого бита.

- A (Auxiliary) — флаг дополнительного переноса. Используется в операциях с упакованными двоично-десятичными числами.

- O (Overflow) — флаг переполнения. CF=1, если получен результат за пределами допустимого диапазона значений.

Не волнуйтесь, если что-то показалось непонятным. Из дальнейшего объяснения станет ясно, что к чему и как всем этим пользоваться 🙂

Комментарии:

Да нет. Все это храниться в программе, которую вы запустите. Прочитав оттуда уже происходит расталкивания данных по сегментам. А так на винте это общий файлик

а как насчёт 386 ? какие у него есть регистры ?

У 386-го регистры 32-битные: EAX, EBX, ECX, EDX, EDI, ESI и т.д.

Ещё есть некоторые дополнительные регистры, например FS и GS.

Различий много, в комментарии всё не рассказать.

Хотелось бы узнать, что подразумевается под размером выполненной команды.

Количество байтов, которое занимает команда в памяти.

Команды могут иметь разную длину. От 1 до 14 байтов.

Процессор декодирует команду и выполняет её, затем переходит к следующей.

O (Overflow) — флаг переполнения. CF=1, если получен результат за пределами допустимого диапазона значений.

CF = 1? Или O = 1?

P (Parity) — признак чётности результата. Как узнать когда числа четные а когда не четные?

C (Carry) — флаг переноса. CF=1, если при сложении/вычитании возникает перенос/заём из старшего разряда. При сдвигах хранит значение выдвигаемого бита.

Что за перенос/заем из старшего разряда? Что за выдвигаемый бит?

A (Auxiliary) — флаг дополнительного переноса. Используется в операциях с упакованными двоично-десятичными числами.

Опять непонятно что за перенос? И что за упакованные двоично-десятичные числа?

Функционально говоря, внутреннюю структуру 8086CPU можно разделить на две части:

1. Шинный интерфейсный блок BIU (шинный интерфейсный модуль) - отвечает за завершение передачи данных между ЦП и памятью или устройством ввода-вывода.

2. Модуль исполнения EU (модуль исполнения) - не подключен напрямую к внешней стороне системы, его функция отвечает только за выполнение инструкций.

(1) Шинный интерфейсный блок БИУ:

Особенности:

- ① Прочитать инструкцию - когда в очереди команд есть пустые байты (8088 1 пустой байт, 8086 2 пустой байт), вынуть последующие инструкции из памяти.Когда BIU извлекает инструкции, это не влияет на выполнение EU. Две работают параллельно, что значительно повышает скорость выполнения CPU.

- ② Read операнд - когда ЕС должен прочитать операнд из памяти или периферийного порта, он считывает данные из памяти или периферийного порта в соответствии с адресом, указанным ЕС для использования ЕС.

- ③ Записать результаты операций EU-операндов, данные или команды управления посылаются BIU в назначенный блок памяти или периферийный порт.

сочинение:

- Четыре 16-битных регистра сегмента: регистр сегмента кода CS (сегмент кода), регистр сегмента данных DS (сегмент данных), регистр сегмента стека SS (сегмент стека) и регистр дополнительного сегмента данных ES (дополнительный сегмент);

- 16-битный регистр указателя инструкций IP (указатель инструкций);

- 20-битный адресный сумматор;

- 6-байтовый буфер очереди команд;

- Внутренний регистр для связи с ЕС и схемой управления шиной и т. Д.

Сегментный регистр:

Есть 20 адресных штырей 8086CPU, Может предоставить 20-битную адресную информацию, может напрямую обращаться к 1M единицам хранения, ноВсе регистры, которые могут использоваться для предоставления адресной информации внутри ЦП, имеют 16 битов,Так как же использовать 16-битный регистр для адресации 20-битного адреса?8086/8088 принимает метод управления памятью сегментной структуры.

Сохраняет код инструкции и данные в сегменте кода, сегменте данных, сегменте стека и дополнительном сегменте данных, адреса сегментов этих сегментов предоставляются регистрами сегментов CS, DS, SS, ES, Адрес смещения кода или данных в сегменте задается соответствующим регистром или непосредственными данными. (Дополнительный сегмент данных обычно используется для хранения строки назначения во время строковой операции.)

- Описание:

- Когда программисты пишут исходные программы на ассемблере, они должныРазместите различные части программы в предписанных сегментах в соответствии с вышеуказанными положениями, Каждая исходная программа должна иметь как минимум один сегмент кода, а сегмент данных, сегмент стека и дополнительный сегмент данных определяются в соответствии с потребностями программы.

20-битный адресный сумматор

20-битный адрес, предоставленный ЦП для доступа к блоку хранения, генерируется сумматором адресов в BIU.

Преобразование логического адреса и физического адреса: (выделение)

Буфер очереди команд:

Очередь команд 8086 имеет 6 байтов, а очередь инструкций 8088 имеет 4 байта. Для 8086, когда в очереди команд 2 пустых байта, а для 8088 в очереди команд появляется 1 пустой байт, BIU автоматически выполнит цикл выборки команд и прочитает следующую команду, которая будет выполнена из блока памяти. В очередь инструкций. Они используют принцип «первым пришел - первым вышел», хранят их в порядке и везут в ЕС для исполнения.

(2) Исполнение блока ЕС:

сочинение:

- 16-разрядное арифметико-логическое устройство (АЛУ): выполняет арифметические и логические операции.

- 16-битный регистр флагов FLAGS: хранит флаги состояния и управления операциями процессора.

- Регистр временного хранения данных: временно хранить данные, участвующие в операции

- Общие регистры: в том числе четыре 16-разрядных регистра данных AX, BX, CX, DX и четыре 16-разрядных регистра указателя и индекса SP, BP и SI, DI.

- Схема управления ЕС

(1) Общие регистры (четыре регистра данных AX (AH / AL), BX (BH / BL), CX (CH / CL), DX (DH / DL), два регистра указателя адреса (SP, BP) и два Индексные регистры (SI, DI))

AX (Аккумулятор) называется аккумулятором. Использование этого регистра для хранения результатов операции может упростить инструкцию и повысить скорость ее выполнения. К тому же,

BX (Base) называется регистром базовых адресов. В 8086 / 8088CPU есть два регистра базовых адресов BX и BP.

CX (Counter) называется счетчиком. вИспользуйте этот регистр для хранения количества циклов при разработке программы циклов, Может упростить инструкции программы и помочь улучшить скорость работы программы.

DX (данные) называется регистром данных.Сохраните адрес порта ввода / вывода в инструкции ввода / вывода косвенной адресации регистра;При выполнении умножения и деления длинных двойных слов, DX и AX хранят операнд длинного двойного слова вместе, где DX хранит верхние 16 цифр.

(2) Индексный регистр SI, DI

SI (Source Index) называется регистром исходного индекса. DI (Индекс назначения) называется регистром индекса назначения.Эти два регистра обычно используются для хранения адреса смещения операнда во время строковой операции, где SI сохраняет адрес смещения исходной строки в сегменте данных, а DI сохраняет адрес смещения строки назначения в дополнительном сегменте данных.Конечно, они также могут поставить данные.

(3) Сегментные регистры (CS, DS, SS, ES)

(4) Контрольный регистр

1. Флаг состояния (6 бит)

- CF (Carry Flag) -Карри-флаг. При выполнении операций сложения и вычитания, если происходит перенос или заимствование старшего бита, CF равен 1, в противном случае он равен 0.Обычно используется для определения того, превышает ли результат операции без знака число диапазон чисел без знака, который может представлять компьютер.

- PF (Parity Flag) - флаг четности. (Обычно не используется)

- AF (вспомогательный флаг) - флаг вспомогательного переноса. (Обычно не используется)

- ZF (Zero Flag) - нулевой флаг. (Обычно не используется)

- SF (Sign Flag) - флаг-знак. Когда старший бит результата операции равен 1, SF = 1, в противном случае он равен 0

- OF (флаг переполнения) - флаг переполнения. Когда результат операции превышает диапазон значений, который может быть представлен числом со знаком, то есть переполнение, OF = 1, иначе 0.Используется для определения того, является ли результат переполнения числа со знаком.

2. Флаг управления (3 бита) - используется для управления работой CPU, устанавливается или сбрасывается программой

- TF (Trap Flag) - флаг отслеживания (trap). Он установлен для удобства проведения теста. Если TF установлен в 1, процессор находится в одношаговом режиме.

- IF (Interrupt Flag) - флаг включения прерывания. Это контрольный флаг, используемый для управления маскируемыми прерываниями. ЕслиУстановите IF на 1, чтобы позволить ЦП принимать маскируемые запросы на прерывание от контакта INTR, а если IF установлен на 0, ЦПУ запрещается принимать маскируемые сигналы запроса на прерывание.

- DF (Direction Flag) - флаг направления. Если DF установлен в 1, строковая операция выполняется способом уменьшения адреса, то есть, начиная с высокого адреса, адрес автоматически уменьшается каждый раз, когда он работает, в противном случае он выполняется в порядке увеличения адреса.

(5) Концепция автобусного цикла (опущено)

1. 8086/8088 организация памяти

8086/8088 имеет 20 адресных строк, которые могут напрямую обращаться к 1 М ячейкам памяти. Каждый блок памяти хранит данные байтового типа, и каждый блок памяти имеет 20-битный адрес, Адреса, соответствующие этим 1 М блокам хранения: 00000H

FFFFFH

2. Логические и физические адреса

Примечание: 1. Для блока хранения он имеет уникальный физический адрес, но поскольку 8086/8088 допускает перекрытие между сегментами, логический адрес блока хранения не является уникальным, то есть блок хранения имеет только уникальный Определенный физический адрес, но может иметь один или несколько логических адресов.

2. Следовательно, в памяти системы 8088 данные шрифта должны дважды обращаться к памяти, чтобы завершить операцию чтения / записи.

3.8086 / 8088 организация ввода / вывода

Система 8086/8088 и внешнее оборудование подключаются через интерфейсную схему ввода-вывода. Каждый интерфейс ввода / вывода имеет один или несколько портов.В микрокомпьютерной системе каждому порту назначается номер адреса, называемый адресом порта.Порт обычно представляет собой регистр или группу регистров в схеме интерфейса ввода / вывода.

Интеллектуальная рекомендация

[Makefile от более мелких к более глубоким полная запись обучения 4] Переменные и различные методы присвоения

Давайте сегодня узнаем о различных методах присваивания переменных в Makefile! Смысл тяжелой работы, чтобы бедность больше не ограничивать свое воображение! Добавьте QQ, чтобы вместе учиться и обменив.

[Luogu P3147] [BZOJ 4576] [USACO16OPEN]262144

Портал Луогу БЗОЙ Портал Описание заголовка Bessie likes downloading games to play on her cell phone, even though she doesfind the small touch screen rather cumbersome to use with her large hooves. Sh.

Читайте также: