Регистры адреса страниц в диспетчере памяти процессора используются для

Обновлено: 02.07.2024

Регистр процессора — сверхбыстрая память внутри процессора, предназначенная прежде всего для хранения промежуточных результатов вычисления (регистр общего назначения/регистр данных) или содержащая данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д. (специальные регистры).

Регистр представляет собой цифровую электронную схему, служащую для временного хранения двоичных чисел. В процессоре имеется значительное количество регистров, большая часть которых используется самим процессором и недоступна программисту. Например, при выборке из памяти очередной команды она помещается в регистр команд. Программист обратиться к этому регистру не может. Имеются так же регистры, которые в принципе программно доступны, но обращение к ним осуществляется из программ операционной системы (например управляющие регистры и теневые регистры дескрипторов сегментов). Этими регистрами пользуются в основном разработчики операционных систем.

Доступ к значениям, хранящимся в регистрах как правило в несколько раз быстрее, чем доступ к ячейкам оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём регистров (объём среднего модуля оперативной памяти сегодня составляет 1 Гб — 4 Гб [1] , суммарная «ёмкость» регистров общего назначения/данных для процессора 16 битов * 4 = 64 бита (8 байт)).

Основные регистры процессора, совместимого с Intel 386

IP (англ. Instruction Pointer ) — регистр, обозначающий смещение следующей команды относительно кодового сегмента.

IP — 16-битный (младшая часть EIP)

EIP — 32-битный аналог

Сегментные регистры — Регистры указывающие на сегменты.

CS — указатель на кодовый сегмент. Связка CS:IP указывает на адрес в памяти следующей команды.

Регистры данных — служат для хранения промежуточных вычислений.

RAX, RBX, RCX, RDX, RBP, RSI, RDI, RSP, R8 — R15 — 64-битные

EAX, EBX, ECX, EDX, EBP, ESI, EDI, ESP — 32-битные (extended AX)

AX, BX, CX, DX — 16-битные

например, AH - high AX - старшая половинка 8 бит

AL - low AX - младшая половинка 8 бит

| RAX | RBX | RCX | RDX | ||||||||||||

| —— | EAX | —— | EBX | —— | ECX | —— | EDX | ||||||||

| —— | —— | AX | —— | —— | BX | —— | —— | CX | —— | —— | DX | ||||

| —— | —— | AH | AL | —— | —— | BH | BL | —— | —— | CH | CL | —— | —— | DH | DL |

Регистр флагов EFLAGS — содержит текущее состояние процессора.

Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. По типу приёма и выдачи информации различают 2 типа регистров:

- С последовательным приёмом и выдачей информации — сдвиговые регистры.

- С параллельным приёмом и выдачей информации — параллельные регистры.

Сдвиговые регистры представляют собой последовательно соединённую цепочку триггеров. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала.

По назначение регистры различаются на:

- аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

- флаговые — хранят признаки результатов арифметических и логических операций;

- общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса;

- индексные — хранят индексы исходных и целевых элементов массива;

- указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стэка);

- сегментные — хранят адреса и селекторы сегментов памяти;

- управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

См. также

Примечания

Wikimedia Foundation . 2010 .

Полезное

Смотреть что такое "Регистры процессора" в других словарях:

Регистр (цифровая техника) — У этого термина существуют и другие значения, см. Регистр. 4 х разрядный сдвиговый регистр, преобразователь последовательного кода в параллельный и обратно Регистр последовательное или параллельное … Википедия

Мне периодически приходится объяснять разным людям некоторые аспекты архитектуры Intel® IA-32, в том числе замысловатость системы адресации данных в памяти, которая, похоже, реализовала почти все когда-то придуманные идеи. Я решил оформить развёрнутый ответ в этой статье. Надеюсь, что он будет полезен ещё кому-нибудь.

При исполнении машинных инструкций считываются и записываются данные, которые могут находиться в нескольких местах: в регистрах самого процессора, в виде констант, закодированных в инструкции, а также в оперативной памяти. Если данные находятся в памяти, то их положение определяется некоторым числом — адресом. По ряду причин, которые, я надеюсь, станут понятными в процессе чтения этой статьи, исходный адрес, закодированный в инструкции, проходит через несколько преобразований.

На рисунке — сегментация и страничное преобразование адреса, как они выглядели 27 лет назад. Иллюстрация из Intel 80386 Programmers's Reference Manual 1986 года. Забавно, что в описании рисунка есть аж две опечатки: «80306 Addressing Machanism». В наше время адрес подвергается более сложным преобразованиям, а иллюстрации больше не делают в псевдографике.

Начнём немного с конца — с цели всей цепочки преобразований.

Физический адрес

Конечный результат всех преобразований других типов адресов, перечисленных далее в этой статье — физический адрес. На нём кончается работа внутри центрального процессора по преобразованию адресов.

На самом деле, легко понять, что это ещё не конец. В платформе, которая должна обработать запрос данных от процессора, может быть несколько чипов DRAM, имеющих собственную структуру разбиения на блоки, а также различные периферийные устройства, отображённые на общее пространство физической памяти. Дальнейший путь транзакции с некоторым физическим адресом будет зависеть от конфигурации нескольких декодеров, находящихся на её пути внутри устройств платформы.

Эффективный адрес

Эффективный адрес — это начало пути. Он задаётся в аргументах индивидуальной машинной инструкции, и вычисляется из значений регистров, смещений и масштабирующих коэффициентов, заданных в ней явно или неявно.

Например, для инструкции (ассемблер в AT&T-нотации)

addl %eax, 0x11(%ebp, %edx, 8)

эффективный адрес операнда-назначения будет вычислен по формуле:

eff_addr = EBP + EDX * 8 + 0x11

Логический адрес

Без знания номера и параметров сегмента, в котором указан эффективный адрес, последний бесполезен. Сам сегмент выбирается ещё одним числом, именуемым селектором. Пара чисел, записываемая как selector:offset , получила имя логический адрес. Так как активные селекторы хранятся в группе специальных регистров, чаще всего вместо первого числа в паре записывается имя регистра, например, ds:0x11223344.

Здесь обычно у тех, кто столкнулся с этими понятиями впервые, голова начинает идти кругом. Несколько упростить (или усложнить) ситуацию помогает тот факт, что почти всегда выбор селектора (и связанного с ним сегмента) делается исходя из «смысла» доступа. По умолчанию, если в кодировке машинной инструкции не сказано иного, для получения адресов кода используются логические адреса с селектором CS, для данных — с DS, для стека — с SS.

Линейный адрес

Эффективный адрес — это смещение от начала сегмента — его базы. Если сложить базу и эффективный адрес, то получим число, называемое линейным адресом:

lin_addr = segment.base + eff_addr

Преобразование логический → линейный не всегда может быть успешным, так как при его исполнении проверяется несколько условий на свойства сегмента, записанных в полях его дескриптора. Например, проверяется выход за границы сегмента и права доступа.

Сегментация была модной на некотором этапе развития вычислительной техники. В настоящее она почти всюду была заменена другими механизмами, и используется только для специфических задач. Так, в режиме IA-32e (64-битном) только два сегмента могут иметь ненулевую базу. Для остальных четырёх в этом режиме всегда линейный адрес == эффективный.

Что такое виртуальный адрес?

В литературе и в документации других архитектур встречается ещё один термин — виртуальный адрес. Он не используется в документации Intel на IA-32, однако встречается, например, в описании Intel® Itanium, в котором сегментация не используется. Можно смело считать, что для IA-32 виртуальный == линейный.

В советской литературе по вычислительной технике этот вид адресов также именовался математическим.

Страничное преобразование

Следующее после сегментации преобразование адресов: линейный → физический — имеет множество вариаций в своём алгоритме, в зависимости от того, в каком режиме (32-битном, PAE или 64-битном) находится процессор.

Примечательно, сколько различных бит из разных системных регистров процессора влияют на процесс страничного преобразования в настоящее время. Я просмотрел свежую сентябрьскую редакцию Intel SDM [1], и вот полный список: CR0.WP, CR0.PG, CR4.PSE, CR4.PAE, CR4.PGE, CR4.PCIDE, CR4.SMEP, CR4.SMAP, IA32_EFER.LME, IA32_EFER.NXE, EFLAGS.AC.

Однако общая идея всегда одна и та же: линейный адрес разбивается на несколько частей, каждая из которых служит индексом в одной из системных таблиц, хранящихся в памяти. Записи в таблицах — это адреса начала таблицы следующего уровня или, для последнего уровня — искомая информация о физическом адресе страницы в памяти и её свойствах. Самые младшие биты не преобразуются, а используются для адресации внутри найденной страницы. Например, для режима PAE с размером страниц 4 кбайт преобразование выглядит так:

В разных режимах процессора различается число и ёмкость этих таблиц. Преобразование может завершиться неудачей, если очередная таблица не содержит валидных данных, или права доступа, хранящиеся в последней из них, запрещают доступ к странице; например, при записи в регионы, помеченные как «только для чтения», или попытке чтения памяти ядра из непривилегированного процесса.

Гостевой физический

До введения возможностей аппаратной виртуализации в процессорах Intel страничное преобразование было последним в цепочке. Когда же на одной системе работают несколько виртуальных машин, то физические адреса, получаемые в каждой из них, приходится транслировать ещё один раз. Это можно делать программным образом, или же аппаратно, если процессор поддерживает функциональность EPT (англ. Extended Page Table). Адрес, раньше называвшийся физическим, был переименован в гостевой физический для того, чтобы отличать его от настоящего физического. Они связаны с помощью EPT-преобразования. Алгоритм последнего схож с ранее описанным страничным преобразованием: набор связанных таблиц с общим корнем, последний уровень которых определяет, существует ли физическая страница для указанной гостевой физической.

Полная картина

Я попытался собрать все преобразования адреса в одну иллюстрацию. В ней преобразования обозначены стрелками, типы адресов обведены в рамки.

Как уже было сказано выше, каждое из преобразований может вернуть ошибку для адресов, не имеющих представления в следующем по цепочке виде. Устранение подобных проблем — это задача операционных систем и мониторов виртуальных машин, реализующих абстракцию виртуальной памяти.

Виртуальной памятью (виртуальным адресным пространством) называют

| оперативное запоминающее устройство |

| невидимую программисту кэш-память |

| регистровую память центрального процессора |

| адресное пространство, которое представляется разработчику при создании кода программы |

| буферную память, используемую для согласования быстродействия процессора и оперативной памяти |

| множество имеющихся в компьютере ячеек оперативной памяти |

Виртуальные станицы одной задачи должны загружаться в физическую память

| распределяясь по любым свободным областям памяти |

| в одну область памяти единым массивом |

| строго по одной станице и подгружаться по мере надобности |

Для того, чтобы в 16-ти разрядной ЭВМ получить 20-ти разрядный физический адрес, необходимо

| чтобы АЛУ процессора также было 20-ти разрядным |

| прибавить к нему содержимое регистра адреса памяти |

| дополнить его справа 4-мя недостающими разрядами |

| в 16-ти разрядной ЭВМ могут быть только 16-ти разрядные физические адреса |

| прибавить к нему 20-ти разрядную константу |

| дополнить его слева 4-мя недостающими разрядами |

Для того, чтобы в 16-ти разрядной ЭВМ получить 22-х разрядный физический адрес, необходимо

| дополнить его слева 6-ю недостающими разрядами |

| дополнить его справа 6-ю недостающими разрядами |

| в 16-ти разрядной ЭВМ могут быть только 16-ти разрядные физические адреса |

| прибавить к нему 22-х разрядную константу |

| прибавить к нему содержимое регистра адреса памяти |

| чтобы АЛУ процессора также было 22-х разрядным |

Для того, чтобы на компьютере можно было выполнять программу, размер которой превышает размер физической памяти,

| на диске должно быть выделено место для файла виртуальной памяти |

| Такая программа выполняться не может |

| в процессоре должно быть соответствующее число регистров общего назначения |

| выполняемая программа должна "уметь" преобразовывать виртуальные адреса в физические |

| в компьютере должны быть специальные программные средства обеспечивающие управление виртуальным и физическим адресными пространствами |

| в компьютере должна быть кэш-память |

| в процессоре должны быть аппаратные средства преобразования виртуальных адресов в физические |

Для того, чтобы на компьютере можно было выполнять программу, размер которой превышает размер физической памяти,

| должны быть специальные программные средства обеспечивающие управление виртуальным и физическим адресными пространствами |

| в процессоре должно быть увеличенное число регистров общего назначения |

| кэш-память должна иметь соответствующие размеры |

| Такая программа выполняться не может |

| в процессоре должны быть аппаратные средства преобразования виртуальных адресов в физические |

К какому объему памяти можно адресоваться с помощью 16-разрядного адреса?

| 1 Мегабайт |

| 128 Килобайт |

| 65 536 Байт |

| 1 073 741 824 Байта |

| 1 048 576 Байт |

| 1 Гигабайт |

| 2 Гигабайта |

| 2 Мегабайт |

| 64 Килобайта |

К какому объему памяти можно адресоваться с помощью 20-разрядного адреса?

| 2 Мегабайт |

| 2 Гигабайта |

| 128 Килобайт |

| 1 073 741 824 Байта |

| 1 Мегабайт |

| 1 048 576 Байт |

| 1 Гигабайт |

| 64 Килобайта |

| 65 536 Байт |

К какому объему памяти можно адресоваться с помощью 22-разрядного адреса

| 64 Килобайта |

| 2 Гигабайта |

| 128 Килобайт |

| 1 073 741 824 Байта |

| 4 Мегабайта |

| 1 048 576 Байт |

| 1 Гигабайт |

| 65 536 Байт |

| 1 Мегабайт |

К какому объему памяти можно адресоваться с помощью 30-разрядного адреса?

| 1 048 576 Байт |

| 128 Килобайт |

| 64 Килобайта |

| 65 536 Байт |

| 2 Мегабайт |

| 1 Мегабайт |

| 2 Гигабайта |

| 1 Гигабайт |

К какому объему памяти можно адресоваться с помощью 32-разрядного адреса?

| 65 536 Байт |

| 1 048 576 Байт |

| 2 Мегабайт |

| 1 Гигабайт |

| 1 073 741 824 Байта |

| 64 Килобайта |

| 128 Килобайт |

| 4 Гигабайта |

| 1 Мегабайт |

| используется для повышения надежности работы компьютера |

| используется для снижения энергопотребления компьютера |

| может адресоваться обычным образом из программы |

| имеет меньшую емкость, чем основная оперативная память |

| недоступна для адресации из программы |

| имеет емкость большую, чем основная оперативная память, но меньшее быстродействие |

| используется для ускорения работы компьютера |

| может адресоваться обычным образом из программы |

| заменяет регистры процессора |

| имеет более высокое быстродействие, чем основная оперативная память |

| используется для повышения надежности работы компьютера |

| размещается между процессором и основной оперативной памятью |

| предназначена для размещения стека |

| размещается между основной оперативной памятью и внешними устройствами |

| используется для снижения энергопотребления компьютера |

| область на диске, отводимая для свопинга виртуальных страниц |

| программно управляемая область памяти, предназначенная для хранения индексов размещения программных модулей на диске |

| область оперативной памяти, отведенная операционной системе под регистры внешних устройств и векторы прерывания |

| промежуточная буферная память, предназначенная для согласования быстродействия процессора и основной памяти |

| область памяти, отводимая под стек |

| память, расположенная на внешнем запоминающем устройстве |

| область оперативной памяти, используемая для свопинга виртуальных страниц |

| недоступная пользовательским программам область памяти, предназначенная для хранения индексов размещения программных модулей на диске |

Могут ли 16-разрядные процессоры работать с памятью объемом 2 Мегабайта?

| Могут некоторые 16-разрядные процессоры |

| Могут любые 16-разрядные процессоры |

| Нет не могут |

Может ли в компьютере выполняться программа, размер которой превышает размер физической памяти?

| Зависит от того, есть ли в компьютере кэш-память |

| Нет не может |

| Это зависит от числа регистров общего назначения |

| Может, если специальные программные средства обеспечивают управление виртуальным и физическим адресными пространствами |

| Может, если в процессоре имеются аппаратные средства преобразования виртуальных адресов в физические |

| Да может |

Может ли в компьютере выполняться программа, размер которой превышает размер физической памяти?

| Может, если выполняемая программа "умеет" преобразовывать виртуальные адреса в физические |

| Может, если в процессоре имеются аппаратные средства преобразования виртуальных адресов в физические |

| Может, если на диске выделено место для файла виртуальной памяти |

| Нет не может |

| Это зависит от числа регистров общего назначения |

| Зависит от того, есть ли в компьютере кэш-память |

| Может, если специальные программные средства обеспечивают управление виртуальным и физическим адресными пространствами |

Может ли виртуальная память (логическое адресное пространство) быть больше физической памяти?

| Нет, не может |

| Они должны иметь одинаковый размер |

| Да может |

Преобразование виртуального адреса в физический адрес осуществляется:

| преобразования виртуального адреса с помощью специальной функции |

| физический адрес должен полностью совпадать с виртуальным, поэтому преобразовывать адреса не требуется |

| путем операции сдвига виртуального адреса вправо или влево на необходимое число разрядов |

| прибавления двоичной константы к виртуальному адресу |

| добавления к виртуальному адресу справа недостающих разрядов |

Преобразование виртуального адреса в физический осуществляется путем:

| сдвига разрядов виртуального адреса на число разрядов, соответствующих номеру страницы |

| добавления к виртуальному адресу недостающих разрядов |

| умножения виртуального адреса на константу |

| прибавления к виртуальному адресу текущего содержимого регистра счетчика команд |

| прибавления к виртуальному адресу константы |

При отображении виртуального адресного пространства на физическое адресное пространство:

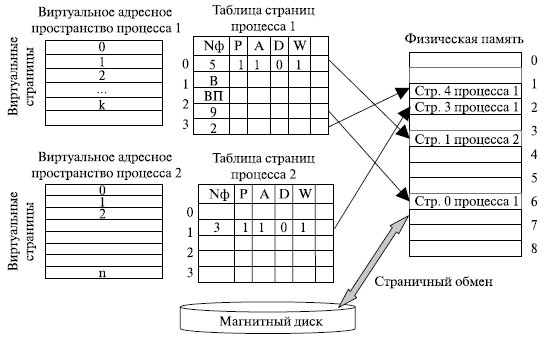

Большинство систем виртуальной памяти используют технику, называемую страничной организацией памяти [32, 37]. Любой процесс, реализуемый в компьютере, может обратиться к множеству адресов в памяти. Адреса могут формироваться с применением индексации, базовых регистров, сегментных регистров и другими путями. Эти программно формируемые адреса, называемые виртуальными адресами, формируют виртуальное адресное пространство . На компьютерах без виртуальной памяти виртуальные адреса подаются непосредственно на шину памяти и вызывают для чтения или записи слово в физической памяти с тем же самым адресом.

Когда используется виртуальная память , виртуальные адреса не передаются напрямую шиной памяти. Вместо этого они передаются диспетчеру памяти ( MMU – Memory Management Unit), который отображает виртуальные адреса на физические адреса памяти, как показано на рис. 6.9. Здесь диспетчер памяти показан как часть микросхемы процессора, как обычно и бывает чаще всего. Но логически он мог бы быть отдельной микросхемой, как было в недавнем прошлом.

Все имеющееся в настоящее время множество реализаций виртуальной памяти различается в основном способом структуризации виртуального адресного пространства.

В настоящее время выделяют три метода реализации виртуальной памяти.

- Страничная виртуальная память организует перемещение данных между основной памятью и диском страницами – частями виртуального адресного пространства фиксированного и сравнительно небольшого размера.

- Сегментная виртуальная память предусматривает перемещение данных сегментами – частями виртуального адресного пространства произвольного размера, полученного с учетом смыслового значения данных.

- Сегментно- страничная виртуальная память использует двухуровневое деление: виртуальное адресное пространство делится на сегменты, а затем сегменты делятся на страницы. Единицей перемещения данных является страница.

Для временного хранения сегментов и страниц на диске отводится специальная область либо специальный файл (страничный файл или файл подкачки – paging file ). Текущий размер страничного файла является важным параметром, оказывающим влияние на возможности операционной системы: чем больше страничный файл , тем больше приложений может одновременно выполнять ОС (при фиксированном размере оперативной памяти). Однако необходимо понимать, что увеличение числа одновременно работающих приложений за счет увеличения размера страничного файла замедляет их работу, так как значительная часть времени при этом тратится на перемещение данных на диск и обратно.

Размер страничного файла в современных ОС является настраиваемым параметром, который выбирается администратором системы для достижения компромисса между уровнем программирования и быстродействием системы.

При страничной организации виртуальное адресное пространство каждого процесса делится на части одинакового, фиксированного для данной системы размера, называемые виртуальными страницами ( Virtual pages). В общем случае размер виртуального адресного пространства не кратен размеру страницы, поэтому последняя страница дополняется фиксированной областью.

Вся оперативная память машины также делится на части такого же размера, называемые физическими страницами (или блоками, или кадрами). Размер страницы выбирается равным степени двойки: 1024, 2048, 4096 байт и т.д. Это позволяет упростить механизм преобразования адресов.

При создании процесса ОС загружает в операционную память несколько его виртуальных страниц (начальные страницы кодового сегмента и сегмента данных). Копия всего виртуального адресного пространства процесса находится на диске. Смежные виртуальные страницы не обязательно находятся в смежных физических страницах. Для каждого процесса ОС создает таблицу страниц – информационную структуру, содержащую записи обо всех виртуальных страницах процесса (рис. 6.10).

Запись таблицы ( дескриптор страницы) включает следующую информацию:

- номер физической страницы (N ф.с.), в которую загружена данная виртуальная страница ;

- признак присутствия Р, устанавливаемый в единицу, если данная страница находится в оперативной памяти;

- признак модификации страницы D, который устанавливается в единицу всякий раз, когда производится запись по адресу, относящемуся к данной странице;

- признак обращения А к странице, называемый также битом доступа, который устанавливается в единицу при каждом обращении по адресу, относящемуся к данной странице;

- другие управляющие биты, служащие, например, для целей защиты или совместного использования памяти на уровне страниц.

Перечисленные признаки в большинстве моделей процессов устанавливаются аппаратно схемами процессора при выполнении операций с памятью. Информация из таблицы страниц используется для решения вопроса о необходимости перемещения той или иной страницы между памятью и диском, а также для преобразования виртуального адреса в физический. Сами таблицы страниц, так же как и описываемые ими страницы, размещаются в оперативной памяти.

Поскольку процесс может задействовать большой объем виртуальной памяти (например, в Windows 2000 он равен 2 32 = 4 Гбайт), при использовании страницы объемом 4 Кбайт (2 12 ) потребуется 2 20 записей в таблице страниц для каждого процесса. Понятно, что выделять такое количество оперативной памяти под таблицы страниц нецелесообразно. Для преодоления этой проблемы большинство схем виртуальной памяти хранит таблицы страниц не в реальной, а в виртуальной памяти. Это означает, что сами таблицы страниц становятся объектами страничной организации. При работе процесса как минимум часть его таблицы страниц должна располагаться в основной памяти, в том числе запись о странице, выполняющейся в настоящий момент. Адрес таблицы страниц включается в контекст процесса . При активизации очередного процесса ОС загружает адрес его таблицы страниц в специальный регистр .

При каждом обращении к памяти выполняется поиск номера виртуальной страницы , содержащей требуемый адрес , затем по этому номеру определяется нужный элемент таблицы страниц и из него извлекается описывающая страницу информация . Далее анализируется признак присутствия, и если данная виртуальная страница находится в оперативной памяти, то выполняется преобразование виртуального адреса в физический. Если же нужная виртуальная страница в данный момент выгружена на диск , то происходит страничное прерывание .

Выполняющий процесс переводится в состояние ожидания, активизируя процесс из очереди процессов, находящихся в состоянии готовности. Параллельно программа обработки страничного прерывания находит на диске требуемую виртуальную страницу и пытается ее загрузить в оперативную память . Если в памяти имеется свободная физическая страница , то загрузка выполняется немедленно. Если же свободных страниц нет, то на основании принятой в данной системе стратегии замещения страниц решается вопрос о том, какую страницу следует выгрузить из оперативной памяти.

После того как выбрана страница, которая должна покинуть оперативную память , обнуляется ее бит присутствия и анализируется ее признак модификации. Если удаляемая страница за время последнего требования в оперативной памяти была модифицирована, то ее новая версия должна быть переписана на диск . Если нет, то принимается во внимание, что на диске уже имеется предыдущая копия этой виртуальной страницы , и никакой записи на диск не производится. Физическая страница объявляется свободной. Из соображений безопасности в некоторых системах освобождаемая страница обнуляется, чтобы невозможно было использовать содержимое выгруженной страницы. Для хранения информации о положении вытесненной страницы в страничном файле ОС может задействовать специальные поля таблицы страниц.

Виртуальный адрес при страничном распределении может быть представлен в виде пары ( P, Sv ), где Р – номер виртуальной страницы процесса ( нумерация страниц начинается с 0), а Sv – смещение в пределах виртуальной страницы (рис. 6.11). Физический адрес также может быть представлен в виде пары ( N, Sf ), где N – номер физической страницы, а Sf – смещение а пределах физической страницы. Задача подсистемы виртуальной памяти состоит в отображении пары значений ( P, Sv ) в пару ( N, Sf ).

Чтобы понять механизм реализации этого отображения, следует остановиться на двух базисных свойствах страничной организации. Как уже отмечалось, объем страницы, как виртуальной, так и физической, выбирается равным степени двойки – 2 к ( k = 8 и более). Отсюда следует, что смещение Sv и Sf может быть получено отделением k младших разделов в двоичной записи виртуального и, соответственно, физического адреса страницы. При этом оставшиеся старшие разделы адреса представляют собой двоичную запись номера виртуальной и, соответственно, физической страницы. Дополнив эти номера к нулям, можно получить начальный адрес виртуальной и физической страниц.

Второе свойство – линейность адресного пространства виртуальной и физической страницы – приводит к тому, что Sf = Sv. Отсюда следует простая схема преобразования виртуального адреса в физический.

При обращении к памяти по некоторому виртуальному адресу ( P, Sv ) аппаратные схемы процессора выполняют следующие действия.

- Из специального регистра процессора извлекается начальный адрес АТ таблицы страниц активного процесса. С помощью сумматора по значениям АТ, Р, L (длина отдельной записи в таблице страниц) определяется адрес нужной записи в таблице страниц:

В итоге полученный физический адрес оперативной памяти представляется парой значений ( N, Sf ).

Рассмотрим пример, поясняющий основные характеристики организации страничной виртуальной памяти. Пусть компьютер имеет оперативную память объемом Еоп = 256 Мбайт , размер страницы выбран равным Естр= 4 Кбайт . В этом случае количество физических страниц равно

Для отображения физического адреса произвольного байта оперативной памяти потребуется K = log2 256*20 2 0 = 28 двоичных разрядов.

Число разрядов для отображения смещения в странице M = log2 4 Кбайт = log2 4096 = 12 .

Если процессор имеет 32-разрядную структуру, то на номер виртуальной страницы отводится 32-12=20 двоичных разрядов. Таким образом, число виртуальных страниц равно Nв = 220 (примерно 1 млн виртуальных страниц ).

Для каждой виртуальной страницы в таблице страниц должна быть запись , содержащая номер виртуальной страницы (20 двоичных разрядов), начальный адрес соответствующей ей физической страницы плюс дополнительные разряды, характеризующие свойства страницы (присутствие, модификация, обращение и т.п.), на которые потребуется 1 байт . Поскольку адрес начала физической страницы кратен 4096, то на него достаточно 28 – 12 = 16 двоичных разрядов (остальные 12 разрядов заполняются нулями). Таким образом, одна запись таблицы страниц займет 20 + 16 + 8 = 44 двоичных разрядов или 6 байт . Общий объем таблицы страниц составит 6 * Nв = 6 Мбайт .

Реально при выборе структуры записи таблицы страниц нужно учитывать следующие факторы. Современные компьютеры позволяют наращивать объем оперативной памяти (например, в ПК она может почти достигать объема виртуальной памяти и даже более). Поэтому на адрес физической страницы в нашем примере следует выделить 32-12 = 20 двоичных разрядов. С другой стороны, нет необходимости в записи (дескрипторе) виртуальной страницы иметь поле с номером виртуальной страницы (20 разрядов), так как адрес нужной записи можно вычислять, как это было рассмотрено выше. Следовательно, в нашем примере длина записи должна быть равной 32 - 12 + 8 = 28 двоичным разрядам, т.е. с округлением до целого числа байт – 4 байт . Таким образом, для каждого выполняющегося в компьютере процесса ОС должна создать страничную таблицу размером 4 * Nв байт = 5 * 2 20 = 4 Мбайт .

Процедура преобразования виртуального адреса в физический без принятия специальных мер ( кэширование активных страниц) занимает один цикл оперативной памяти, который затрачивается на считывание номера физической страницы из таблицы страниц. Поэтому любое обращение к ОП будет занимать 2 цикла вместо одного при работе без виртуальной памяти. Другим фактором, влияющим на производительность систем, являются затраты времени на обработку страничных прерываний. При неправильно выбранной стратегии замещения страниц может возникнуть ситуация, когда система тратит большую часть времени впустую на подкачку страниц из оперативной памяти на диск и обратно.

Регистры MMX / 3DNow!

Расширение MMX

MMX было первым расширением, реализующим технологию SIMD (Single Instruction - Multiple Data). Основная идея SIMD заключается в одновременной обработке нескольких элементов данных одной операцией. Расширение MMX использует новые типы упакованных 64-битные целочисленных данных:

- 8 упакованных байт ( Packed byte );

- 4 упакованных слова ( Packed word );

- 2 упакованных двойных слова ( Packed double word );

- 1 учетверенное слово ( Quad word );

Эти типы данных могут специальным образом обрабатываться в 64-битных регистрах MM 0- MM 7, представляющих собой младшие биты стека 80-битных регистров FPU . Каждая инструкция MMX выполняет действие сразу над всем комплектом операндов (8, 4, 2 или 1), размещенных в адресуемых регистрах. Как и регистры FPU , эти регистры не могут использоваться для адресации памяти. Совпадение регистров MMX и FPU накладывает ограничение на чередование кодов FPU и MMX . В отличие от стека FPU регистры MMX адресуются не с помощью стека, а физически (по своим физическим номерам).

Расширение 3 DNow !

Технология 3 DNow !, разработанная AMD , расширяет возможности MMX . Она позволяет оперировать с новым типом данных - парой упакованных вещественных чисел одинарной точности. Эти числа занимают по двойному слову (32 бита) в 64-битных регистрах MMX .

Расширение 3 DNow ! работает с упакованными данными в FP -формате с одинарной точностью, а также упакованными 8 байт, 4 слова, 2 двойных слова и 64-битными целыми числами, размещая их в младших 64 битах регистров FPU / MMX .

Блок XMM

Кроме инструкций с новым блоком XMM в расширение SSE входят и дополнительные целочисленные инструкции с регистрами MMX , а также инструкции управления кэшированием.

- упакованная пара вещественных чисел двойной точности;

- упакованные целые числа: 16 байт, 8 слов, 4 двойных слова или пара учетверенных слов.

Регистры архитектуры x86-64 (AMD64)

Выпущенные недавно фирмой AMD новые процессоры Athlon 64 и Opteron имеют архитектуру x 86-64, которая в отличие от архитектуры x 86 является полностью 64-битной. Она естественным образом расширяет регистры общего назначения x 86 до 64 битов и увеличивает их количество. Также удваивается число регистров XMM . Регистры FPU / MMX остаются без изменений.

Читайте также: