Intel r spi flash controller a324 что это

Обновлено: 07.07.2024

Identify your products and get driver and software updates for your Intel hardware.

Available Downloads

PROC_IO_Win7_32_64_1.1.9.0140.zip

Windows 7, 32-bit*

Windows 7, 64-bit*

Detailed Description

Purpose

Installs the I/O controllers driver version 1.1.9.0140 on Intel® NUCs. This package provides drivers for the following processor features:

UART Host Controller

This download is valid for the product(s) listed below.

Intel Software License Agreement

The terms of the software license agreement included with any software you download will control your use of the software.

INTEL SOFTWARE LICENSE AGREEMENT

Do not use or load this software and any associated materials (collectively,

conditions. By loading or using the Software, you agree to the terms of this

Agreement. If you do not wish to so agree, do not install or use the Software.

LICENSES: Please Note:

shall apply to you.

back-up copies of the Software, subject to these conditions:

1. This Software is licensed for use only in conjunction with Intel

component products. Use of the Software in conjunction with non-Intel

component products is not licensed hereunder.

2. You may not copy, modify, rent, sell, distribute or transfer any part

of the Software except as provided in this Agreement, and you agree to

prevent unauthorized copying of the Software.

3. You may not reverse engineer, decompile, or disassemble the Software.

4. You may not sublicense or permit simultaneous use of the Software by

more than one user.

5. The Software may include portions offered on terms in addition to those

set out here, as set out in a license accompanying those portions.

SINGLE USER LICENSE. You may copy the Software onto a single computer for

your personal, noncommercial use, and you may make one back-up copy of the

Software, subject to these conditions:

1. This Software is licensed for use only in conjunction with Intel

component products. Use of the Software in conjunction with non-Intel

component products is not licensed hereunder.

2. You may not copy, modify, rent, sell, distribute or transfer any part

of the Software except as provided in this Agreement, and you agree to

prevent unauthorized copying of the Software.

3. You may not reverse engineer, decompile, or disassemble the Software.

4. You may not sublicense or permit simultaneous use of the Software by

more than one user.

5. The Software may include portions offered on terms in addition to those

set out here, as set out in a license accompanying those portions.

OEM LICENSE: You may reproduce and distribute the Software only as an

integral part of or incorporated in Your product or as a standalone

Software maintenance update for existing end users of Your products,

excluding any other standalone products, subject to these conditions:

1. This Software is licensed for use only in conjunction with Intel

component products. Use of the Software in conjunction with non-Intel

component products is not licensed hereunder.

2. You may not copy, modify, rent, sell, distribute or transfer any part

of the Software except as provided in this Agreement, and you agree to

prevent unauthorized copying of the Software.

3. You may not reverse engineer, decompile, or disassemble the Software.

4. You may only distribute the Software to your customers pursuant to a

5. The Software may include portions offered on terms in addition to those

set out here, as set out in a license accompanying those portions.

NO OTHER RIGHTS. No rights or licenses are granted by Intel to You, expressly

or by implication, with respect to any proprietary information or patent,

copyright, mask work, trademark, trade secret, or other intellectual property

right owned or controlled by Intel, except as expressly provided in this

OWNERSHIP OF SOFTWARE AND COPYRIGHTS. Title to all copies of the Software

remains with Intel or its suppliers. The Software is copyrighted and

protected by the laws of the United States and other countries, and

international treaty provisions. You may not remove any copyright notices

from the Software. Intel may make changes to the Software, or to items

referenced therein, at any time without notice, but is not obligated to

support or update the Software. Except as otherwise expressly provided, Intel

grants no express or implied right under Intel patents, copyrights,

trademarks, or other intellectual property rights. You may transfer the

Software only if the recipient agrees to be fully bound by these terms and if

you retain no copies of the Software.

LIMITED MEDIA WARRANTY. If the Software has been delivered by Intel on

physical media, Intel warrants the media to be free from material physical

defects for a period of ninety days after delivery by Intel. If such a defect

is found, return the media to Intel for replacement or alternate delivery of

the Software as Intel may select.

EXCLUSION OF OTHER WARRANTIES. EXCEPT AS PROVIDED ABOVE, THE SOFTWARE IS

INCLUDING WARRANTIES OF MERCHANTABILITY, NONINFRINGEMENT, OR FITNESS FOR A

PARTICULAR PURPOSE. Intel does not warrant or assume responsibility for the

accuracy or completeness of any information, text, graphics, links or other

items contained within the Software.

LIMITATION OF LIABILITY. IN NO EVENT SHALL INTEL OR ITS SUPPLIERS BE LIABLE

FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, LOST PROFITS,

BUSINESS INTERRUPTION, OR LOST INFORMATION) ARISING OUT OF THE USE OF OR

INABILITY TO USE THE SOFTWARE, EVEN IF INTEL HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES. SOME JURISDICTIONS PROHIBIT EXCLUSION OR

LIMITATION OF LIABILITY FOR IMPLIED WARRANTIES OR CONSEQUENTIAL OR INCIDENTAL

DAMAGES, SO THE ABOVE LIMITATION MAY NOT APPLY TO YOU. YOU MAY ALSO HAVE

OTHER LEGAL RIGHTS THAT VARY FROM JURISDICTION TO JURISDICTION.

TERMINATION OF THIS AGREEMENT. Intel may terminate this Agreement at any time

if you violate its terms. Upon termination, you will immediately destroy the

Software or return all copies of the Software to Intel.

APPLICABLE LAWS. Claims arising under this Agreement shall be governed by the

laws of California, excluding its principles of conflict of laws and the

United Nations Convention on Contracts for the Sale of Goods. You may not

export the Software in violation of applicable export laws and regulations.

Intel is not obligated under any other agreements unless they are in writing

and signed by an authorized representative of Intel.

restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its

successor. Use of the Software by the Government constitutes acknowledgment

2200 Mission College Blvd., Santa Clara, CA 95052.

Your file download has started. If your download did not start, please click here to initiate again.

List of driver files that match with the above device in our database.

You are viewing the drivers of an anonymous computer which may be not the same with your current computer. These driver(s) may not work with your computer. Please click on the link below to download, scan and get the correct drivers.

Предыстория

Во время очередной уборки был случайно выключен удлинитель, к которому были подключены работающие системный блок и монитор. Системный блок состоит из:

- материнская плата — ASRock B75 Pro 3

- процессор — Intel Core i5-3570

- блок питания — Corsair CX750M

После включения системник начал издавать пять противных писков, что вроде как соответствует неисправности процессора. Процессор, судя по Яндекс.Маркету, на данный момент стоит от 11000 руб. Покупать довольно накладно, а недорогой, но слабенький не хочется. В общем, немного испугался…

Порылся в интернете, выяснил, что точная причина неисправности может быть совсем другая. Это вселило небольшую надежду. Но надо как-то найти эту самую причину.

В первую очередь подключил другой старенький БП — комп не запускается.

Для дальнейших проверок принес домой автомобильный комп. Состав:

- материнская плата — ASRock B75M-ITX

- процессор — Intel Pentium G640T

Как хорошо, что компоненты оказались взаимозаменяемыми.

Вытащил из автомобильного компа процессор, вставил его в домашний — комп не запускается. Но появилась надежда, что процессор все таки цел, а неисправна материнка, которая немного дешевле (хотя новые на чипсетах не H61 и H67 — дефицит).

Далее домашний процессор вставил в автомобильный комп — комп заработал. Следовательно, процессор живой, а проблема в материнке. Начал грешить на BIOS (Winbond 25Q64BVAIG).

Собственно, программирование

Хорошо, что микросхема BIOS не впаяна, а на обычной панельке DIP-8. Программатора у меня нет, заказывать в Китае и ждать месяц — не выход. Решил сделать программатор из ноутбука жены и имеющейся в наличии Arduino Nano. Покопался в интернете… Везде в основном прошивка заливается через COM-порт, я же решил прошивать с карты памяти (так вроде гораздо быстрее).

Набросал схему подключения:

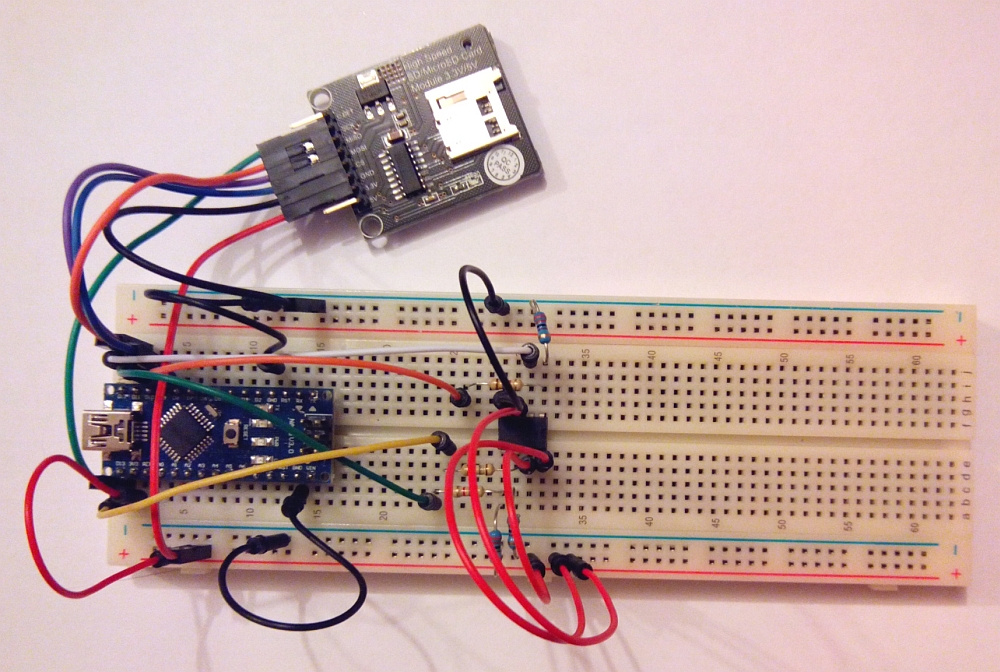

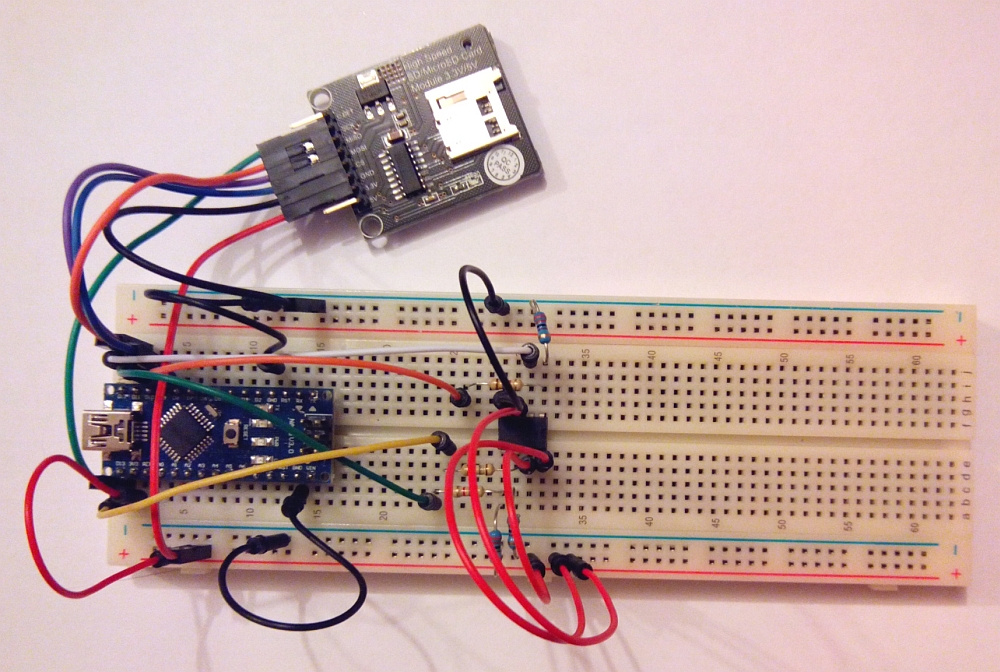

Собрал все на макетной плате:

Тип и объем карты памяти, способ ее форматирования, имя файла должны соответствовать требованиям библиотеки SD Arduino.

Для начала набросал скетч, который считывает содержимое SPI Flash и записывает его в файл на карту памяти, попутно вычисляя контрольную сумму по методу Checksum-32, т.е. простым суммированием.

Запустил скетч, получившийся файл сравнил с оригинальным BIOS — получилось около 140000 несовпадающих байт.

Далее написал скетч, который читает файл с карты памяти и записывает его на SPI Flash, предварительно стирая чип.

Запустил, подождал, скетч вывел контрольную сумму, она совпала с контрольной суммой оригинального файла. Но это контрольная сумма файла на карте памяти, мне же нужна контрольная сумма содержимого SPI Flash.

Можно было использовать первый скетч, но написал третий, который только считает контрольную сумму содержимого SPI Flash по тому же алгоритму.

Контрольная сумма SPI Flash совпала с контрольной суммой оригинального файла.

После вставки прошитой микросхемы BIOS в домашний комп — он благополучно заработал.

В среде Arduino IDE необходимо установить библиотеку SPIFlash через управление библиотеками.

Контрольную сумму вычислял с помощью HEX-редактора HxD.

PS: Первоначально в качестве SD-модуля использовал вот такой:

Но с ним были частые глюки, не инициализировалась SD-карта. Помогало «горячее» переподключение самой SD-карты при подключенной к компу Arduino.

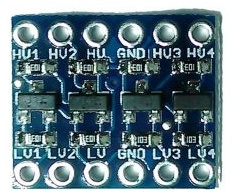

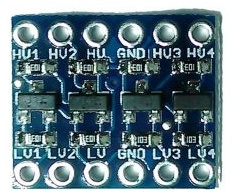

PPS: Вместо резисторов пробовал подключить двунаправленный конвертер сигналов:

Но с ним схема не заработала.

Эта статья продолжает тему, связанную с угрозой искажения BIOS материнской

платы вредоносными программами. В ранее опубликованном материале

"Проникновение в BIOS ROM"

N1 и N2 был

приведен пример программы, выполняющей запись в микросхему BIOS, рассмотрены

механизмы защиты, используемые производителями материнских плат и причины, по

которым данные механизмы часто оказываются неэффективными. Напомним, что эта

проблема возникла более 10 лет назад, когда в качестве носителя BIOS начали

использовать микросхемы Flash ROM, допускающие перезапись содержимого без

физического вмешательства в компьютер. Таким образом, возможность оперативной

перезаписи (обновления) BIOS, привела к побочному эффекту – риску его случайного

или преднамеренного искажения.

Казалось бы, сегодня на эту тему уже все сказано. Но время идет, появляются

новые типы микросхем Flash ROM и интерфейсов для их подключения. Это

сопровождается появлением новых методов защиты BIOS от несанкционированного

искажения, и, конечно, новых уязвимостей. В ранее опубликованном материале,

ссылка на который приведена в начале статьи, рассматриваемая тема раскрыта на

примере платформы, использующей микросхему SST 49LF004A, подключенную к

интерфейсу LPC (Low Pin Count). Сегодня, ему на смену пришел интерфейс SPI

(Serial Peripheral Interface). Напомним, что для перезаписи содержимого

микросхемы BIOS, программа должна взаимодействовать с двумя блоками регистров:

регистры интерфейса Flash ROM, расположенные в составе "южного моста" чипсета и

регистры, входящие в состав самой микросхемы Flash ROM. При переходе от

интерфейса LPC к SPI, архитектура двух указанных блоков существенно изменилась.

Поэтому есть смысл рассмотреть взаимодействие программ с микросхемой BIOS,

механизмы защиты и их уязвимости применительно к современным платформам.

Материал снабжен примерами на ассемблере. Для экспериментов использовалась

материнская плата Gigabyte GA-965P-S3, построенная на чипсете Intel 965,

описанном в 2. В качестве носителя BIOS на данной плате используется

микросхема SST 25VF080B, описанная в [5]. Эта микросхема имеет объем 8 Мегабит

(1 Мегабайт) и подключается к интерфейсу SPI. Некоторые микросхемы других

производителей, использующих тот же интерфейс, описаны в [4,6,7]. Описание

интерфейса SPI приведено в [8,9]. При взаимодействии с контроллером SPI, нам

потребуется использовать механизмы доступа к конфигурационному пространству,

описанные в документах 10.

Интерфейс SPI: историческая справка

Как известно, быстродействие микросхемы постоянного запоминающего устройства

(Flash ROM), используемой в качестве носителя BIOS, практически не влияет на

общую производительность компьютера. Это связано с тем, что при старте

материнской платы, BIOS переписывается (или распаковывается) в оперативную

память Shadow RAM и при обращении к BIOS в сеансе ОС, программы работают с

оперативной памятью, а не с микросхемой Flash ROM. Поэтому, в отличие от

процессора, памяти, графической подсистемы, эволюция которых сопровождается

ростом производительности, микросхемы Flash ROM и их интерфейсы развиваются в

другом направлении. Здесь главными критериями являются уменьшение стоимости,

потребляемой мощности и занимаемой площади на материнской плате. Главный метод

достижения этих целей – уменьшение количества проводников между микросхемой BIOS

и контроллером, обычно входящим в состав "южного моста" чипсета. С точки зрения

метода подключения микросхемы BIOS, можно выделить три поколения материнских

плат:

1) На платах, использующих шину ISA, устанавливались микросхемы постоянных

запоминающих устройств с раздельными линиями адреса, данных и управления. При

этом для каждого разряда адреса и данных, а также для каждого сигнала управления

(чтение, запись) требовался свой провод, точнее печатный проводник на плате.

2) С появлением чипсетов Intel 810, 815, на основе "хабовой" архитектуры,

шина ISA ушла в прошлое. Ряд устройств материнской платы, ранее подключаемых к

ISA (контроллер гибких дисков, порты COM и LPT, микросхема BIOS), "переехали" на

интерфейс Low Pin Count или LPC, название которого переводится как "малое

количество сигналов". Сигналы адреса, данных и управления в этом интерфейсе

передаются по пяти линиям (не считая сигналов сброса, тактирования и линий

питания), в режиме мультиплексирования во времени. Микросхемы BIOS, используемые

в таких платформах, иногда называют Firmware Hub или FWH. Пример программы

стирания и записи микросхемы BIOS, приведенный в ранее опубликованной статье

"Проникновение в BIOS ROM" N1 и N2" предназначен для таких платформ.

Отметим, что интерфейс LPC также поддерживается современными чипсетами и

разработчик материнской платы может использовать для подключения микросхемы BIOS

как LPC, так и SPI. Сфера применения интерфейса SPI не ограничивается

материнскими платами компьютеров. Внимательный читатель мог обратить внимание на

то, что из-за перехода к последовательному формату данных, каждый из описанных

интерфейсов использует больше тактов для выполнения операций чтения и записи,

чем его предшественник, что чревато снижением быстродействия. Но этого не

происходит, так как указанное обстоятельство компенсируется ростом частоты и

оптимизацией форматов данных. Шина ISA работает на частотах 5-8MHz, LPC на

33MHz, SPI на 33-50 MHz.

Архитектура микросхемы SPI Flash ROM

Микросхемы SPI Flash, в частности SST25VF080B, используют три сигнала для

приема и передачи данных. SCK (Serial Clock) – вход для тактирования

передаваемых или принимаемых данных. SI (Serial Input) – вход для передачи

данных от контроллера к микросхеме, по этой линии побитно передаются адрес,

данные для записи, и коды команд управления микросхемой. SO (Serial Output) –

выход для передачи данных от микросхемы к контроллеру, по этой линии побитно

передаются читаемые данные, а также информация о состоянии микросхемы.

Контроллер управляет микросхемой посредством команд, инициирующих операции

чтения и записи данных, стирания, чтения идентификаторов микросхемы, чтения и

записи регистра статуса и т.п.

Назначение каждого из восьми контактов микросхемы, описание всех команд, а

также другие подробности содержатся в [5].

Архитектура контроллера SPI

Контроллер SPI, входящий в состав "южного моста" Intel ICH8, содержит более

20 регистров управления и состояния. Регистры адресуются в пространстве памяти с

использованием технологии memory-mapped I/O, рассмотренной в ранее

опубликованной статье "Устройства системной поддержки. Исследовательская работа

N 8". Описание всех регистров и команд контроллера SPI выходит за рамки

данной статьи, рассмотрим основные отличия программной модели интерфейса SPI от

его предшественника - интерфейса LPC, акцентируя внимание на регистрах,

используемых при выполнении основных операций – чтении идентификаторов, записи и

стирании Flash ROM.

Напомним, что физический доступ к микросхеме BIOS (не путать с областью

Shadow RAM) осуществляется посредством окна, примыкающего к верхней границе

диапазона 0-4GB. Например, Flash ROM размером 1 Мбайт будет доступен в диапазоне

FFF00000h-FFFFFFFFh. В платформах, использующих интерфейсы ISA и LPC, через тот

же диапазон, при выполнении операций стирания и записи выполняется передача

команд и записываемых данных для микросхемы Flash ROM, а также чтение ее

статуса. Платформа, использующая интерфейс SPI, рассматриваемая в данной статье,

также поддерживает чтение содержимого микросхемы BIOS через указанный диапазон,

но для передачи управляющей и статусной информации во время записи и стирания

Flash ROM, используется другой метод доступа. Информация для выполнения цикла на

шине SPI (адрес и данные) записывается в специальные регистры контроллера SPI

(Flash Address и Flash Data соответственно), затем в регистр Software Sequencing

Flash Control передается команда на выполнение цикла обращения к Flash ROM

(чтения или записи). После этого, через регистр Software Sequencing Flash Status

можно определить момент завершения операции и проконтролировать наличие ошибок.

Данные, прочитанные из Flash ROM, находятся в регистре Flash Data.

Бит 0 (SPI Cycle In Progress) – используется для определения момента

завершения операции на шине SPI. "0" означает, что шина SPI свободна и программа

может запускать следующий цикл. "1" означает, что шина SPI занята, выполняется

транзакция. Бит устанавливается и сбрасывается аппаратно, доступен только для

чтения.

Бит 1 (Reserved) – не используется.

Бит 2 (Cycle Done Status) – устанавливается в "1" аппаратно, при

завершении транзакции на шине SPI. Для сброса, программа должна записать "1" в

данный бит.

Бит 3 (Flash Cycle Error) – устанавливается в "1" аппаратно, если при

выполнении транзакции имели место ошибки: защита записи или попытка запуска

следующей транзакции до завершения предыдущей. Для сброса, программа должна

записать "1" в данный бит.

Бит 4 (Access Error Log) – устанавливается в "1" аппаратно, если имели

место попытки обращения к микросхеме BIOS, нарушающие права доступа к заданным

диапазонам адресов, запрограммированным в конфигурационных регистрах контроллера

SPI.

Биты 5-7 (Reserved) – не используются.

Бит 9 (SPI Cycle Go) – запуск транзакции на SPI. Запись "1" в этот бит

запускает выполнение транзакции, тип и содержание которой определяются

состоянием битов 10-31 этого же регистра.

Бит 10 (Atomic Cycle Sequence) – при передаче приказа на выполнение

транзакции, запись "1" в этот бит запрещает внешним событиям вмешиваться в

процессы, происходящие на интерфейсе SPI до тех пор, пока не будут выполнены три

фазы: передача префиксной команды, передача основной команды и завершение

выполнения основной команды.

Отметим, что таким образом реализуется один из механизмов защиты от

случайного искажения содержимого микросхемы BIOS. Так называемые префиксные

команды (например, Write Enable) должны предшествовать командам, изменяющим

содержимое микросхемы (например, Write, Erase). Получив код команды, содержащий

"1" в данном бите, все три фазы контроллер выполняет аппаратно, без

вмешательства процессора до завершения выполнения основной команды.

Бит 11 (Sequence Prefix Opcode Pointer) – при использовании префиксных

команд (когда бит 10 установлен в "1", см. выше), этот бит выбирает один из двух

байтов, который будет передан в качестве префиксной команды для микросхемы SPI

Flash. При "0" выбирается младший байт регистра Prefix Opcode Configuration

Register, при "1" – старший.

Бит 12-14 (Cycle Opcode Pointer) – это битовое поле выбирает один из

восьми байтов, который будет передан в качестве основной команды для микросхемы

SPI Flash. Указанные байты находятся в регистре Opcode Menu Configuration

Register.

Бит 15 (Reserved) – не используется.

Биты 16-21 (Data Byte Count) – задает количество байтов данных для

операций чтения или записи данных. Количество равно значению этого поля плюс 1.

Например: 000000b=1 байт, 111111b=64 байта.

Бит 22 (Data Cycle) – Задает наличие байтов данных в команде. "0"

означает, данные отсутствуют (например, в команде стирания), "1" означает, что

данные присутствуют (например, в команде чтения статуса, данными является

содержимое регистра статуса).

Биты 24-26 (SPI Cycle Frequency) – задает частоту битовой

синхронизации при выполнении транзакции на SPI. Используются два значения

(остальные зарезервированы): 000b=20MHz, 001b=33MHz.

Биты 27-31 (Reserved) – не используются.

Отметим, что предварительное заполнение восьми байтов регистра Opcode Menu

Configuration Register и двух байтов регистра Prefix Opcode Configuration

Register выполняет BIOS при старте платформы. Поэтому, при формировании битовых

полей, выбирающих код команды и код префикса, программа должна просканировать

указанные регистры и найти, под каким номером в них находятся коды требуемых

операций. Варианты заполнения могут быть разными, даже среди материнских плат

одной модели, использующих различные версии BIOS. Некоторые утилиты перезаписи

Flash изменяют содержимое указанных регистров.

Детальное описание всех регистров и команд контроллера SPI приводится в [3].

Описание команд микросхемы SPI Flash приводится в 5. Информация, изложенная

выше, также проиллюстрирована ассемблерными примерами, прилагаемыми к статье.

Механизмы доступа к Flash ROM и защита записи

В общем случае, для инициирования операций стирания или перезаписи микросхемы

BIOS, программа должна выполнить четыре действия:

- Настроить регистры "южного моста" чипсета, управляющие размещением

микросхемы BIOS в адресном пространстве для обеспечения доступа к полному

объему микросхемы. - Выключить режим защиты записи BIOS, реализуемый средствами "южного моста"

чипсета. - Выключить режим защиты записи BIOS, реализуемый средствами микросхемы

Flash ROM. - Передать команду стирания или записи микросхеме Flash ROM.

Рассмотрим подробнее эти процедуры, механизмы защиты, препятствующие их

несанкционированному выполнению и, конечно, уязвимости этих механизмов.

Как было сказано выше, при выполнении операций записи и стирания, программный

доступ к микросхеме SPI Flash осуществляется посредством регистров контроллера

SPI, без использования диапазона адресов, в котором доступен образ микросхемы

BIOS. Поэтому перенастройка чипсета для доступа к диапазону FFF00000h-FFFFFFFFh

в данном примере не потребуется.

Практика показывает, что данный механизм "защиты от снятия защиты" обычно не

активируется разработчиками BIOS. Во всех материнских платах, исследованных

автором, бит BLE=0, поэтому для снятия защиты записи достаточно установить бит

BIOSWE=1, эта операция не будет перехвачена.

Микросхема Intel ICH8 также поддерживает защиту содержимого микросхемы BIOS,

путем задания адресных диапазонов, защищенных от чтения и (или) записи.

Теоретически, на базе данного механизма можно реализовать эффективную защиту,

так как запрет программно включается процедурами BIOS при старте платформы, и

может быть снят только при аппаратном сбросе. Но и этот механизм обычно не

активируется разработчиками BIOS.

Источники информации

1) Intel Low Pin Count (LPC) Interface Specification. Revision 1.1. Document

Number 251289-001.

2) Intel P965 Express Chipset Family Datasheet – For the Intel 82P965 Memory

Controller Hub (MCH). Document Number: 313053-001.

3) Intel I/O Controller Hub 8 (ICH8) Family Datasheet – For the Intel 82801HB

ICH8 and 82801HR ICH8R I/O Controller Hubs. Document Number: 313056-001.

4) 1 Mbit SPI Serial Flash SST25VF010 Data Sheet. Document Number:

S71233-01-000.

5) 8 Mbit SPI Serial Flash SST25VF080B Data Sheet. Document Number:

S71296-01-000.

6) W25X10A, W25X20A, W25X40A, W25X80A 1M-bit, 2M-bit, 4M-bit and 8M-bit

Serial Flash Memory with 4KB sectors and dual output SPI Data Sheet.

7) MX25L802 8M-bit [8Mx1] CMOS Serial Flash EEPROM Data Sheet.

8) SPI EEPROM Interface Specification. Part Number 223-0017-004 Revision H.

Во время очередной уборки был случайно выключен удлинитель, к которому были подключены работающие системный блок и монитор. Системный блок состоит из:

- материнская плата — ASRock B75 Pro 3

- процессор — Intel Core i5-3570

- блок питания — Corsair CX750M

Порылся в интернете, выяснил, что точная причина неисправности может быть совсем другая. Это вселило небольшую надежду. Но надо как-то найти эту самую причину.

В первую очередь подключил другой старенький БП — комп не запускается.

Для дальнейших проверок принес домой автомобильный комп. Состав:

- материнская плата — ASRock B75M-ITX

- процессор — Intel Pentium G640T

Вытащил из автомобильного компа процессор, вставил его в домашний — комп не запускается. Но появилась надежда, что процессор все таки цел, а неисправна материнка, которая немного дешевле (хотя новые на чипсетах не H61 и H67 — дефицит).

Далее домашний процессор вставил в автомобильный комп — комп заработал. Следовательно, процессор живой, а проблема в материнке. Начал грешить на BIOS (Winbond 25Q64BVAIG).

Собственно, программирование

Хорошо, что микросхема BIOS не впаяна, а на обычной панельке DIP-8. Программатора у меня нет, заказывать в Китае и ждать месяц — не выход. Решил сделать программатор из ноутбука жены и имеющейся в наличии Arduino Nano. Покопался в интернете… Везде в основном прошивка заливается через COM-порт, я же решил прошивать с карты памяти (так вроде гораздо быстрее).

Набросал схему подключения:

Собрал все на макетной плате:

Тип и объем карты памяти, способ ее форматирования, имя файла должны соответствовать требованиям библиотеки SD Arduino.

Для начала набросал скетч, который считывает содержимое SPI Flash и записывает его в файл на карту памяти, попутно вычисляя контрольную сумму по методу Checksum-32, т.е. простым суммированием.

Запустил скетч, получившийся файл сравнил с оригинальным BIOS — получилось около 140000 несовпадающих байт.

Далее написал скетч, который читает файл с карты памяти и записывает его на SPI Flash, предварительно стирая чип.

Запустил, подождал, скетч вывел контрольную сумму, она совпала с контрольной суммой оригинального файла. Но это контрольная сумма файла на карте памяти, мне же нужна контрольная сумма содержимого SPI Flash.

Можно было использовать первый скетч, но написал третий, который только считает контрольную сумму содержимого SPI Flash по тому же алгоритму.

Контрольная сумма SPI Flash совпала с контрольной суммой оригинального файла.

После вставки прошитой микросхемы BIOS в домашний комп — он благополучно заработал.

В среде Arduino IDE необходимо установить библиотеку SPIFlash через управление библиотеками.

Контрольную сумму вычислял с помощью HEX-редактора HxD.

PS: Первоначально в качестве SD-модуля использовал вот такой:

Но с ним были частые глюки, не инициализировалась SD-карта. Помогало «горячее» переподключение самой SD-карты при подключенной к компу Arduino.

PPS: Вместо резисторов пробовал подключить двунаправленный конвертер сигналов:

Но с ним схема не заработала.

Когда в качестве носителя BIOS начали использовать микросхемы Flash ROM, допускающие перезапись содержимого без физического вмешательства в компьютер, то появилась возможность оперативной перезаписи (обновления) BIOS, и это привело к риску его случайного или преднамеренного искажения. Поэтому появились и новые методы защиты BIOS от несанкционированного искажения. Появились и новые типы микросхем Flash ROM и интерфейсы для их подключения.

Рис. 1. ICH10 и ПЗУ BIOS

Интерфейс SPI. Основная архитектура шины SPI для базового варианта интерфейса приведена на рис. 2 (классическая четырех проводная структура). В ней один ведущий управляет несколькими (N) ведомыми. Все ведомые подключены параллельно на линиях SCLK, MISO и MOSI шины SPI. Выборка ведомого происходит с помощью одной из линий портов ввода/вывода, которая соединяется с входом NSS соответствующего ведомого. Обычно такая архитектура используется для построения систем с одним микроконтроллером, исполняющим роль ведущего, и рядом периферийных микросхем, исполняющих роль ведомых. В качестве периферийных микросхем может быть использован ряд современных микросхем, оснащенных интерфейсом SPI, например, таймеры реального времени RTC, аналого-цифровые преобразователи ADC, цифро-аналоговые преобразователи DAC, различные микросхемы памяти Flash-ПЗУ и т. п.

Рис. 2. Основная архитектура шины SPI (базовый вариант)

Частным случаем предыдущей архитектуры является трех проводная структура, приведенная на рис. 3. в ней ведомая микросхема постоянно выбрана, и необходимость в использовании четвертой линии интерфейса SPI отсутствует.

Рис. 3. Трехпроводная структура шины SPI

При обмене данными по интерфейсу SPI контроллер может работать как в режиме Master, так и в режиме Slave. При этом пользователь может задать следующие параметры:

- скорость передачи (четыре программируемых значения);

- формат передачи (от младшего разряда к старшему или наоборот).

Дополнительной возможностью подсистемы SPI является «пробуждение» микроконтроллера из режима Idle при поступлении данных. Модуль SPI использует четыре внешних вывода микроконтроллера. Как и для большинства периферийных устройств микроконтроллера, эти выводы являются линиями порта ввода/вывода общего назначения. В ряде случаев пользователь должен самостоятельно задать режим работы вывода, используемого модулем SPI, в соответствии с его назначением, причем возможность управления внутренними подтягивающими резисторами выводов, работающих как входы, сохраняется независимо от способа управления их режимом работы.

Обмен данными осуществляется (передаваемые данные записываются, а принимаемые данные считываются) через регистр данных (SPDR). Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое приемного буфера сдвигового регистра. Поэтому этот регистр можно назвать буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI. Перед началом выполнения обмена необходимо разрешить работу модуля SPI. При подключении к ведущему устройству нескольких ведомых, что разрешено спецификацией SPI, выбор конкретного ведомого устройства осуществляется подачей на его вход SS сигнала «низкого уровня».

Спецификация интерфейса SPI предусматривает 4 режима передачи данных. Эти режимы различаются соответствием между фазой (момент считывания сигнала) тактового сигнала SCK, его полярностью и передаваемыми данными. Вывод SS(Slave Select - выборка ведомого) предназначен для выбора активного ведомого устройства и в режиме Slave всегда является входом.При подаче на него напряжения «низкого уровня» модуль SPI активируется и вывод MOSI переключается в режим вывода данных (если это задано пользователем). Остальные выводы модуля SPI являются в этом режиме входами. А при подаче на вывод SS напряжения «высокого уровня» все выводы модуля SPI переключаются в режим ввода данных. При этом модуль переходит в неактивное состояние и прием данных не производится. Каждый раз, когда на вывод SS подается напряжение «высокого уровня», происходит сброс модуля SPI. Соответственно, если изменение состояния этого вывода произойдет во время передачи данных, и прием и передача немедленно прекратятся, а передаваемый и принимаемый байты будут потеряны.

Производители микросхем в своей документации могут использовать и другие обозначения этих сигналов, например:

С - вход синхронизации (соответствует сигналу SCK);

D - входные последовательные данные (соответствует сигналу MOSI);

Q - выходные последовательные данные (соответствует сигналу MISO);

Рис. 4. Режим обмена SPI Mode 0

Рис. 5. Режим обмена SPI Mode 1

Рис. 6. Режим обмена SPI Mode 2

Рис. 7. Режим обмена SPI Mode 3

На рис. 9, 10, 11, 12 приведены примеры протоколов операций на интерфейсе SPI.

Рис. 9. Протокол интерфейса SPI (код операции - 03H, операция «Чтение» см. табл. 3)

Таблица 2. Программирование Status Register Block Protection для SST25VF080B

Таблица 3. Device Operation Instructions (команды операций устройства)

Рис. 10. Операция стирания блоком 32-KByte и 64-KByte на SPI (код операции 52H и D8H)

Рис.11. Операция «Чтение» Read-Status-Register (RDSR), код операции 05H

Рис. 12. Write-Enable (WREN), Write Disable (WRDI), код операции 06H и 04H

Для перезаписи содержимого микросхемы BIOS, программа должна взаимодействовать с двумя блоками регистров:

- регистры интерфейса Flash ROM, расположенные в составе "южного моста" чипсета,

- и регистры, входящие в состав самой микросхемы Flash ROM.

При переходе от интерфейса LPC к SPI, архитектура двух указанных блоков существенно изменилась (контроллер SPI, входящий, например, в состав "южного моста" Intel ICH8, содержит более 20 регистров управления и состояния). Регистры адресуются в пространстве памяти с использованием технологии memory-mapped I/O (описание всех регистров и команд контроллера SPI выходит за рамки данной статьи, мы ограничимся регистрами, используемыми при выполнении основных операций – чтении идентификаторов, записи и стирании Flash ROM).

Физический доступ к микросхеме BIOS (не надо путать с областью Shadow RAM) осуществляется посредством окна, примыкающего к верхней границе диапазона 0-4GB. Например, Flash ROM размером 1 Мбайт будет доступен в диапазоне FFF00000h-FFFFFFFFh. В платформах, использующих интерфейс LPC, через тот же диапазон, при выполнении операций стирания и записи выполняется передача команд и записываемых данных для микросхемы Flash ROM, а также чтение ее статуса.

Платформа, использующая интерфейс SPI, рассматриваемая в данной статье, также поддерживает чтение содержимого микросхемы BIOS через указанный диапазон, но для передачи управляющей и статусной информации во время записи и стирания Flash ROM, используется другой метод доступа. Информация для выполнения цикла на шине SPI (адрес и данные) записывается в специальные регистры контроллера SPI (Flash Address и Flash Data соответственно), затем в регистр Software Sequencing Flash Control передается команда на выполнение цикла обращения к Flash ROM (чтения или записи). После этого, через регистр Software Sequencing Flash Status можно определить момент завершения операции и проконтролировать наличие ошибок. Данные, прочитанные из Flash ROM, находятся в регистре Flash Data.

Механизмы доступа к Flash ROM и защита записи. В общем случае, для инициирования операций стирания или перезаписи микросхемы BIOS, программа должна выполнить четыре действия:

- настроить регистры "южного моста" чипсета, управляющие размещением микросхемы BIOS в адресном пространстве для обеспечения доступа к полному объему микросхемы;

- выключить режим защиты записи BIOS, реализуемый средствами "южного моста" чипсета;

- выключить режим защиты записи BIOS, реализуемый средствами микросхемы Flash ROM;

- передать команду стирания или записи микросхеме Flash ROM.

Рассмотрим подробнее эти процедуры, механизмы защиты, препятствующие их несанкционированному выполнению и, конечно, точки уязвимости этих механизмов. Как было сказано выше, при выполнении операций записи и стирания, программный доступ к микросхеме SPI Flash осуществляется посредством регистров контроллера SPI, без использования диапазона адресов, в котором доступен образ микросхемы BIOS. Поэтому перенастройка чипсета для доступа к диапазону FFF00000h-FFFFFFFFh в данном примере не потребуется. Защита записи, реализуемая "южным мостом" Intel ICH8 построена по такой же схеме, как и в платформах предыдущих поколений, отличаются только адреса регистров.

Бит 0 этого регистра (бит BIOSWE, BIOS Write Enable) управляет разрешением записи в микросхему BIOS, 0=запрещена, 1=разрешена. Бит 1 того же регистра (бит BLE, BIOS Lock Enable) обеспечивает перехват несанкционированного выключения защиты. Если бит BLE=1, то при попытке установить бит BIOSWE=1 будет генерироваться прерывание SMI (System Management Interrupt) с вызовом специальной процедуры, входящей в состав BIOS. Причем, если BIOS при старте установит бит BLE=1, программно обнулить его чипсет не позволяет, режим перехвата будет выключен только после аппаратного сброса (по сигналу RESET). Данный механизм "защиты от снятия защиты" обычно не активируется разработчиками BIOS. Во всех материнских платах, исследованных автором, бит BLE=0, поэтому для снятия защиты записи достаточно установить бит BIOSWE=1, эта операция не будет перехвачена.

Микросхема Intel ICH8 также поддерживает защиту содержимого микросхемы BIOS, путем задания адресных диапазонов, защищенных от чтения и (или) записи.Теоретически, на базе данного механизма можно реализовать эффективную защиту, так как запрет программно включается процедурами BIOS при старте платформы, и может быть снят только при аппаратном сбросе. Но и этот механизм обычно не активируется разработчиками BIOS.

Читайте также: