Чем динамическая dram память отличается от статической sram

Обновлено: 04.07.2024

SRAM и DRAM - это режимы ОЗУ на интегральных схемах где SRAM использует транзисторы и защелки в конструкции, а DRAM использует конденсаторы и транзисторы. Их можно различать по-разному, например, SRAM сравнительно быстрее DRAM; следовательно, SRAM используется для кэш-памяти, а DRAM - для основной памяти.

RAM (оперативная память) это своего рода память, которой требуется постоянное питание для хранения данных в ней, при отключении питания данные будут потеряны, поэтому она известна как энергозависимая память. Чтение и запись в ОЗУ выполняется легко и быстро с помощью электрических сигналов.

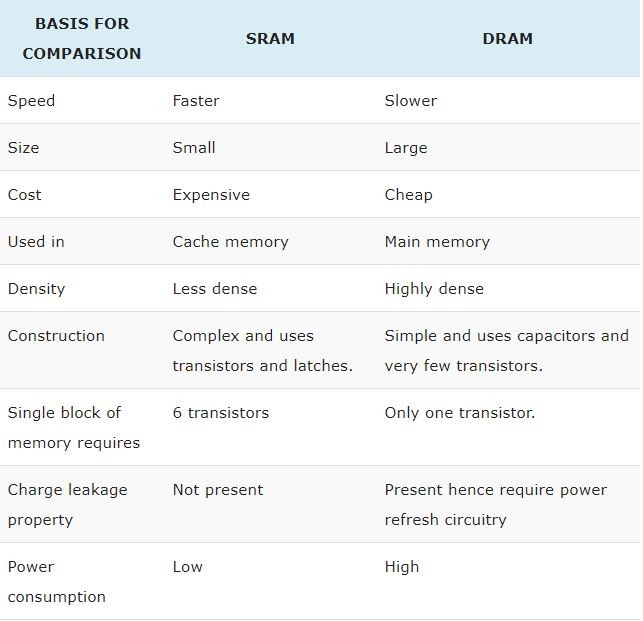

Сравнительная таблица

| Основа для сравнения | SRAM | DRAM |

|---|---|---|

| Скорость | Быстрее | Помедленнее |

| Размер | Маленький | Большой |

| Стоимость | Дорого | Дешево |

| Используется в | Кэш-память | Основная память |

| Плотность | Менее плотный | Очень плотный |

| строительство | Сложный и использует транзисторы и защелки. | Простой и использует конденсаторы и очень мало транзисторов. |

| Для одного блока памяти требуется | 6 транзисторов | Всего один транзистор. |

| Свойство утечки заряда | Нет | Присутствует, следовательно, требуется схема обновления питания |

| Потребляемая мощность | Низкий | Высоко |

Определение SRAM

SRAM (статическая память с произвольным доступом) составлен из CMOS технология и использует шесть транзисторов. Его конструкция состоит из двух инверторов с перекрестной связью для хранения данных (двоичных), подобных триггерам, и двух дополнительных транзисторов для контроля доступа. Это относительно быстрее, чем другие типы RAM, такие как DRAM. Он потребляет меньше энергии. SRAM может хранить данные до тех пор, пока на нее подается питание.

Работа SRAM для отдельной ячейки:

Для создания стабильного логического состояния четыре транзисторы (T1, T2, T3, T4) организованы перекрестно. Для генерации логического состояния 1 узелC1 высокий, и C2 низкий; в этом состоянии, Т1 а также Т4 выключены, и Т2 а также Т3 находятся на. Для логического состояния 0 соединение C1 низкий, и C2 в приоритете; в данном состоянии Т1 а также Т4 включены, и Т2 а также Т3 выключены. Оба состояния стабильны, пока не будет приложено напряжение постоянного тока (dc). SRAM адресная строка используется для размыкания и замыкания переключателя, а также для управления транзисторами T5 и T6, разрешающих чтение и запись. Для операции чтения сигнал подается на эту адресную строку, затем включаются T5 и T6, и значение бита считывается из строки B. Для операции записи сигнал используется для B битовая линия, и его дополнение применяется к B ’.

Определение DRAM

DRAM (динамическая память с произвольным доступом) Это также тип оперативной памяти, которая построена с использованием конденсаторов и небольшого количества транзисторов. Конденсатор используется для хранения данных, где битовое значение 1 означает, что конденсатор заряжен, а битовое значение 0 означает, что конденсатор разряжен.Конденсатор имеет тенденцию к разрядке, что приводит к утечке зарядов.

Динамический термин указывает на то, что заряды постоянно протекают даже при наличии непрерывной подаваемой мощности, что является причиной потребления большего количества энергии. Чтобы сохранить данные в течение длительного времени, их необходимо многократно обновлять, что требует дополнительных схем обновления. Из-за утечки заряда DRAM теряет данные даже при включении питания. DRAM доступен с большей емкостью и дешевле. Для единственного блока памяти требуется только один транзистор.

Работа типичной ячейки DRAM:

В момент чтения и записи битового значения из ячейки адресная строка активируется. Транзистор, присутствующий в схеме, ведет себя как переключатель, закрыто (позволяя току течь), если напряжение подается на адресную строку и открытым (ток не течет), если на адресную строку не подается напряжение. Для операции записи сигнал напряжения подается на разрядную шину, где высокое напряжение показывает 1, а низкое напряжение показывает 0. Затем сигнал используется в адресной строке, который позволяет передавать заряд конденсатору.

Когда адресная линия выбрана для выполнения операции чтения, транзистор включается, и заряд, накопленный на конденсаторе, подается на разрядную линию и на усилитель считывания. Усилитель считывания определяет, содержит ли ячейка логическую единицу или логику 2, путем сравнения напряжения конденсатора с опорным значением. Считывание ячейки приводит к разрядке конденсатора, который необходимо восстановить для завершения операции. Хотя DRAM в основном является аналоговым устройством и используется для хранения одного бита (т.е. 0,1).

Вывод

DRAM является потомком SRAM. DRAM разработана для преодоления недостатков SRAM; разработчики сократили количество элементов памяти, используемых в одном бите памяти, что значительно снизило стоимость DRAM и увеличило область хранения. Но DRAM медленная и потребляет больше энергии, чем SRAM, ее необходимо часто обновлять за несколько миллисекунд, чтобы сохранить заряд.

Если не хватает места на бумаге, вы стираете то, что вам больше не нужно. Оперативная память работает аналогично, когда ей требуется больше места для работы с временной информацией (то есть с запущенным программным обеспечением или программами). Большие листы бумаги позволяют вам набрасывать больше и больше идей за раз, прежде чем стирать. Больше оперативной памяти внутри компьютеров разделяют информацию прежде чем стереть аналогичным сопособом.

Оперативная память имеет различные формы (то есть физическое соединение с вычислительными системами или взаимодействие с ними), емкости (измеряемые в МБ или ГБ), скорости (измеряемые в МГц или ГГц) и архитектуры. Эти и другие аспекты важно учитывать при обновлении систем с ОЗУ, поскольку компьютерные системы (например, аппаратные средства, материнские платы) должны придерживаться строгих критериев.

- Компьютеры старого поколения вряд ли приспособят более современные типы технологий оперативной памяти

- Память ноутбука не помещается на десктопах (и наоборот)

- RAM не всегда обратно совместима

- Система не может смешивать и сочетать разные типы/поколения ОЗУ вместе

Есть кэш-память SRAM?

Приложения

Как и все ОЗУ, DRAM и SRAM являются энергозависимыми и поэтому не могут использоваться для хранения «постоянных» данных, таких как операционные системы, или файлов данных, таких как изображения и электронные таблицы..

Наиболее распространенным применением SRAM является кэш-память процессора (CPU). В спецификациях процессора это указано как кэш-память второго уровня или кэш-память третьего уровня. Производительность SRAM действительно высокая, но SRAM дорогая, поэтому типичные значения кэш-памяти L2 и L3 составляют от 1 до 8 МБ.

Синхронное динамическое ОЗУ с двойной скоростью передачи данных (DDR SDRAM)

- Время на рынке: с 2000 года по настоящее время

- Популярные продукты с использованием DDR SDRAM: память компьютера

DDR SDRAM работает как SDR SDRAM, только в два раза быстрее. DDR SDRAM способна обрабатывать две инструкции чтения и две записи за такт (следовательно, «двойной»). Функция DDR SDRAM аналогична, и имеет физические различия (184 контакта и один паз на разъеме) по сравнению с SDR SDRAM (168 контактов и две выемки на разъеме). DDR SDRAM также работает при низком стандартном напряжении (2,5 В от 3,3 В), предотвращая обратную совместимость с SDR SDRAM.

Структура и функции

Структуры ОЗУ обоих типов отвечают за их основные характеристики, а также за их плюсы и минусы. Техническое подробное объяснение того, как работают DRAM и SRAM, см. В этой технической лекции из Университета Вирджинии..

Динамическая RAM (DRAM)

Каждая ячейка памяти в микросхеме DRAM содержит один бит данных и состоит из транзистора и конденсатора. Транзистор функционирует как переключатель, который позволяет схемам управления на микросхеме памяти считывать конденсатор или изменять его состояние, в то время как конденсатор отвечает за удержание бита данных в форме 1 или 0..

С точки зрения функции, конденсатор похож на контейнер, в котором хранятся электроны. Когда этот контейнер заполнен, он обозначает 1, в то время как контейнер, пустой электронов, обозначает 0. Однако конденсаторы имеют утечку, которая приводит к тому, что они теряют этот заряд, и в результате «контейнер» становится пустым через несколько секунд. миллисекунды.

Таким образом, чтобы чип DRAM работал, ЦПУ или контроллер памяти должны перезарядить конденсаторы, заполненные электронами (и, следовательно, указать 1), перед тем как они разрядятся, чтобы сохранить данные. Для этого контроллер памяти считывает данные и затем переписывает их. Это называется обновлением и происходит тысячи раз в секунду в микросхеме DRAM. Здесь также происходит «Динамическое» в динамическом ОЗУ, поскольку оно относится к обновлению, необходимому для сохранения данных..

Из-за необходимости постоянно обновлять данные, что занимает много времени, DRAM медленнее.

Статическая RAM (SRAM)

Статическая RAM, с другой стороны, использует триггеры, которые могут находиться в одном из двух стабильных состояний, которые схема поддержки может считывать как 1 или 0. Триггер, хотя требуется шесть транзисторов, имеет преимущество: не нуждается в обновлении. Отсутствие необходимости постоянно обновлять делает SRAM быстрее, чем DRAM; однако, поскольку для SRAM требуется больше деталей и проводки, ячейка SRAM занимает больше места в микросхеме, чем ячейка DRAM. Таким образом, SRAM дороже не только потому, что на чип приходится меньше памяти (менее плотно), но и потому, что их сложнее изготовить.

скорость

Поскольку SRAM не нужно обновлять, обычно это происходит быстрее. Среднее время доступа DRAM составляет около 60 наносекунд, тогда как SRAM может дать время доступа всего 10 наносекунд..

Где мы используем SRAM?

Также есть статическая RAM (SRAM), которую не нужно обновлять. Хотя SRAM работает быстрее, чем DRAM, в ней используется больше транзисторов, и поэтому она более дорогая; он используется в основном для внутренних регистров ЦП и кэш-памяти.

SDRAM: Определение

Микросхемы SDRAM: Физическая организация и принцип работы

Важно заметить, что с динамической матрицей памяти связан особый буфер статической природы, именуемый «усилителем уровня» (SenseAmp), размер которого равен размеру одной строки, необходимый для осуществления операций чтения и регенерации данных, содержащихся в ячейках памяти. Поскольку последние физически представляют собой конденсаторы, разряжающиеся при совершении каждой операции чтения, усилитель уровня обязан восстановить данные, хранящиеся в ячейке, после завершения цикла доступа (более подробно участие усилителя уровня в цикле чтения данных из микросхемы памяти рассмотрено ниже).

Кроме того, поскольку конденсаторы со временем теряют свой заряд (независимо от операций чтения), для предотвращения потери данных необходимо периодически обновлять содержимое ячеек. В современных типах памяти, которые поддерживают режимы автоматической регенерации (в «пробужденном» состоянии) и саморегенерации (в «спящем» состоянии), обычно это является задачей внутреннего контроллера регенерации, расположенного непосредственно в микросхеме памяти.

Схема обращения к ячейке памяти в самом общем случае может быть представлена следующим образом:

В современных микросхемах SDRAM схема обращения к ячейкам памяти выглядит аналогично. Далее, в связи с обсуждением задержек при доступе в память (таймингов памяти), мы рассмотрим ее более подробно.

Микросхемы SDRAM: Логическая организация

Модули SDRAM: Организация

Модули памяти: Микросхема SPD

Тайминги памяти

Схема доступа к данным микросхемы SDRAM

1. Активизация строки

Повторная активизация какой-либо другой строки того же банка не может быть осуществлена до тех пор, пока предыдущая строка этого банка остается открытой (т.к. усилитель уровня, содержащий буфер данных размером в одну строку банка и описанный в разделе «Микросхемы SDRAM: Физическая организация и принцип работы», является общим для всех строк данного банка микросхемы SDRAM). Таким образом, минимальный промежуток времени между активизацией двух различных строк одного и того же банка определяется минимальным временем цикла строки (Row Cycle Time, tRC).

2. Чтение/запись данных

Возвращаясь к чтению данных, заметим, что существует две разновидности команды чтения. Первая из них является «обычным» чтением (READ), вторая называется «чтением с автоматической подзарядкой» (Read with Auto-Precharge, «RD+AP»). Последняя отличается тем, что после завершения пакетной передачи данных по шине данных микросхемы автоматически будет подана команда подзарядки строки (PRECHARGE), тогда как в первом случае выбранная строка микросхемы памяти останется «открытой» для осуществления дальнейших операций.

3. Подзарядка строки

Соотношения между таймингами

В заключение этой части, посвященной задержкам при доступе к данным, рассмотрим основные соотношения между важнейшими параметрами таймингов на примере более простых операций чтения данных. Как мы рассмотрели выше, в самом простейшем и самом общем случае — для пакетного считывания заданного количества данных (2, 4 или 8 элементов) необходимо осуществить следующие операции:

1) активизировать строку в банке памяти с помощью команды ACTIVATE;

2) подать команду чтения данных READ;

3) считать данные, поступающие на внешнюю шину данных микросхемы;

4) закрыть строку с помощью команды подзарядки строки PRECHARGE (как вариант, это делается автоматически, если на втором шаге использовать команду «RD+AP»).

Наконец, промежуток времени между четвертой операцией и последующим повтором первой операции цикла составляет «время подзарядки строки» (tRP).

В то же время, минимальному времени активности строки (от подачи команды ACTIVATE до подачи команды PRECHARGE, tRAS), по его определению, как раз отвечает промежуток времени между началом первой и началом четвертой операции. Отсюда вытекает первое важное соотношение между таймингами памяти:

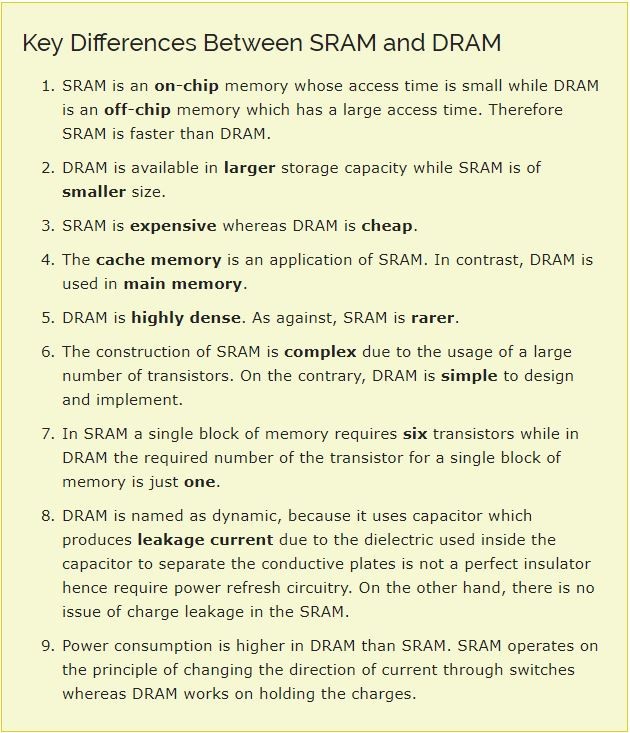

Разница между SRAM и DRAM

Статическая ОЗУ и динамическая ОЗУ отличаются друг от друга во многих контекстах, таких как скорость, емкость и т. Д. Эти различия возникают из-за различий в технике, используемой для хранения данных. DRAM использует один транзистор и конденсатор для каждой ячейки памяти, в то время как каждая ячейка памяти SRAM использует массив из 6 транзисторов. DRAM нуждается в обновлении, тогда как SRAM не требует обновления ячейки памяти.

Срам против диаграммы сравнения драма

определение драм и драм

DRAM обозначает динамическую оперативную память это широко используется в качестве основной памяти для компьютерной системы. DRAM требует 1 транзистор и 1 конденсатор для хранения 1 бита. Средство Каждая ячейка памяти в микросхеме DRAM содержит один бит данных и состоит из транзистора и конденсатора. Транзистор функционирует как переключатель, который позволяет схеме управления на микросхеме памяти считывать конденсатор или изменять его состояние, в то время как конденсатор отвечает за удержание бита данных в форме 1 или 0.

Как мы знаем, конденсатор похож на контейнер, в котором хранятся электроны. Когда этот контейнер заполнен, он обозначает 1, в то время как контейнер, пустой электронов, обозначает 0. Однако конденсаторы имеют утечку, которая приводит к тому, что они теряют этот заряд, и в результате «контейнер» становится пустым через несколько секунд. миллисекунды. И чтобы чип DRAM работал, процессор или контроллер памяти должны перезарядить конденсаторы, которые заполнены электронами (и, следовательно, указать 1), прежде чем они разрядятся, чтобы сохранить данные. Для этого контроллер памяти считывает данные и затем переписывает их. Это называется обновлением и происходит тысячи раз в секунду в микросхеме DRAM. Из-за необходимости постоянно обновлять данные, что занимает много времени, DRAM работает медленнее.

Наиболее распространенным применением DRAM, таким как DDR3, является энергозависимое хранилище для компьютеров. Хотя DRAM не такой быстрый, как SRAM, он по-прежнему очень быстрый и может подключаться непосредственно к шине ЦП. Типичные размеры DRAM составляют от 1 до 2 ГБ для смартфонов и планшетов и от 4 до 16 ГБ для ноутбуков.

SRAM обозначает статическую оперативную память, Обычно он используется для создания очень быстрой памяти, известной как кэш-память. SRAM требует 6 транзисторов для хранения 1 бита, и это намного быстрее по сравнению с DRAM. Статическая RAM использует совершенно другую технологию по сравнению с DRAM. В статической оперативной памяти форма триггера содержит каждый бит памяти. Триггер для ячейки памяти требует 4 или 6 транзисторов вместе с некоторой разводкой, но не требует обновления. Это делает статическое ОЗУ значительно быстрее, чем динамическое. В отличие от динамического ОЗУ (DRAM), которое хранит биты в ячейках, состоящих из конденсатора и транзистора, SRAM не требует периодического обновления.

Однако из-за того, что он содержит больше частей, ячейка статической памяти занимает на чипе намного больше места, чем ячейка динамической памяти. Таким образом, вы получаете меньше памяти на чип, и это делает статическую память намного дороже.

Это быстрее: Поскольку SRAM не нужно обновлять, обычно это происходит быстрее. Среднее время доступа DRAM составляет около 60 наносекунд, а SRAM может дать время доступа всего 10 наносекунд.

Наиболее распространенным применением SRAM является кэш-память процессора (CPU). В спецификациях процессора это указано как кэш-память второго уровня или кэш-память третьего уровня. Производительность SRAM действительно высокая, но SRAM дорогая, поэтому типичные значения кэша L2 и L3 составляют от 1 до 8 МБ.

статический баран против динамического баран

Основное различие между ними заключается в технологии, которая используется для хранения данных. Из-за этого ключевого различия возникают и другие различия. SRAM использует защелки для хранения данных (транзисторная схема), тогда как DRAM использует конденсаторы для хранения битов в виде заряда. SRAM использует обычную высокоскоростную технологию CMOS для строительства, тогда как DRAM использует специальные процессы DRAM для достижения оптимизированной высокой плотности. Динамические RAM имеют более простую внутреннюю структуру, чем SRAM.

Срам против скорости драма

SRAM обычно быстрее, чем DRAM так как у него нет циклов обновления. Поскольку каждая ячейка памяти SRAM состоит из 6 транзисторов, в отличие от ячейки памяти DRAM, которая состоит из 1 транзистора и 1 конденсатора, стоимость одной ячейки памяти в SRAM намного выше по сравнению с DRAM.

Я надеюсь, что теперь вы, возможно, поняли разницу между SRAM и DRAM. И что немаловажно, причина необходимости обновления ОЗУ сотню раз за такт. Тем не менее есть какие-либо вопросы запроса, не стесняйтесь обсуждать комментарии.

Читайте также: