Как добавить файл в проект quartus

Обновлено: 07.07.2024

В этой статье я расскажу, как создать новый проект в среде Altera Quartus II, как его откомпилировать и как прошить плату Марсоход.

В предыдущей статье "Введение в Verilog, урок первый" я писал о простых "программах" на языке Verilog. Мы изучили простое понятие провод ( wire ) и регистр ( reg ). Я хочу сделать совсем простой проект - соединить проводами кнопочки и светодиоды на плате Марсоход. Чтоб было не совсем скучно, добавим совсем простую логику в наш проект - две логические функции И и ИЛИ .

Соединить проводами - это не значит, что мы будем что-то паять. Мы напишем "программу" на языке Verilog, откомпилируем ее средствами среды разработки Quartus II и зашьем в плату Марсоход.

Вот какая у меня будет программа на Verilog:

module test_wires(

input wire key0,

input wire key1,

input wire key2,

input wire key3,

output wire led0,

output wire led1

);

assign led0 = key0 & key1;

assign led1 = key2 | key3;

endmodule

Светодиод led0 будет гореть если от кнопочек key0 И key1 будет приходить сигнал единица .

Светодиод led1 будет гореть если от кнопочек key2 ИЛИ key3 будет приходить сигнал единица .

Посмотрим, что у нас получится (внимание траффик - более 30 картинок - очень подробная инструкция).

Шаг 1.

Запускаем среду разработки Altera Quartus II Web Edition и выбираем пункт меню File/New Project Wizard . (Нажмите на картинку, чтобы посмотреть крупнее).

Шаг 2.

Вы видите начальный диалог мастера создания проекта. Этот диалог в несколько простых шагов поможет нам сделать наш первый проект. Сейчас нажмем кнопку Next - и пойдем дальше.

Шаг 3.

Сейчас нам нужно выбрать папку для нашего нового проекта и его название. Выберите себе любую пустую папку. Я назвал наш проект lesson1 , вы можете использовать любое другое название.

Шаг 4.

Сейчас можно добавить в новый проект какие-то существующие файлы, модули, может быть из других проектов. Поскольку это наш первый проект, то пропускаем этот шаг. Нажимаем Next .

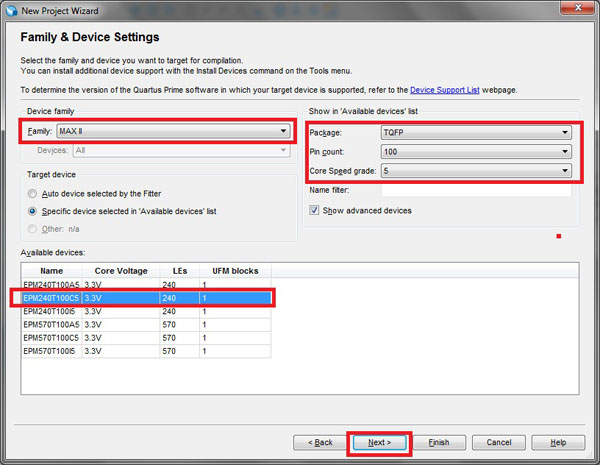

Шаг 5.

Вот здесь пожалуйста внимательнее. Нужно выбрать тип микросхемы CPLD или FPGA , для которой будет делаться проект. Конечно этот шаг тоже можно пропустить и сделать это назначение позже. Я предлагаю делать выбор сейчас. На плате Марсоход стоит микросхема ПЛИС (CPLD) EPM240T100C5. Вот ее и выбираем. После того, как выбрали - нажимаем Next .

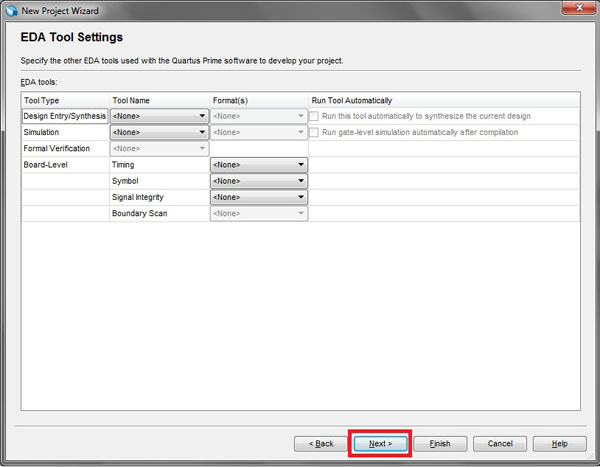

Шаг 6.

Здесь можно выбрать дополнительные программные инструменты, например, для симуляции проекта, мы пропускаем этот шаг. Нажимаем кнопку Finish . Наш проект создан. Теперь нужно добавить в него файлы, описывающие логику проекта.

Шаг 7.

Заходим в меню File/New и видим вот такой диалог. Здесь нам нужно решить какой именно файл мы собираемся создать, какого типа. Вы можете выбрать Block diagram/Schematic file - тогда логику проекта будем рисовать в виде схемы. Запустится специальный графический редактор и можно будет вставить в проект разные логические элементы, триггера, регистры, счетчики, сумматоры, мультиплексоры и много еще чего. Потом все эти элементы соединяются проводками - они буквально "рисуются" в этом графическом редакторе. Очень удобно. Я расскажу об этом как нибудь в другой раз. Сейчас в этом диалоге мы можем выбрать создание файла на языках описания аппаратуры: AHDL, VHDL, Verilog и других. Я выбираю Verilog - пункт списка Verilog HDL File .

Шаг 8.

Вот наш новый файл создан! Здесь мы будем набирать текст нашей программы.

Шаг 9.

Вот я набрал текст программы и теперь нужно его сохранить в каком нибудь файле. По умолчанию сейчас имя файла Verilog1.v - его можно поменять на любое другое имя файла.

Шаг 10.

Выбираем пункт меню File/Save As .

Шаг 11.

Вот появился диалог позволяющий задать имя записываемого файла. Я предпочитаю давать имена файлов по названию модулей, описанных в них. Конечно это не обязательно, вы можете выбрать себе любое другое имя файла. Сейчас я хочу задать имя файла test_wires.v

Шаг 12.

Файл записан. Вы можете видеть наше имя файла на закладке.

Шаг 13.

Вот здесь пожалуйста внимательней. Сейчас мы скажем среде программирования Quartus II, что этот наш текущий файл test_wires.v является самым главным файлом проекта. Попробую объяснить. Проект всегда включает в себя самый главный модуль, который может включать в себя многие другие модули в других файлах. Сейчас мы явно скажем, кто у нас тут самый главный . Заходим в меню Project/Set As Top Level Entity . Все - готово.

Шаг 14.

Пожалуй можно пробовать компилировать наш проект. Видите кнопочку треугольничек на панели инструментов?.Ну или можно зайти в меню Processing/Start Compilation .

Пожалуй перед компиляцией сделаем еще одну очень важную настройку нашего проекта.

Шаг 15.

Выберем пункт меню Assignments/Device . Здесь можно задать многие параметры компиляции проекта, связанные конкретно с чипом.

Шаг 16.

Появился вот такой диалог - на нем куча всяких настроек. Например можно выбрать тип микросхемы, для которой будет делаться компиляция проекта. Мы уже выбрали микросхему раньше. Сейчас можете проверить - должно быть EPM240T100C5. Нас же сейчас интересует кнопка Device and Pin Options . Нажмем ее.

Шаг 17.

Появился еще более страшный диалог. Не пугайтесь. Выбираем закладку Unused Pins .

Шаг 18.

Сейчас нам нужно сделать очень важную настройку . Мы должны сказать компилятору, что делать с неиспользуемыми ножками микросхемы. Поясню. В написанной нами программе всего 4 входа подключенных к кнопочкам, и два выхода, подключенных к светодиодам. Итого наш проект будет использовать 6 контактов микросхемы ПЛИС. А у нее, например всего 80 контактов, которые мы можем использовать по своему разумению. Компилятор подключит 6 контактов, а что делать с остальными? По умолчанию все неиспользуемые контакты микросхемы подключаются к нулю по питанию. Конечно все зависит от печатной платы, куда впаяна микросхема. Если на плате, например ошибочно, неиспользуемый контакт микросхемы подключен к питанию платы, то произойдет короткое замыкание. Не очень приятно. Что нибудь может сгореть на плате. Поэтому я всегда устанавливаю эту настройку. Я ставлю As input tri-stated . Это обозначает, что неиспользуемые входы будут входами с высоким входным сопротивлением. Это обезопасит микросхему и плату.

Шаг 19.

Вот теперь компилируем!

Шаг 20.

Мы видим, что проект успешно откомпилирован! Поздравляю!

Тем не менее, это еще не все. Пожалуйста обратите внимание на Warnings - предупреждения, а особенно на Critical Warnings - критические предупреждения. Я вообще, всегда рекомендую внимательно читать предупреждения компилятора. Конечно, хорошо бы знать английский язык, но я думаю вы довольно быстро освоитесь. Посмотрим, что же нам выдал компилятор?

Шаг 21.

Читаем: " Critical Warning: No exact pin location assignments for 6 pins of a total 6 pins ".

Это обозначает, что в проекте всего было 6 контактов и всем шести контактам не были сделаны назначения по расположению на чипе. На самом деле компилятор выполнил свою работу, но расположил контакты как попало, как ему было удобно. Так дело не пойдет. У нас уже есть плата Марсоход и кнопочки присоединены к конкретным ножкам микросхемы. Светодиоды так же подключены на плате. Точное расположение контактов нужно смотреть на схеме нашей платы

. Нам нужно сказать компилятору куда подключать какую ногу микросхемы.Шаг 22.

Выберем пункт меню Assignments/Assignment Editor .

Шаг 23.

В открывшемся окне делаем нужные нам назначения согласно схеме нашей платы. В колонке To вписываем имя входа или выхода. В колонке Assignment Name выбираем из списка нужную нам настройку Location . В колонке Value вписываем номер контакта микросхемы - его смотрим в PIN OUT файле или на схеме платы.

Шаг 24.

Вот теперь можете компилировать проект и все будет нормально!

Шаг 25.

После успешной компиляции проекта его можно зашить в чип платы Марсоход. Для этого запускаем программу программатора. Выберите пункт меню Tools/Programmer .

Шаг 26.

Вот так выглядит окно программатора на экране. Видите в левом верхнем углу " No Hardware " - похоже программатор еще не установлен. Подключите программатор к вашему ПК. Если у вас UsbBlaster, то нужно будет установить драйвера к нему. Они находятся в папке C:/Altera/91/Quartus/Drivers . Если у вас ByteBlaster (в том числе сделанный самостоятельно), то драйвера не нужны. Теперь нажмите кнопку Hardware Setup .

Шаг 27.

В открывшемся диалоговом окне выберите тип программатора, который у вас установлен.

Шаг 28.

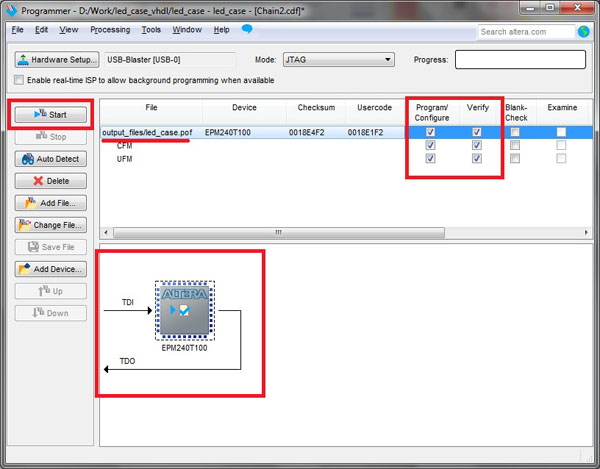

Теперь нужно проставить нужные "галочки" в Program/Configure и Verify . Строка CFM имеет отношение к собственно программированию ПЛИС. Строка UFM имеет отношение к программированию флеш памяти внутри чипа ПЛИС. Их можно программировать по отдельности.

Колонка Verify обозначает проверить после прошивки.

Шаг 29.

Нужно подключить плату Марсоход к UsbBlaster и подать питание на плату.

Шаг 30.

Нажимаем в програматоре кнопку Start - и, все готово! Плата Марсоход прошита с только что откомпилированным проектом! Урра!

После прошивки, подключаем питание и пробуем, что у нас получилось:

Обратите внимание, как все работает.

Левые две кнопки key3, key2 объединены в логическую функцию ИЛИ . Именно поэтому светодиод led1 гаснет только если нажать обе эти кнопки.

Правые две кнопки key1 , key0 объединены в логическую функцию И . Именно поэтому светодиод led0 гаснет если нажать хотя бы одну кнопку.

Вот так это все работает.

Теперь у нас есть инструкция, по которой вы сможете создавать свои проекты. Возможно она показалась вам длинной и занудной. Может быть сложной. На самом деле, дальше будет гораздо проще. Если у вас будет хотя бы один готовый проект (а их у нас на сайте уже много), то достаточно просто открыть его и удалить лишнее. Очень много времени обычно уходит на разные настройки. Если брать готовые проекты за основу, то там все настройки уже сделаны и тратить время на это уже не нужно.

Подготовим и загрузим в ПЛИС фирмы Altera проект из среды разработки Quartus II.

Для работы нам понадобится:

- ПЛИС фирмы Altera; ;

- компьютер со средой разработки Quartus II.

1 Назначение выводов в проекте Quartus II

Первым делом необходимо назначить используемые выводы ПЛИС. В меню Assignements Device… выбираем ПЛИС, в которую вы собираетесь «залить» проект. В группе Device Family нужно выбрать семейство, к которому относится ваша ПЛИС. В поле Available devices выберите модель вашей ПЛИС. У меня, например, это Cyclone II, модель EP2C5T144C8.

Выбираем семейство и модель ПЛИС в окне Device

В группе Show in "Available devices" list можно отсортировать устройства по типу корпуса (Package) или по количеству выводов (Pin count), чтобы быстрее найти вашу модель ПЛИС.

Определение состояния незадействованных выводов

После того как указали модель ПЛИС, закрываем окно Device, нажав кнопку OK.

Если вы хотите, чтобы синтезатор сам назначил функции выводам, то можно ничего больше не делать. А для того, чтобы вручную назначить выводы ПЛИС, идём в меню Assignements Pin Planner или нажимаем сочетание клавиш Ctrl+Shift+N .

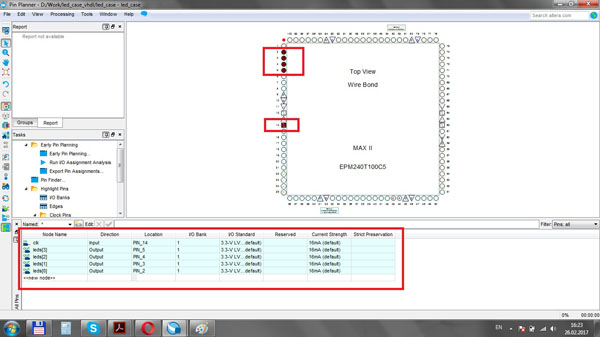

Запуск инструмента назначения выводов Pin Planner

Запустится инструмент назначения выводов Pin Planner. Внизу отображается список используемых в вашем проекте пинов ввода-вывода с соответствующими именами Node Name.

Инструмент Pin Planner и список вводов-выводов проекта ПЛИС

Теперь в столбце Location нужно задать номера выводов. Дважды кликаем на соответствующей ячейке и выбираем номер вывода, или же вводим с клавиатуры номер. Номера выводов будут зависеть от вашей макетной платы. Например, в моей плате тактовый импульс CLK, согласно мануалу, на 17 выводе, а выходам OUT1…OUT5 я назначу свободные выводы 94, 97, 100, 103 и 93.

Назначаем соответствие выводов ПЛИС сигналам проекта

После того, как все выводы были определены, окно планировщика пинов Pin Planner можно закрыть. Теперь скомпилируйте проект: Processing Start Compilation или Ctrl+L .

Запускаем полную перекомпиляцию проекта в Quartus II

2 Установка драйвера для программатора USB Blaster

Подключим программатор USB Blaster к компьютеру (если у вас его нет, то можно приобрести на Али-Экспресс). При первом подключении необходимо установить драйвер. Он устанавливается стандартным образом, и находится в директории Квартуса, в папке drivers: C:\altera\13.0sp1\quartus\drivers

Установка драйвера для программатора USB Blaster

После установки драйвера, программатор будет отображаться в диспетчере устройств как Altera USB-Blaster.

3 Загрузка прошивки через интерфейс JTAG

ПЛИС фирмы Altera поддерживают несколько режимов программирования. Сначала рассмотрим загрузку прошивки в ПЛИС через интерфейс JTAG. Подключите программатор к разъёму JTAG на плате с ПЛИС.

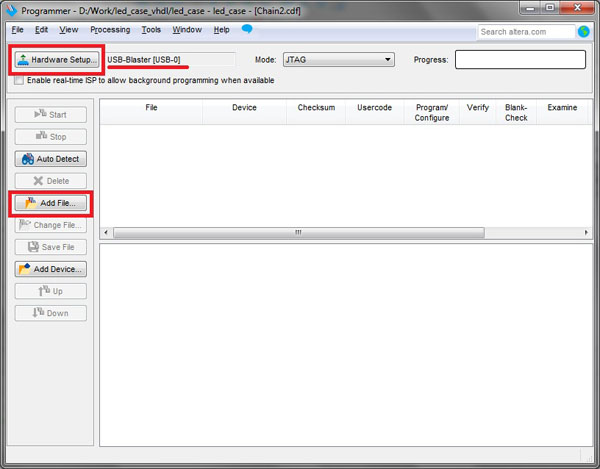

Запустим инструмент для программирования: Tools Programmer.

Добавим программатор. Для этого нажмём кнопку Hardware Setup… и в выпадающем списке выберем подключённый USB Blaster. Закроем окно Hardware Setup.

Настройка программатора

В окне программатора Programmer нажмите кнопку Auto Detect, чтобы Quartus попытался автоматически определить подключённую ПЛИС и файл прошивки *.sof.

Файл прошивки создаётся Квартусом по умолчанию при компиляции и сохраняется в директории output_files, если не задано иное.

В окне Programmer выберите режим JTAG, установите галочку Program/Configure и нажмите кнопку Start. Прошивка будет записана в память ПЛИС.

Загрузка прошивки в ПЛИС через JTAG

4 Загрузка прошивки в режиме Active Serial

Чтобы прошивка сохранилась в ПЗУ, запишем прошивку в режиме Active Serial.

Подключите кабель программатора к разъёму AS или Active Serial. Запустите программу прошивки: Tools Programmer.

Выберите режим Mode Active Serial. Соглашайтесь при ответе на уточняющий вопрос.

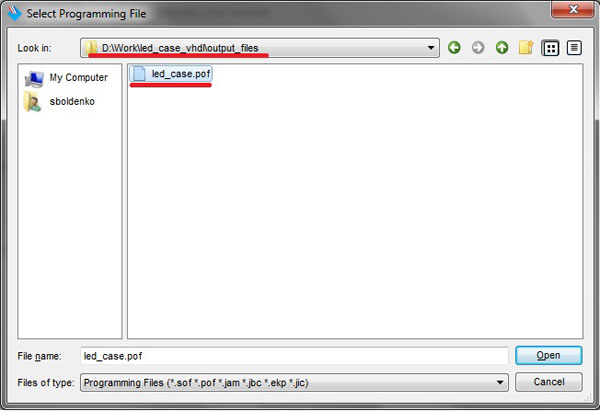

Добавим файл прошивки, нажав кнопку Add File… В поддиректории проекта output_files найдите файл с расширением .pof.

Добавляем файл прошивки в режиме Active Serial

После открытия файла прошивки, установите галочки Program/Configure и, по желанию,остальные.

Загрузка прошивки в ПЛИС в режиме Active Serial

Обратите внимание на тип конфигурационной памяти в столбце Device: он должен соответствовать типу памяти, которая установлена у вас на плате.

Проверка с помощью осциллографа результата прошивки ПЛИС

Для преобразования и настройки файлов прошивок существует инструмент, который доступен из меню File Convert Programming Files….

Самыми популярными языками описания цифровой аппаратуры являются VHDL и Verilog. В этой статье я постараюсь сравнить синтаксис двух этих языков на примере "бегущего огонька", архивы проектов будут прикреплены в конце статьи. Для полного понимания описываемых процессов настоятельно рекомендую ознакомиться с предыдущими статьями цикла:

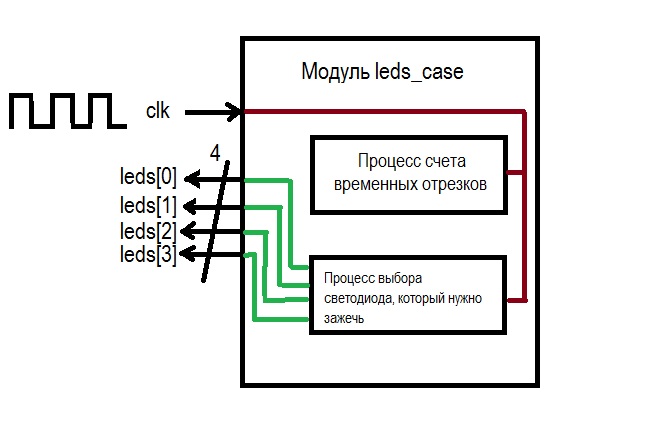

Рассмотрим структуру создаваемого модуля "бегущего огонька", который назовем leds_case. В модуле будет один вход для тактового сигнала clk, и четыре выхода (четырехбитная шина) для светодиодов.

В модуле будет всего два процесса, которые будут выполнятся параллельно друг-другу, синхронно с тактовым сигналом clk. В первом процессе сделаем счетчик, который бы считал равные временные отрезки, через которые происходит переключение с одного светодиода на другой. Во втором процессе реализуем функцию, которая бы включала поочередно светодиоды по истечению определенного промежутка времени заданного счетчиком из первого процесса.

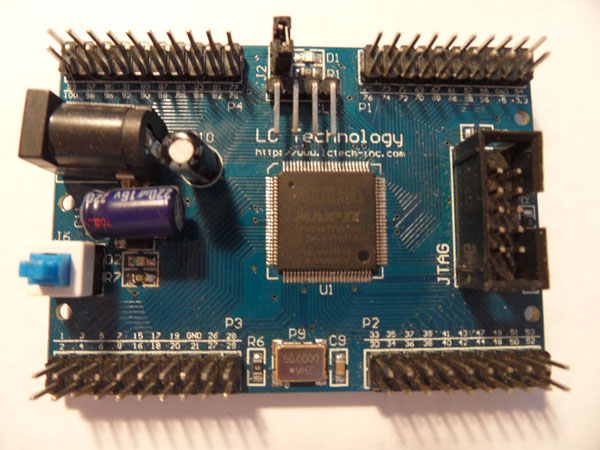

Чтобы не быть голословным, реализуем данный модуль на отладочной плате от ALTERA с CPLD семейства MAX II.

Плата прошивается по JTAG программатором USB BLASTER.

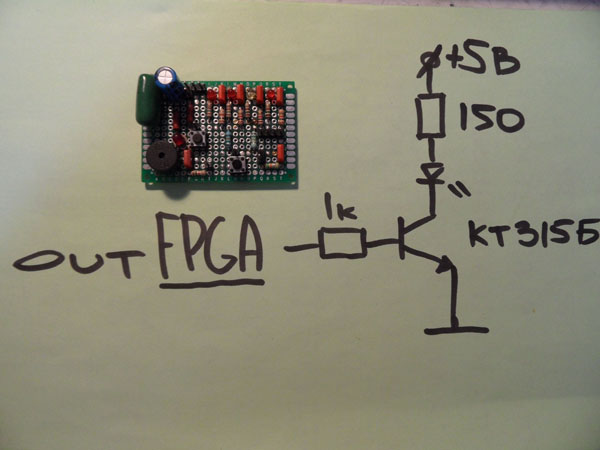

Т.к. на самой отладочной плате нет светодиодов, то я нашел у себя старую плату, на которой было 4 светодиода включенных по схеме на рисунке ниже.

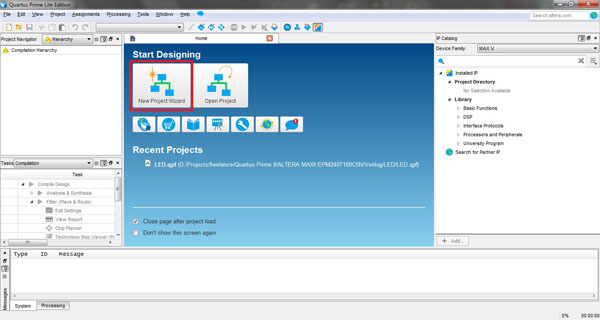

Итак, теперь создадим новый проект в среде Quartus II, которую можно скачать на официальном сайте Altera. Запускаем среду, для создания нового проекта кликаем на New Project Wizard (на картинке обведено красным).

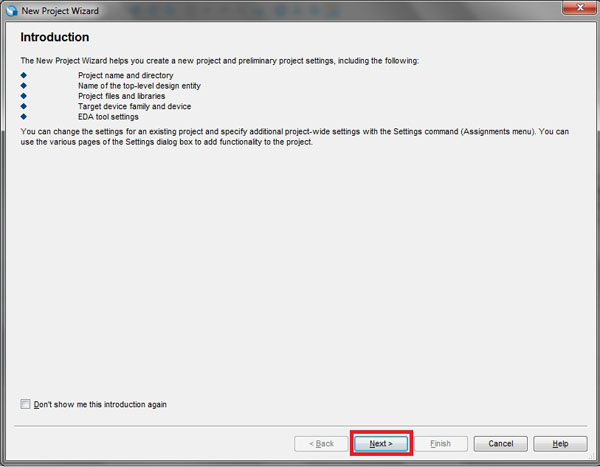

В этом окне среда нам сообщает какие операции нужно совершить для создания проекта. Пропускаем.

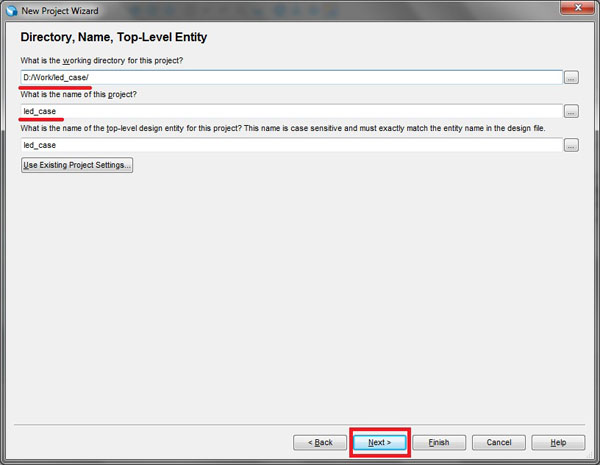

В этом диалоговом окне указываем рабочую папк, где будет храниться проект, а также название топового модуля. Т.к. у нас в проекте запланирован всего один модуль, то назовем его led_case.

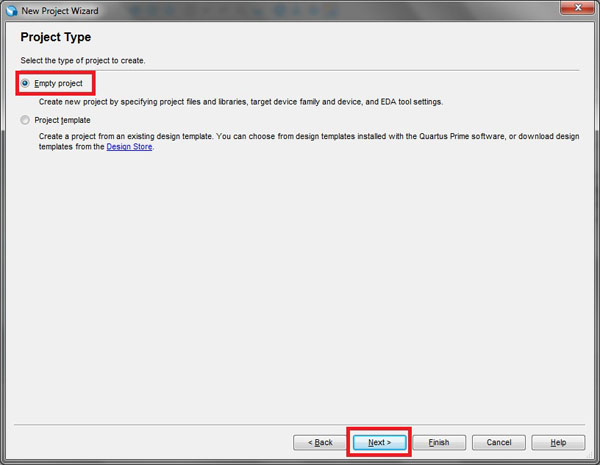

Далее выбираем Empty project, тем самым подтверждаем создание абсолютно чистого проекта.

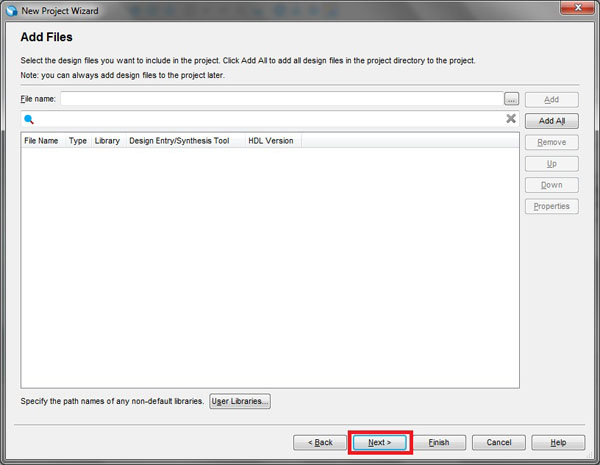

В следующем диалоговом окне нам предлагают подключить файлы проекта, но так-как нам нечего подключать, то пропустим этот шаг.

В этом диалоговом окне выбираем микросхему, которую мы будем программировать. Выбираем параметры соответствующие микросхеме на нашей плате: семейство MAX II корпус TQFP и количество ножек 100. Немного остановимся на параметре Core Speed grade - это параметр характеризующий время задержки прохождения сигнала между внутренними соединениями в ПЛИС. Проект созданный для ПЛИС со speed grade 5 без проблем заработает на ПЛИС со speed grade 10, но проект созданный для ПЛИС со speed grade 10 не будет адекватно работать, если вообще разведется, на ПЛИС со speed grade 5. Как определить speed grade? Очень просто: в названии микросхемы EPM240T100C5 последняя цифра 5 и есть значение speed grade.

В этом окне среда предлагает нам указать на средства симуляции, в которых мы бы хотели отлаживать код, но т.к. код будет простым, то пропустим этот шаг. Средства симуляции разберем в другой статье.

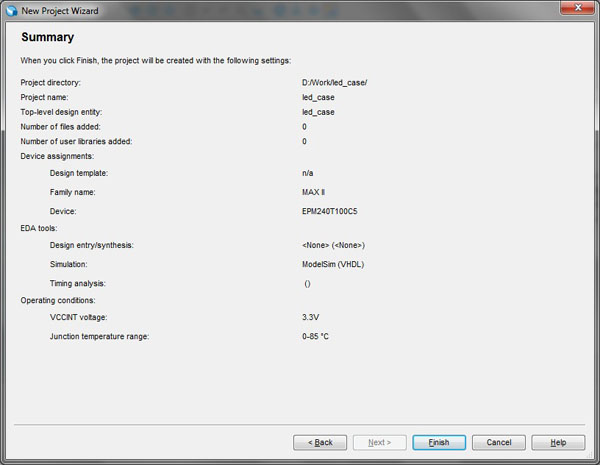

В этом диалоговом окне среда показывает нам суммарные сведения о выбранных нами настройках.

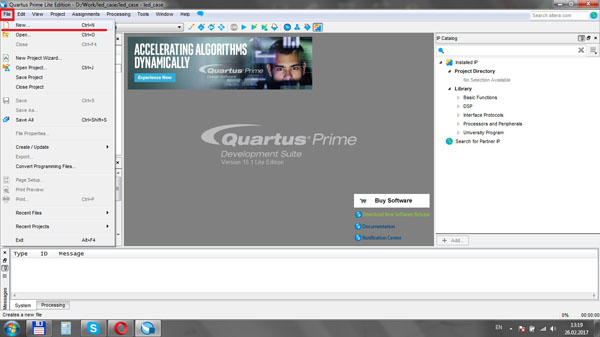

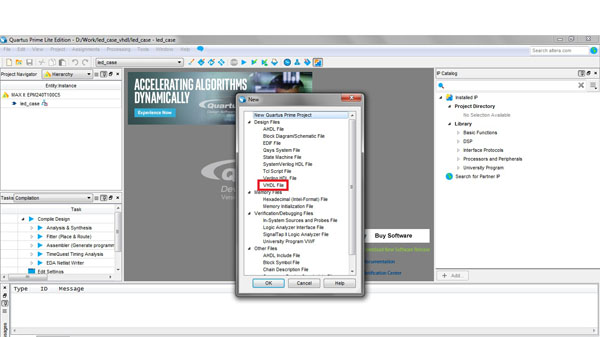

Для начала напишем модуль на VHDL. Cоздадим VHDL файл. Выберем File -> New

В появившемся окне выбираем VHDL file.

Теперь напишем код и разберем его.

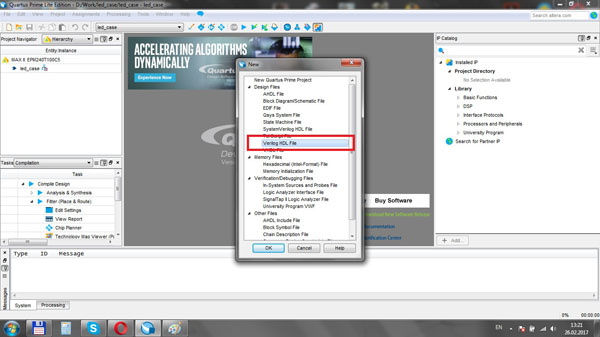

Теперь напишем код выполняющий ту же самую функцию но на Verilog, для этого создадим новый проект, но новый модуль создадим как Verilog file

// Как видите, никаких библиотек на математику и типы данных мы не подключаем

Как Вы можете убедится оба языка очень похожи и мнение о том, что синтаксис Verilog подобен высокоуровневому языку С сильно преувеличено. Как я и говорил ранее, выбор на чем писать сугубо личный и основан исключительно на популярности языка, так что о том что для читателя является достоинством, а что недостатком я доверю решать самому читателю. А вообще, никто не мешает Вам выучить и Verilog и VHDL. В одном проекте допускается то, что один модуль может быть написан на Verilog, а другой на VHDL. Хочется еще сказать пару слов о переносимости проектов на разные ПЛИС: если Вы не используете специфические ресурсы ПЛИС, такие как аппаратные умножители, множители частоты и т.д., то перенести проект на другую ПЛИС не составит труда. Например наш проект не использует ничего кроме таблиц соответствия и триггеров, и следовательно его можно перенести не только на ПЛИС из другого семейства, но и на ПЛИС другой фирмы!

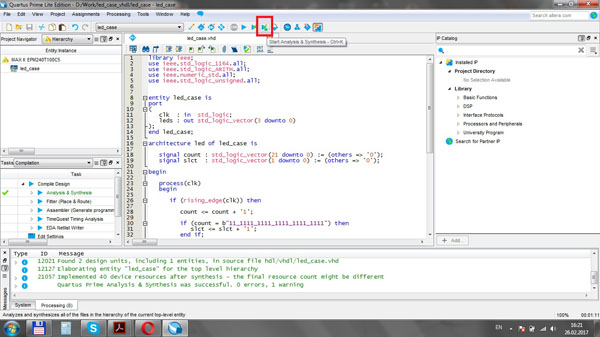

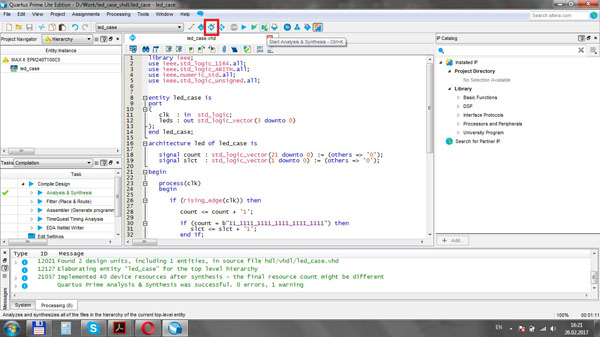

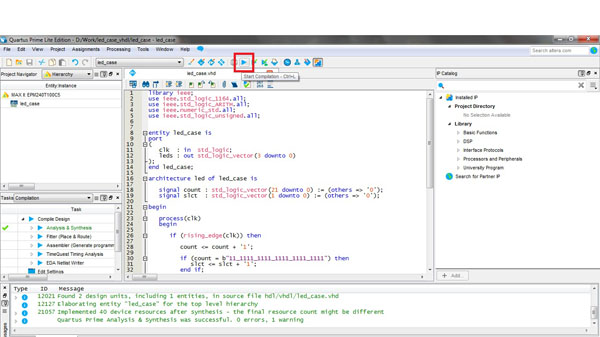

Раз у нас уже есть прошивка, то самое время научиться прошивать плату и посмотреть на результаты своих трудов, но перед этим давайте сначала синтезируем проект. Для этого кликаем на значок вверху экрана. Должен предупредить сразу, что синтез проекта для ПЛИС требует ресурсов компьютера и занимает долго времени, по сравнению с микроконтроллерами.

После того как синтез проекта выполнится успешно, настало время присвоить портам из модуля реальные пины ПЛИС. Для этого кликнем на значок Pin Planning вверху экрана.

Перед нами откроется изображение нашей микросхемы. Мы видим на какие ножки мы можем "повесить" наши сигналы, но перед тем как это сделать расскажу Вам, что есть три типа пинов: обычные пины входа/выхода, на них можно заводить переферию (у ПЛИС есть несколько банков, куда входят группы пинов), пины тактирования, на них заводится тактовая частота, а еще есть пины сброса (reset) на которые заводится сигнал сброса. У меня на плате нет кнопки reset'а, поэтому эти пины трогать не будем. На PIN_14 нужно завести сигнал clk, чтобы затактировать банк с пинами номер 1. PIN_2, PIN_3, PIN_4, PIN_5 входят в банк пинов номер 1, и следовательно на них "повесим" выходную шину управления светодиодами. После того, как Вы назначили все требуемые пины, просто закройте окно Pin Planner'а, все результаты сохранятся.

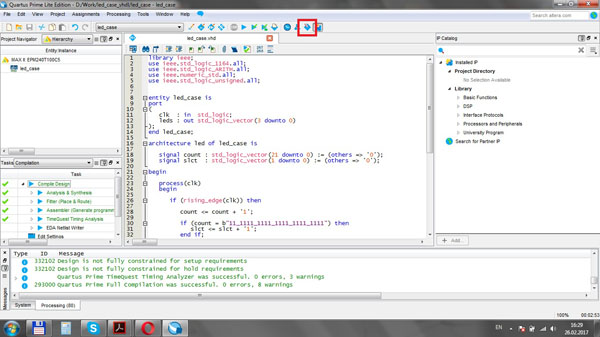

После того как мы все правильно присвоили, сделаем синтез и имплементацию проекта нажав на соответствующую иконку вверху экрана.

После успешной сборки проекта откроем утилиту Programmer в верней части экрана, в которой можно прошить нашу ПЛИС.

В появившемся окне Programmera нажмите Hardware Setup, если Ваш программатор не определился автоматически. Драйвера на программатор должны установиться автоматически, но если по каким-то причинам этого не произошло, то их можно найти в папке с установленной средой. Нажмите Add File, чтобы загрузить сгенерированный средой файл прошивки.

Файл прошивки можно найти в папке output_files вашего проекта. Выбираем его.

Далее появится вот такое окошко. Внизу мы можем увидеть, что ПЛИС выбрана правильно. Чтобы запрограммировать нашу ПЛИС ставим галочки Program/Configure и Verify и жмем Start. Если все сделано правильно, то статус-бар Progress станет зеленым и будет отображать 100%.

Добавлю видео работы прошивки, чтобы Вы убедились что все написанное правда, а так же два варианта прошивки: на Verilog и на VHDL. Спасибо за внимание.

Программа на vhdl уже есть, теперь расскажу что с ней делать.

При запуске программа предлагает создать новый проект или открыть существующий

выбираем “Create a New Project”, если уже зашли в программу, тогда

File->New Project Wizard…

Не думаю что вы увидите что-то новое: выбор каталога и название проекта, добавление файлов к проекту, выбор чипа, финиш.

Теперь нужно создать файл (основываясь на статью Что такое VHDL. Простейший пример создания логического элемента в ПЛИС) создаем файл vhdl

File->New->VHDL File

Копипастим в него весь код, сохраняем. Теперь указываем программе что это главный файл проекта

Project->Set as Top-Level Entity

(без этого ничего не получится).

Можно компилировать.

Processing->Start Compilation (Ctrl+L)

либо фиолетовый треугольник вверху на панели.

Выводится отчет о компиляции, если все хорошо – идем дальше.

Перед прошивкой нужно назначить соответствие между сигналами входа и выхода в проекте и пинами чипа. Заходим

Assignments->Pins

Внизу видим название наших сигналов. В поле Location просто выбираем нужный пин, либо клацнуть два раза на пине (где изображение микросхемы) и выбрать нужное имя.

В ПЛИС все пины равноправные, могут быть как входом, так и выходом, или двунаправленные. Некоторые выводы могут быть источником глобального клока, глобальным сбросом или глобальным enable. В нашем проекте есть все эти виды сигналов, конечно не обязательно их подключать к этим пинам, но в большем проекте где тактовый сигнал идет на много модулей это будет эффективней, поскольку физически они так построены внутри чипа. Также в зависимости от конкретной микросхемы можно выбирать нагрузочную способность вывода, подключать подтягивающий резистор или защитный диод.

После назначений выводов можно приступать к программированию

Tools->Programmer

Когда проект состоит из множества файлов (а это чаще всего), тогда удобно чтобы главным был файл схемотехнического описания. Создаем

File->New->Block Diagram/Schematic File

Сохраняем, назовем его main.

Чтобы добавить туда наш vhdl файл, надо создать с него символьный файл. Для этого выбираем vhdl файл, жмем

File->Create/Update->Create Symbol File for Current File

Возвращаемся к нашему main.bdf, жмем Symbol Tool (кнопочка в виде логического элемента И).

Программа создала 2 символьных файла, поскольку в vhdl два entity. Собственно то что мы описали в entity мы видим в образе этого символьного файла, некий черный ящик у которого есть входы и выходы, а то что в нем происходит описано в architecture.

Теперь добавляем пины, даем им какое-то осмысленное название.

Должно получится что-то типа этого:

Здесь можно добавлять различные интересные штуки, такие как микросхемы стандартной логики или различные сумматоры, мультиплексоры и т. д.

Также в зависимости от используемой микросхемы ее «фарш» в виде памяти, или как в семействе MAX II, встроенный генератор на 5 МГц. Все добавляется и соединяется проводами, причем в чипе оно также будет физически соединено.

Сохраняем файл, снова проделываем

Project->Set as Top-Level Entity

Теперь мои замечания и доработки проекта.

Здесь 2 entity будут лишними, поскольку в схемотехническом файле можно соединять все блоки привычным образом и одни сигнал пускать куда угодно.

Также здесь не нужно подключать библиотеку, т. к. она не используется (в ней описаны сигналы типа std_logic).

Наш файл упрощается до такого

теперь внесу свои 5 копеек в код

Отмазки

Исторически сложилось что я описал создание проекта в Квартусе по первой статье о vhdl, хотя лучше было бы по второй. Но так как у меня были замечания по этой статье, а также хотелось Ultrin'у показать как создается проект в Квартусе я решил ничего не переделывать.

Читайте также: