Как называют контроллер управляющий обменом между внешним устройством и памятью эвм

Обновлено: 07.07.2024

Из вышесказанного следует, что в состав современных ЭВМ входят многочисленные и разнообразные по выполняемым функциям, принципам действия и характеристикам периферийные устройства (ПУ), которые по назначению можно разделить на две группы:

• внешние запоминающие устройства, предназначенные для хранения больших объемов информации;

• устройства ввода-вывода, обеспечивающие связь машины с внешней средой путем ввода информации в ЭВМ и вывода ее из ЭВМ, ее регистрации и отображения.

Необходимость обеспечения автоматического распознавания и реакции ядра ЭВМ на многообразие ситуаций, возникающих в ПУ (готовность устройства, различные неисправности и т.п.), привела к использованию унифицированных форматов данных при обмене информацией между ПУ и ЭВМ. Преобразование унифицированных форматов данных в индивидуальные, приспособленные для отдельных ПУ, производится в самих ПУ.

Контроллер жесткого диска позволяет:

• поддерживать формат данных на диске, совместимый с форматом данных ЭВМ;

• поддерживать не только стандартные, но также и задаваемые пользователем типы НЖМД;

• генерировать прерывание IRQ14;

• осуществлять поиск требуемых цилиндров (если головки находятся не на требуемом цилиндре, то инициируется его поиск, а затем выполняется чтение или запись информации);

• производить автоматическое переключение головок накопителя (при обнаружении конца дорожки во время мультисекторной передачи адаптер выбирает следующую дорожку, а при обнаружении конца цилиндра – следующий цилиндр, после чего продолжается выполнение команды);

• обнаруживать ошибки в считываемой информации и корректировать пакеты ошибок;

• управлять последовательностью размещения секторов на дорожке (чередованием);

• производить обмен данными с ЦП и ОЗУ в режиме программного ввода-вывода;

• производить внутреннюю диагностику аппаратуры адаптера.

Получив команды и данные от ЦП через программно-доступные регистры, адаптер НЖМД начинает выполнять операцию. Передача в ОЗУ компьютера считываемых данных, а также прием из ОЗУ записываемых данных происходят через буферную память адаптера НЖМД, необходимую для согласования временных параметров обмена данными между НЖМД и системной шиной, а также для коррекции информации (при записи информации на диск формируется циклический избыточный код контроля ошибок, который приписывается в конец каждого поля идентификатора сектора и каждого поля данных).

Рассмотрим состав и назначение регистров контроллера НЖМД.

Регистр данных 1F0h используется при выполнении операции чтения или записи сектора в программном режиме ввода-вывода. Этот регистр недоступен, пока не начнется операция чтения или записи.

Регистр ошибок 1F1h доступен только на чтение. Он определяет состояние контроллера после выполнения операции. Состояние этого регистра действительно в следующих случаях:

• после выполнения команды, если установлен бит “Error” в регистре состояния;

• после выполнения команды “Диагностика” или после выполнения внутренней диагностики контроллера по системному сбросу.

Коды регистра ошибок в диагностическом режиме:

Значения битов регистра ошибок после выполнения команды (устанавливаются в 1 при наличии соответствующей ошибки):

• бит 3 не используется;

• бит 5 не используется;

В регистр стартового цилиндра 1F1h (доступный только для записи) заносится уменьшенный в 4 раза по отношению к действительному номер цилиндра, начиная с которого адаптер осуществляет запись данных.

В регистр номера сектора 1F3h загружается стартовый номер сектора при операциях чтения-записи. После обработки каждого сектора в этот регистр заносится номер следующего сектора, подлежащего обработке. Регистр доступен для чтения/записи. После выполнения команды он содержит номер последнего обработанного сектора.

Регистры младшего (1F4h) и старшего (1F5h) байтов номера цилиндра определяют стартовый цилиндр для выполнения команды. Регистр доступен для чтения/записи. После выполнения команды он содержит текущий адрес цилиндра.

Регистр выбора НЖМД и номера головки 1F6h, доступный для чтения/записи, определяет номер головки, выбранный НЖМД (1 или 2), и размер сектора.

Регистр состояния 1F7h, доступный только для чтения, отображает состояние адаптера и НЖМД. Значения битов регистра состояния (возникновение определенного состояния индицируется установкой соответствующего бита в 1):

Регистр команд 1F7h используется для загрузки выполняемой команды (загрузка команды должна производиться только после того, как подготовлены и записаны в регистры 1F1h-1F6h все необходимые для ее выполнения данные). Регистр управления 3F6h доступен только для записи. Значения битов этого регистра следующие:

• бит 0 не используется;

• биты 4-7 не используются.

Статьи к прочтению:

Лекция 279.Прямой доступ к памяти

Похожие статьи:

В современных компьютерах используются два основных способа организации передачи данных между памятью и периферийными устройствами: программно-управляемая передача ( PIO , Programmed Input - Output ) и прямой доступ к памяти ( DMA , Direct Memory Access ).

Программно-управляемая передача данных осуществляется при непосредственном участии и под управлением процессора. Например, при пересылке блока данных из периферийного устройства в оперативную память процессор должен выполнить следующую последовательность шагов:

сформировать начальный адрес области обмена в оперативной памяти;

занести длину передаваемого массива данных в один из внутренних регистров, который будет играть роль счетчика;

выдать команду чтения информации с устройства; при этом на шину адреса от процессора выдается адрес устройства, на шину управления – сигнал чтения данных, а считанные данные заносятся во внутренний регистр процессора;

выдать команду записи информации в оперативную память; при этом на шину адреса от процессора выдается адрес ячейки оперативной памяти, на шину управления – сигнал записи данных в память, а на шину данных выставляются данные из регистра процессора, в который они были помещены при чтении с устройства;

модифицировать регистр, содержащий адрес оперативной памяти;

уменьшить счетчик длины массива на длину переданных данных;

если переданы не все данные, то повторить шаги 3-6, в противном случае закончить обмен.

Как видно, программно-управляемый обмен ведет к нерациональному использованию мощности микропроцессора, который вынужден выполнять большое количество относительно простых операций, приостанавливая работу над основной программой. При этом действия, связанные с обращением к оперативной памяти и к периферийному устройству, обычно требуют удлиненного цикла работы микропроцессора из-за их более медленной по сравнению с микропроцессором работы, что приводит к еще более существенным потерям производительности.

Альтернативой программно-управляемому обмену служит прямой доступ к памяти – способ быстродействующего подключения внешнего устройства, при котором оно обращается к оперативной памяти, не прерывая работы процессора. Такой обмен происходит под управлением отдельного устройства – контроллера DMA (или КПДП).

Рис. 13. Обмен данными в режиме прямого доступа к памяти

Перед началом работы контроллер DMA необходимо инициализировать: занести начальный адрес области памяти, с которой производится обмен, и длину передаваемого массива данных. В дальнейшем по сигналу запроса прямого доступа контроллер фактически является посредником между устройством и памятью – выполняет все те действия, которые обеспечивал микропроцессор при программно-управляемой передаче.

Последовательность действий контроллера DMA при запросе на прямой доступ к памяти со стороны устройства ввода-вывода следующая:

Принять запрос на DMA (сигнал DRQ) от устройства.

Сформировать запрос к процессору на захват шин (сигнал HRQ).

Принять сигнал от процессора (HLDA), подтверждающий факт перевода микропроцессором своих шин в третье состояние.

Сформировать сигнал, сообщающий устройству ввода-вывода о начале выполнения циклов прямого доступа к памяти (DACK).

Сформировать на шине адреса компьютера адрес ячейки памяти, предназначенной для обмена.

Выработать сигналы, обеспечивающие управление обменом (IOR, MW для передачи данных из устройства в оперативную память и IOW, MR для передачи данных из оперативной памяти на устройство).

Уменьшить значение в счетчике данных на длину переданных данных.

Проверить условие окончания сеанса прямого доступа (обнуление счетчика данных, снятие сигнала запроса на DMA ). Если условие окончания не выполнено, изменить адрес в регистре текущего адреса на длину переданных данных и повторить шаги 5-8.

Прямой доступ к памяти позволяет осуществлять параллельно во времени выполнение процессором программы и обмен данными между периферийным устройством и оперативной памятью.

Режим DMA для шины ISA .

DMA -контроллер шины ISA имеет 16 каналов DMA , из которых 7 могут использоваться процессором. Каждому каналу DMA присвоен 16-битный регистр адреса и 16-битный регистр счётчика. Для начала передачи данных на контроллере выставляются значения адреса в памяти и счётчика данных, а также действие (чтение/запись). Затем контроллер передает устройству сигнал начала процедуры передачи, по окончании которой посылает на процессор прерывание. Контроллер исполняет роль посредника при передаче.

Режим DMA для шины PCI .

В отличие от шины ISA , архитектура шины PCI не предусматривает отдельного контроллера DMA , и при этом любое устройство, подключённое к шине PCI , может послать запрос на получение статуса «мастера шины» ( Bus Master ) и возможности считывать/записывать значения в память напрямую.

Когда PCI -устройство запрашивает у контроллера шины данных полный доступ, контроллер (обычно это южный мост в системных платах) проверит возможность предоставления доступа (только одно устройство может иметь статус Bus Master ). Когда устройство получает доступ, оно передает команды считывания/записи на шину PCI , а контроллер в свою очередь переводит поток данных на контроллер доступа к памяти.

PIO обычно используется в ЭВМ для операций ввода-вывода отдельных байт (слов), которые выполняются быстрее, чем при DMA , так как исключаются потери времени на инициализацию контроллера DMA , а в качестве основного способа осуществления операций ввода-вывода используют DMA . Например, в современных компьютерах обмен между накопителями на магнитных дисках и оперативной памятью происходит в режиме прямого доступа.

Организация ЭВМ на основе общей шины является сдерживающим фактором для повышения производительности компьютера. Следует отметить, что даже при использовании прямого доступа к памяти процессор полностью не освобождается от управления операциями ввода-вывода. Он обеспечивает инициализацию контроллера ПДП, а также взаимодействует с ним по некоторым управляющим линиям. Более того, во время операции передачи данных интерфейс оказывается занятым, а связь процессора с оперативной памятью – блокированной.

Это существенно сказывается на эффективности работы ЭВМ, особенно в тех случаях, когда в вычислительной системе используется большое количество высокоскоростных внешних устройств. Для решения этой проблемы в состав высокопроизводительных компьютеров иногда включают специализированные процессоры ввода-вывода, способные полностью разгрузить основной процессор от управления операциями обмена с внешними устройствами.

Одним из важнейших устройств компьютера является центральный процессор (CPU — англ, central processing unit, что переводится как «центральное вычислительное устройство»). Именно от типа процессора и его характеристик в первую очередь зависит производительность компьютерной системы в целом.

Центральный процессор — это устройство компьютера, предназначенное для выполнения арифметических и логических операций над данными, а также координации работы всех устройств компьютера.

Современные центральные процессоры для персональных компьютеров выполняются в виде отдельных микросхем и называются микропроцессорами. В дальнейшем будем считать понятия «микропроцессор» и «процессор» равнозначными.

Схема состава микропроцессора показана на рисунке 1.

Основным элементом микропроцессора является ядро, от которого зависит большинство характеристик самого процессора. Ядро представляет собой часть микропроцессора, содержащую его основные функциональные блоки и осуществляющую выполнение одного потока команд.

Современные процессоры могут иметь более одного ядра, т.е. могут быть многоядерными. Многоядерные процессоры способны выполнять одновременно несколько потоков команд. Основная причина перехода к многоядерным процессорам была вызвана тем, что повышение производительности микропроцессоров путем дальнейшего наращивания тактовой частоты достигло физического предела в связи с очень высоким уровнем тепловыделения и энергопотребления. Производительность многоядерного процессора увеличивается за счет распараллеливания обработки данных между несколькими ядрами. Визуальное представление процессора показано на рисунке 2.

Ядро процессора помещается в корпус (пластмассовый или керамический) и соединяется проводками с металлическими ножками (выводами), с помощью которых процессор присоединяется к системной плате компьютера. Количество выводов и их расположение определяют тип процессорного интерфейса (разъема). Каждая системная плата ориентирована на один определенный тип разъема

Арифметико-логическое устройство (АЛУ) выполняет все математические и логические операции.

Управляющее устройство (УУ) обеспечивает выполнение процессором последовательности команд программы.

Набор регистров — ячейки памяти внутри процессора, используемые для размещения команд программы и обрабатываемых данных.

Кэш-память (кэш) — сверхбыстрая память, хранящая содержимое наиболее часто используемых ячеек оперативной памяти, а также части программы, к которым процессор обратится с наибольшей долей вероятности. Процессор в первую очередь пытается найти нужные данные именно в кэш-памяти, а если их там не оказывается, обращается к более медленной оперативной памяти. Кэш-память делится на два или три уровня, которые обозначаются LI, L2 и L3 (чаще всего уровней два).

Сопроцессор — элемент процессора, выполняющий действия над числами с плавающей запятой.

Характеристики микропроцессора Тактовая частота. Для каждой выполняемой процессором команды требуется строго определенное количество единиц времени (тактов). Тактовые импульсы формируются генератором тактовой частоты, установленным на системной плате. Чем чаще они генерируются, тем больше команд процессор выполняет за единицу времени, т. е. тем выше его быстродействие. Тактовая частота обычно выражается в мегагерцах. 1 МГц равен 1 миллиону тактов в секунду. Первые модели процессоров Intel ( i 8008 x ) работали с тактовыми частотами, меньшими 5 МГц. Сегодня тактовая частота последних процессоров превышает 3 ГГц (1 ГГц = 1000 МГц). Внутренняя архитектура процессора, как и тактовая частота, также влияет на работу процессора, поэтому два CPU с одинаковой тактовой частотой не обязательно будут тратить одинаковое время на выполнение одной команды. Если, например, микропроцессору Intel 80286 требовалось 20 тактов, чтобы выполнить команду умножения двух чисел, то Intel 80486 или старше мог выполнить это же действие за один такт. Некоторые процессоры способны выполнять более одной команды за 1 такт. Их называют суперскалярными. Различают внутреннюю и внешнюю тактовую частоту. Внешняя тактовая частота — это частота, с которой процессор обменивается данными с оперативной памятью компьютера. Как уже было сказано выше, она формируется генератором тактовых импульсов (кварцевым резонатором).

Внутренняя тактовая частота — это частота, с которой происходит работа внутри процессора. Именно это значение указывается в прайс-листах фирм, продающих процессоры.

МПС - сложная система, включающая в себя большое количество различных устройств. Основой ее является микропроцессор . Связь устройств ЭВМ между собой осуществляется с помощью сопряжений, которые в вычислительной технике называются интерфейсами.

Интерфейс - это совокупность программных и аппаратных средств, предназначенных для передачи информации между компонентами ЭВМ и включающих в себя электронные схемы, линии, шины и сигналы адресов, данных и управления, алгоритмы передачи сигналов и правила интерпретации сигналов устройствами.

В широком смысле интерфейс включает также механическую часть (совместимость по типоразъемам) и вспомогательные схемы, обеспечивающие электрическую совместимость устройств по уровням логических сигналов, входным и выходным токам и т. д.

Подробное изучение интерфейсов и системных шин не входит в задачи данного курса. Поэтому эти вопросы мы будем рассматривать лишь с точки зрения общего представления об организации работы микропроцессорной системы и принципах взаимодействия составляющих ее устройств.

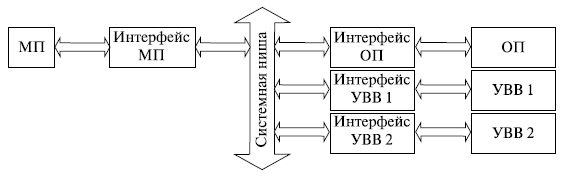

Основным способом организации МПС является магистрально-модульный (рис. 8.1): все устройства, включая и микропроцессор , представляются в виде модулей, которые соединяются между собой общей магистралью . Обмен информацией по магистрали удовлетворяет требованиям некоторого общего интерфейса, установленного для магистрали данного типа. Каждый модуль подключается к магистрали посредством специальных интерфейсных схем.

Рис. 8.1. Магистрально-модульный принцип построения микропроцессорной системы

На интерфейсные схемы модулей возлагаются следующие задачи:

- обеспечение функциональной и электрической совместимости сигналов и протоколов обмена модулей и системной магистрали;

- преобразование внутреннего формата данных модуля в формат данных системной магистрали и обратно;

- обеспечение восприятия единых команд обмена информацией и преобразование их в последовательность внутренних управляющих сигналов.

Эти интерфейсные схемы могут быть достаточно сложными. Обычно они выполняются в виде специализированных микропроцессорных БИС. Такие схемы принято называть контроллерами.

Контроллеры обладают высокой степенью автономности, что позволяет обеспечить параллельную во времени работу периферийных устройств и выполнение программы обработки данных микропроцессором.

Кроме того, предварительно буферируя данные, контроллеры обеспечивают пересылку сразу для многих слов, расположенных по подряд идущим адресам, что позволяет использование так называемого "взрывного"

( burst ) режима работы шины - 1 цикл адреса и следующие за ним многочисленные циклы данных.

Недостатком магистрально-модульного способа организации ЭВМ является невозможность одновременного взаимодействия более двух модулей, что ставит ограничение на производительность компьютера.

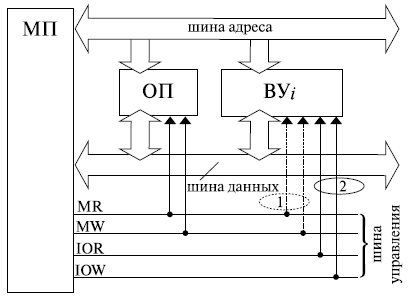

Взаимодействие микропроцессора с оперативной памятью (ОП) и внешними устройствами (ВУ) проиллюстрировано на рис. 8.2.

Рис. 8.2. Взаимодействие микропроцессора с оперативной памятью и внешними устройствами

Микропроцессор формирует адрес внешнего устройства или ячейки оперативной памяти и вырабатывает управляющие сигналы - либо IOR/ IOW при обращении на чтение/запись из внешнего устройства, либо MR/MW для чтения/записи из оперативной памяти.

Для обмена информацией с внешними устройствами в МП имеются только 2 команды:

- команда ввода IN AX , DX записывает в регистр AX число из внешнего устройства, адрес которого находится в регистре DX ; при этом вырабатывается сигнал IOR ( INput/OUTput Read ).);

- команда вывода OUT DX , AX выводит информацию из регистра AX во внешнее устройство, адрес которого находится в регистре DX ; при этом вырабатывается сигнал IOW ( INput/OUTput Write ).

Сигналы IOR/ IOW формируются при выполнении только этих команд.

Формирование сигналов MR/MW происходит в командах, для которых операнд и/или приемник результата располагаются в оперативной памяти, например, ADD [EBX] , AX .

В связи с этим возможны два основных способа организации адресного пространства микропроцессорной системы:

- с общим адресным пространством внешних устройств и оперативной памяти;

- с независимыми адресными пространствами.

В первом случае к портам ввода/вывода можно обращаться как к ячейкам оперативной памяти. Достоинством такого подхода является возможность использовать различные режимы адресации при обращении к внешним устройствам, а также выполнять над содержимым портов ввода/вывода различные арифметико-логические операции . Но в то же время при этом сокращается емкость адресуемой ОП и снижается защищенность системы, так как она лишается дополнительных средств защиты, связанных с выполнением команд ввода/вывода (не работает поле IOPL регистра флагов ). К тому же нарушение в логике работы программы (формирование неверного адреса оперативной памяти) может привести к ложному срабатыванию внешнего устройства.

Если первый недостаток не столь существенен при современных объемах запоминающих устройств , то второй может весьма негативно сказаться на работе МПС. Возможность использования сложных режимов адресации при обращении к внешним устройствам для микропроцессорных систем на основе универсальных МП не столь важна. Поэтому в настоящее время при построении МПС предпочтение отдается второму подходу.

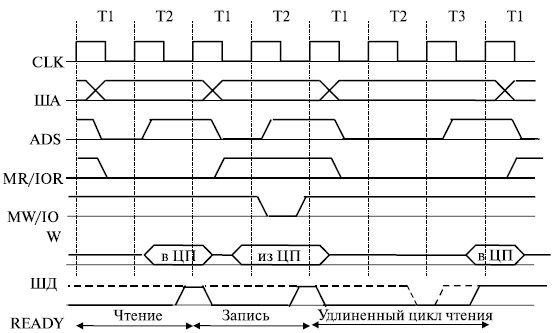

Рассмотрим особенности обмена информацией микропроцессора с внешними устройствами. Упрощенная временная диаграмма этого процесса представлена на рис. 8.3.

Рис. 8.3. Временная диаграмма обмена информацией между микропроцессором и внешним устройством

При таком обмене микропроцессор использует стандартный цикл шины длительностью 2 периода тактового генератора , начало которого определяется сигналом A DS шины.

Однако если в обмене задействованы относительно медленное внешнее устройство или оперативная память , которые не успевают завершить обмен в текущем цикле работы микропроцессора, то они сбрасывают сигнал READY , который проверяется микропроцессором в конце второго тактового сигнала цикла . При READY = 0 МП вставляет дополнительные такты ожидания в цикл шины, чтобы дать возможность внешнему устройству завершить операцию ввода/вывода. Однако сигнал неготовности внешнего устройства не может длиться более установленного времени (для шины ISA - 2,5 мкс), в противном случае генерируется прерывание по ошибке ввода/вывода. Это предотвращает зависание системы в случае, например, механического повреждения данного контакта.

В общем случае стандартный цикл шины при обмене уже включает несколько дополнительных тактов ожидания. При этом циклы обращения к памяти короче циклов обращения к портам ввода/вывода. Минимальная длительность цикла определяется чипсетом и может программироваться опциями BIOS Setup заданием тактов ожидания. Если ОП или внешнее устройство не нуждаются в дополнительных тактах, то их контроллеры выставляют на шину сигнал OWS , по которому дополнительные такты не вставляются.

Читайте также: