Как узнать логический адрес компьютера

Обновлено: 06.07.2024

Для адресации операндов в физическом адресном пространстве программы используют логическую адресацию. Процессор автоматически транслирует логические адреса в физические, выдаваемые затем на системную шину.

Архитектура компьютера различает физическое адресное пространство (ФАП) и логическое адресное пространство (ЛАП). Физическое адресное пространство представляет собой простой одномерный массив байтов, доступ к которому реализуется аппаратурой памяти по адресу, присутствующему на шине адреса микропроцессорной системы . Логическое адресное пространство организуется самим программистом исходя из конкретных потребностей. Трансляцию логических адресов в физические осуществляет блок управления памятью MMU .

В архитектуре современных микропроцессоров ЛАП представляется в виде набора элементарных структур: байтов, сегментов и страниц. В микропроцессорах используются следующие варианты организации логического адресного пространства:

- плоское (линейное) ЛАП: состоит из массива байтов, не имеющего определенной структуры; трансляция адреса не требуется, так как логический адрес совпадает с физическим;

- сегментированное ЛАП: состоит из сегментов - непрерывных областей памяти, содержащих в общем случае переменное число байтов; логический адрес содержит 2 части: идентификатор сегмента и смещение внутри сегмента; трансляцию адреса проводит блок сегментации MMU ;

- страничное ЛАП: состоит из страниц - непрерывных областей памяти, каждая из которых содержит фиксированное число байтов. Логический адрес состоит из номера (идентификатора) страницы и смещения внутри страницы; трансляция логического адреса в физический проводится блоком страничного преобразования MMU ;

- сегментно-страничное ЛАП: состоит из сегментов, которые, в свою очередь, состоят из страниц; логический адрес состоит из идентификатора сегмента и смещения внутри сегмента. Блок сегментного преобразования MMU проводит трансляцию логического адреса в номер страницы и смещение в ней, которые затем транслируются в физический адрес блоком страничного преобразования MMU .

Таким образом, основой получения физического адреса памяти служит логический адрес . В какой-то степени логическое адресное пространство , с которым имеет дело программист, можно сравнить со структурой книги, где аналогом сегмента выступает рассказ, страница книги соответствует странице ЛАП, а искомая информация - это некоторое слово . При этом если память организована как линейная, то номер искомого слова задается в явном виде и просто отсчитывается от начала книги. При сегментном представлении памяти искомое слово определяется его номером в заданном рассказе. Страничное представление памяти предполагает задание информации о слове в виде номера страницы в книге и номера слова на указанной странице. При сегментно-страничном представлении логический адрес слова задается номером слова в определенном рассказе. В этом случае по оглавлению книги определяется номер страницы, с которой начинается указанный рассказ. Затем, зная количество слов на странице и положение слова в рассказе, можно вычислить страницу книги и положение искомого слова на этой странице.

Формирование физического адреса в универсальном микропроцессоре при различных режимах работы

Микропроцессор способен работать в двух режимах: реальном и защищенном.

При работе в реальном режиме возможности процессора ограничены: емкость адресуемой памяти составляет 1 Мбайт, отсутствует страничная организация памяти, сегменты имеют фиксированную длину 2 16 байт .

Этот режим обычно используется на начальном этапе загрузки компьютера для перехода в защищенный режим.

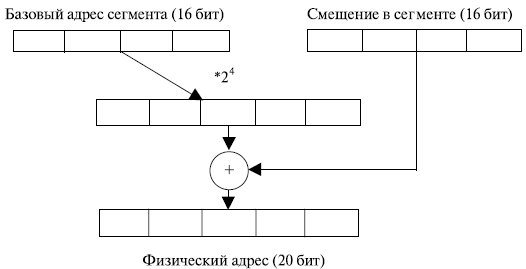

В реальном режиме сегментные регистры процессора содержат старшие 16 бит физического адреса начала сегмента. Сдвинутый на 4 разряда влево селектор дает 20-разрядный базовый адрес сегмента. Физический адрес получается путем сложения этого адреса с 16-разрядным значением смещения в сегменте, формируемого по заданному режиму адресации для операнда или извлекаемому из регистра EIP для команды (рис. 3.1). По полученному адресу происходит выборка информации из памяти.

Наиболее полно возможности микропроцессора по адресации памяти реализуются при работе в защищенном режиме. Объем адресуемой памяти увеличивается до 4 Гбайт, появляется возможность страничного режима адресации. Сегменты могут иметь переменную длину от 1 байта до 4 Гбайт.

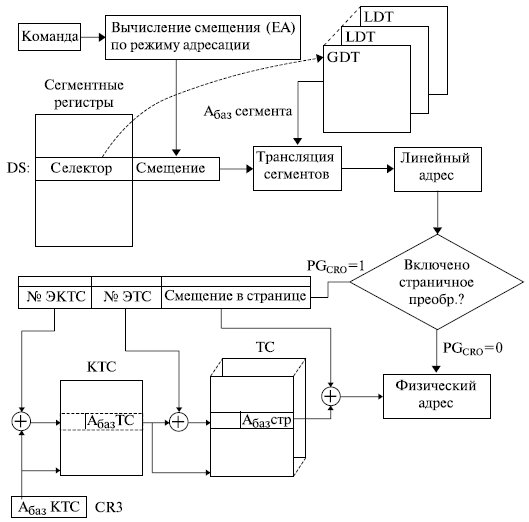

Общая схема формирования физического адреса микропроцессором , работающим в защищенном режиме, представлена на рис. 3.2.

Как уже отмечалось, основой формирования физического адреса служит логический адрес . Он состоит из двух частей: селектора и смещения в сегменте.

Селектор содержится в сегментном регистре микропроцессора и позволяет найти описание сегмента (дескриптор) в специальной таблице дескрипторов. Дескрипторы сегментов хранятся в специальных системных объектах глобальной ( GDT ) и локальных ( LDT ) таблицах дескрипторов. Дескриптор играет очень важную роль в функционировании микропроцессора , от формирования физического адреса при различной организации адресного пространства и до организации мультипрограммного режима работы. Поэтому рассмотрим его структуру более подробно.

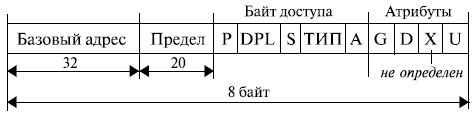

Сегменты микропроцессора , работающего в защищенном режиме, характеризуются большим количеством параметров. Поэтому в универсальных 32-разрядных микропроцессорах информация о сегменте хранится в

Рис. 3.2. Формирование физического адреса при сегментно-страничной организации памяти

Структура дескриптора сегмента представлена на рис. 3.3.

Мы будем рассматривать именно структуру, а не формат дескриптора, так как при переходе от микропроцессора i286 к 32-разрядному МП расположение отдельных полей дескриптора потеряло свою стройность и частично стало иметь вид "заплаток", поставленных с целью механического увеличения разрядности этих полей.

32-разрядное поле базового адреса позволяет определить начальный адрес сегмента в любой точке адресного пространства в 2 32 байт (4 Гбайт).

Поле предела (limit) указывает длину сегмента (точнее, длину сегмента минус 1: если в этом поле записан 0, то это означает, что сегмент имеет длину 1) в адресуемых единицах, то есть максимальный размер сегмента равен 2 20 элементов.

Величина элемента определяется одним из атрибутов дескриптора битом G ( Granularity - гранулярность , или дробность):

Таким образом, сегмент может иметь размер с точностью до 1 байта в диапазоне от 1 байта до 1 Мбайт (при G = 0 ). При объеме страницы в 2 12 = 4 Кбайт можно задать объем сегмента до 4 Гбайт (при G = l ):

Так как в архитектуре IA-32 сегмент может начинаться в произвольной точке адресного пространства и иметь произвольную длину, сегменты в памяти могут частично или полностью перекрываться.

Бит размерности ( Default size ) определяет длину адресов и операндов, используемых в команде по умолчанию:

Конечно, этот бит предназначен не для обычного пользователя, а для системного программиста, применяющего его, например, для отметки сегментов для сбора"мусора" или сегментов, базовые адреса которых нельзя модифицировать. Этот бит доступен только программам, работающим на высшем уровне привилегий. Микропроцессор в своей работе его не меняет и не использует.

Байт доступа определяет основные правила обращения с сегментом.

Бит присутствия P (Present) показывает возможность доступа к сегменту. Операционная система (ОС) отмечает сегмент, передаваемый из оперативной во внешнюю память , как временно отсутствующий, устанавливая в его дескрипторе P = 0 . При P = 1 сегмент находится в физической памяти. Когда выбирается дескриптор с P = 0 (сегмент отсутствует в ОЗУ ), поля базового адреса и предела игнорируются. Это естественно: например, как может идти речь о базовом адресе сегмента, если самого сегмента вообще нет в оперативной памяти? В этой ситуации процессор отвергает все последующие попытки использовать дескриптор в командах, и определяемое дескриптором адресное пространство как бы"пропадает".

Возникает особый случай неприсутствия сегмента. При этом операционная система копирует запрошенный сегмент с диска в память (при этом, возможно, удаляя другой сегмент), загружает в дескриптор базовый адрес сегмента, устанавливает P = 1 и осуществляет рестарт той команды, которая обратилась к отсутствовавшему в ОЗУ сегменту.

Двухразрядное поле DPL ( Descriptor Privilege Level ) указывает один из четырех возможных (от 0 до 3) уровней привилегий дескриптора, определяющий возможность доступа к сегменту со стороны тех или иных программ (уровень 0 соответствует самому высокому уровню привилегий).

Бит обращения A (Accessed) устанавливается в"1" при любом обращении к сегменту. Используется операционной системой для того, чтобы отслеживать сегменты , к которым дольше всего не было обращений.

Пусть, например, 1 раз в секунду операционная система в дескрипторах всех сегментов сбрасывает бит А. Если по прошествии некоторого времени необходимо загрузить в оперативную память новый сегмент, места для которого недостаточно, операционная система определяет"кандидатов" на то, чтобы очистить часть оперативной памяти, среди тех сегментов, в дескрипторах которых бит А до этого момента не был установлен в"1", то есть к которым не было обращения за последнее время.

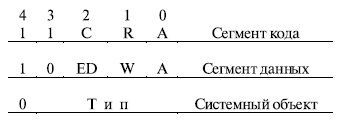

Поле типа в байте доступа определяет назначение и особенности использования сегмента. Если бит S ( System - бит 4 байта доступа) равен 1, то данный дескриптор описывает реальный сегмент памяти. Если S = 0 , то этот дескриптор описывает специальный системный объект , который может и не быть сегментом памяти, например, шлюз вызова, используемый при переключении задач, или дескриптор локальной таблицы дескрипторов LDT . Назначение битов <3. 0> байта доступа определяется типом сегмента (рис. 3.4).

В сегменте кода: бит подчинения, или согласования, C ( Conforming ) определяет дополнительные правила обращения, которые обеспечивают защиту сегментов программ. При C = 1 данный сегмент является подчиненным сегментом кода. В этом случае он намеренно лишается защиты по привилегиям. Такое средство удобно для организации, например, подпрограмм, которые должны быть доступны всем выполняющимся в системе задачам. При C = 0 - это обычный сегмент кода; бит считывания R ( Readable ) устанавливает, можно ли обращаться к сегменту только на исполнение или на исполнение и считывание, например, констант как данных с помощью префикса замены сегмента. При R = 0 допускается только выборка из сегмента команд для их выполнения. При R = 1 разрешено также чтение данных из сегмента.

Запись в сегмент кода запрещена. При любой попытке записи возникает программное прерывание .

В сегменте данных:

- ED ( Expand Down) - бит направления расширения. При ED = 1 этот сегмент является сегментом стека и смещение в сегменте должно быть больше размера сегмента. При ED = 0 - это сегмент собственно данных (смещение должно быть меньше или равно размеру сегмента);

- бит разрешения записи W(Writeable) . При W = 1 разрешено изменение сегмента. При W = 0 запись в сегмент запрещена, при попытке записи в сегмент возникает программное прерывание .

В случае обращения за операндом смещение в сегменте формируется микропроцессором по режиму адресации операнда, заданному в команде. Смещение в сегменте кода извлекается из регистра - указателя команд EIP .

Сумма извлеченного из дескриптора начального адреса сегмента и сформированного смещения в сегменте дает линейный адрес (ЛА).

Если в микропроцессоре используется только сегментное представление адресного пространства, то полученный линейный адрес является также и физическим.

Если помимо сегментного используется и страничный механизм организации памяти , то линейный адрес представляется в виде двух полей: старшие разряды содержат номер виртуальной страницы , а младшие смещение в странице. Преобразование номера виртуальной страницы в номер физической проводится с помощью специальных системных таблиц: каталога таблиц страниц (КТС) и таблиц страниц (ТС). Положение каталога таблиц страниц в памяти определяется системным регистром CR3. Физический адрес вычисляется как сумма полученного из таблицы страниц адреса физической страницы и смещения в странице, полученного из линейного адреса.

Рассмотрим теперь все этапы преобразования логического адреса в физический более подробно.

Логический адрес — это термин, используемый в документации фирмы Intel для обозначения адреса ячейки памяти с точки зрения программиста. Логический адрес в 16- и 32-разрядном режимах состоит из двух компонентов: селектора сегмента и смещения. Однако в 64-разрядном режиме логический адрес состоит только из смещения, поскольку сегментная организация памяти в этом случае не используется.

Селектор сегмента

Селектор сегмента всегда является 16-разрядной величиной и хранится в сегментном регистре. Какой именно из сегментных регистров процессора содержит селектор для данного доступа к памяти, зависит от характера доступа. Так, если производится выборка кода команды, селектор будет находиться в регистре CS, если осуществляется неявный доступ к стеку — в регистре SS; эти два сегментных регистра не могут быть переопределены. Доступ к данным обычно осуществляется с использованием селектора в регистре DS, хотя с помощью префикса замены сегмента можно указать любой другой сегментный регистр. В строковых операциях MOVS, CMPS и STOS, а также команде потокового ввода INS один (или единственный) операнд использует значение селектора из регистра ES, который не может быть переопределён. При явных доступах к стеку (когда в качестве базового регистра используется ESP/ESP или BP/EBP/EBP) обычно используется сегментный регистр SS, однако, в отличие от неявных доступов, он может быть заменён на другой с помощью префикса замены сегмента.

В 64-разрядном режиме могут использоваться только сегментные регистры FS и GS, однако в этом случае они выступают в роли дополнительных базовых регистров, поскольку сегментация в этом режиме отключена.

Смещение

Смещение является вторым компонентом логического адреса. Его размер зависит от текущего режима работы процессора и может составлять 16, 32 или 64 бита.

В тех случаях, когда обращение к памяти производится явным образом (то есть если производится чтение или запись операнда в памяти, адрес которого явно задан в инструкции), смещение численно равно эффективному адресу, поэтому эти два понятия нередко смешивают и называют эффективный адрес смещением.

В случае неявного обращения к памяти (например, при выборке кода очередной команды или при чтении или записи размещённого в стеке операнда команд PUSH и POP) смещение определяется процессором автоматически в соответствии со смыслом выполняемой операции. Например, при выборке кода команды смещением является содержимое регистра IP/EIP/RIP, а при доступе к вершине стека — содержимое регистра SP/ESP/RSP.

Логические и виртуальные адреса

Общепринятым термином для обозначения адресов, с которыми прямо работает программа, является «виртуальный адрес». Однако особенности операционных систем, предназначенных для архитектуры IA-32, накладывают на его понимание свой отпечаток. Поскольку все популярные системы, включая Windows и Linux, используют механизм сегментации в минимально необходимой степени, программы работают в плоском адресном пространстве при неизменных значениях селекторов сегментов, загруженных в сегментные регистры операционной системой при запуске программы. Таким образом, программы (и программисты) фактически имеют дело лишь со смещениями. Документация на операционные системы, говоря, например, о передаче параметров системным сервисам, применяет термин «виртуальный адрес» в тех случаях, когда фактически происходит передача смещения. Таким образом, можно считать, что в популярных ОС виртуальные адреса равны смещениям из состава логических адресов. Численно они будут равны линейным адресам, однако считать виртуальные и линейные адреса эквивалентными некорректно, поскольку программа имеет прямой доступ к виртуальным адресам, в то время как линейные существуют лишь внутри процессора и для программы совершенно недоступны.

Операционные системы компьютеров, построенных на архитектуре PC, такие как Mac OS X, Windows 7 и Linux, позволяют одновременно запускать несколько программ. Разработчикам ОС удалось достичь этого, создавая видимость для каждой программы, что она единственная. Этот фокус получается сделать, используя такое понятие, как адрес памяти. Так как обычный компьютер имеет ограниченное количество памяти с настоящей физической адресацией, операционная система использует виртуальную схему распределения памяти на основе логического адреса. Использование технологии виртуальной адресации позволяет на компьютере запускать одновременно несколько программ.

Компьютерная память и программы

Компьютер запускает программы с использованием памяти со случайным доступом или RAM. В большинстве программ для выполнения арифметических действий и обработки данных используются переменные. Например, программа по расчету и начислению зарплаты использует такие переменные, как тариф почасовой оплаты, количество отработанного времени и фамилия работника. Каждая переменная имеет свой собственный адрес в памяти, что позволяет программе быстро найти место, где хранятся данные. Пока одна программа умещается в доступной памяти, все работает очень быстро и просто. Но стоит запустить большую программу или сразу несколько приложений, как возникают проблемы с их работой, и требуется более сложная схема управления памятью с использованием логических адресов. Кстати, многие программы для оптимизации Windows здорово помогают в подобных ситуациях.

Виртуальная память

В современных компьютерах уже давно используется интересная технология, в которой применяется такое понятие, как виртуальная память. Виртуальная память позволяет снять все ограничения, определенные небольшим объемом оперативной памяти. Для формирования виртуальной памяти используются ресурсы модулей RAM и жесткого диска, что позволяет использовать любые программы. С тех пор, как дисковое пространство на жестком диске стало очень дешевым, компьютер получил возможность использования намного больших программ, чем это было возможно в схеме с одной только RAM памятью. При таком подходе компьютеры с разным объемом оперативной памяти могут с одинаковым успехом работать с крупными проектами, требующими большого количества памяти.

Виртуальная память использует комбинацию физических и логических адресов. Так как современные программы созданы для работы с логическими адресами, то они абсолютно не замечают, какая память используется – физическая RAM или виртуальная память на нескольких устройствах хранения данных. При обращении к памяти из программ, операционная система переводит логические адреса в физические, которые могут находиться как в оперативной памяти, так и на жестком диске.

Физический адрес

Адрес в памяти, служащий для указания действительного размещения данных на компьютерном оборудовании, получил название физический адрес. Когда компьютер записывает данные по определенному физическому адресу в памяти, вы можете в любой момент обратиться к ним, зная его. Помимо модулей оперативной памяти, физический адрес может быть использован при работе с таким компонентом компьютера, как BIOS или basic input-output system. Этот чип содержит небольшие программы, записанные в BIOS еще на предприятии – изготовителе материнских плат. Другим устройством с физической адресацией к данным является жесткий диск, клавиатура и прочие компоненты системы. Но только при работе с памятью RAM может быть использована логическая адресация, и то косвенно.

Логический адрес

Логические адреса описывают виртуальный объем памяти, который может быть неограниченно большим. Некоторые современные системы построены на 64-битной архитектуре (основным элементом которой является 64-битный процессор), что позволяет использовать до 18 триллионов символов. Это намного больше, чем может уместиться на рядовом жестком диске. Каждая запущенная программа представляет себе, что она монопольно загружена в память, начиная с нулевого адреса и может себе позволить использование неограниченного ресурса памяти. Когда программа обращается в память за новыми переменными, операционная система транслирует логический адрес в физический, считывает данные и передает их программе. Операционная система может перемещать программы по физическим адресам памяти, в том числе на жесткий диск, в зависимости от обстоятельств. Сложный алгоритм ОС обязан отслеживать логический и физический адрес, используемый программами, для того, чтобы избежать конфликта между ними.

Логический адрес — это адрес, с которым обычно оперирует программное обеспечение, формируется он из двух величин. Первая — это 16-битный селектор (указатель) сегмента (берется из соответствующего операции сегментного регистра), вторая — 32(16)-битное смещение относительно начала сегмента. Логический адрес существует лишь внутри процессора и имеет смысл для программного обеспечения. Его преобразование в физический адрес для обращения к памяти осуществляется с помощью достаточно сложного механизма, функционирование которого существенно зависит от текущего режима работы процессора.

Программы могут использовать различные методы адресации (методы формирования логического адреса). В общем случае эти методы можно разделить на прямые и косвенные. Отличаются они способом задания 32(16)-битного смещения. Смещение может задаваться в коде программы непосредственным 32(16)-битным значением (прямая адресация), либо путем указания на регистр (регистры), значение в котором является смещением (косвенная адресация). Все возможные способы формирования 32-битного смещения представляются формулой на рис. 2.1. (в режиме 16-битной адресации 32-битные регистры заменяются на соответствующие 16-битные: EAX – AX, EBX – BX и т.д.).

Рис. 2.1. Возможные методы формирования смещения

Для формирования полного логического адреса смещение комбинируется с селектором сегмента. Селектор сегмента берется из одного из сегментных регистров (CS, DS, ES, SS, FS, GS). Используемый сегментный регистр задается либо неявно, либо с помощью префикса замещения сегмента, который предшествует коду команды. Используемые по умолчанию сегментные регистры, зависят от адресуемого объекта (операнд, команда и т.п.) и приведены в следующей таблице.

Таблица 2.1. Сегментные регистры, используемые по умолчанию

при формировании логического адреса

Тип адресуемого объекта

Сегментный регистр

Операции

Любые операции выборки (чтения) команд

Данные из стека

Все операции занесения и чтения данных из стека, а также любые обращения к данным, использующие в качестве регистра базы (Base) регистры EBP или ESP.

Читайте также: