Какие устройства используют каналы прямого доступа к памяти

Обновлено: 04.07.2024

Необходимость организации канала прямого доступа к памяти

Информация, хранимая во внешних устройствах памяти большой емкости, таких, как накопители на магнитных дисках и лентах, организована в виде блоков размером единицы и более килобайт. Для обмена данными между указанными устройствами памяти и основной (оперативной) памятью микропроцессора не подходят ни программный способ обмена, ни прерывания. Это обусловлено тем, что обмен производится блоками фиксированного размера в строгой последовательности, соответствующей расположению информации на магнитном носителе. Время на обмен одного байта данных строго фиксировано, ограничено скоростью передвижения носителя относительно магнитных головок и составляет весьма малое значение (единицы микросекунд и меньше). При программно–управляемом обмене и обмене с использованием прерываний на передачу байта данных затрачивается большее время. Для обмена данными в указанных условиях организуется прямой доступ к памяти (ПДП), или Direct Memory Access ( DMA ).

Каналом прямого доступа к памяти называют средства, позволяющие осуществить быстрый обмен данными непосредственно между основной памятью и внешним устройством (ВУ) без участия процессора. При этом способе обмена процедура ввода/вывода полностью осуществляется аппаратными средствами и возлагается на контроллер ПДП.

Отметим, что обычный обмен между внешним устройством и памятью реализуются за два командных цикла: вначале данные поступают от источника в центральный процессор, а затем — из процессора в приемник. При ПДП данные не проходят через процессор, и передача слова производится за один цикл. Поэтому основное достоинство обмена по каналу ПДП — высокая скорость обмена, ограниченная только временем доступа к памяти.

Принципы организации ПДП. Структурная схема организации канала ПДП показана на рис. 3.10.1. Прямой доступ к памяти предоставляется по завершении текущего машинного цикла процессора. В отличие от прерывания обмен по каналу ПДП выполняется без участия программы, поэтому содержимое рабочих регистров процессора сохраняется и на вхождение в режим ПДП не требуется затрат времени (отсутствует необходимость хранения в стеке содержимого рабочих регистров процессора).

Центральный процессор выполняет программирование контроллера, настраивая его на требуемый режим работы, и следит за состоянием контроллера. Во время обмена данными по каналу ПДП процессор отключен, а контроллер вырабатывает сигналы управления обменом для памяти и внешнего устройства. Связь внешнего устройства памятью осуществляется по шинам адреса и данных системного интерфейса. Проблема совместного использования шин центрального процессора и внешнего устройства решается двумя способами: организацией режима обмена с «захватом цикла» и (пакетного, или непрерывного) режима с блокировкой центрального процессора.

В режиме с «захватом цикла» обмен ведется одиночными передачами, когда для прямого доступа к памяти выделяются отдельные циклы (такты), т. е. передача данных (слов) перемежается с выполнением программы.

Один из вариантов обмена с «захватом цикла» состоит в использовании тех тактов, в которых центральный процессор не обменивается данными с памятью. Такие такты должны быть известны контроллеру ПДП. Некоторые процессоры вырабатывают специальный сигнал, указывающий используется ли процессором в данном цикле память. Например, Такой сигнал VMA вырабатывает микропроцессор

Motorola 6800

Процессор Intel 8080 никогда не использует четвертый и пятый такты машинных циклов для доступа к внешней памяти. Кроме того, каждый командный цикл начинается с машинного цикла М1 — выборки команды. В такте декодирования принятой процессором команды этого машинного цикла системные шины не используются. На это время системные шины можно отдать для передачи одного слова по каналу ПДП. Применение рассмотренного способа организации обмена не снижает производительности процессоров, однако:

● требует дополнительных аппаратных затрат и позволяет реализовать только случайные, нерегулярные передачи;

● скорость обмена будет не быстрой, темп обмена нерегулярен, так как длительности циклов различных команд различны, и, кроме того, прямой доступ может все–таки замедлить выполнение программы, если цикл ПДП не превышает интервал, соответствующий такту процессора.

Более распространенным является вариант способа с «захватом цикла», при котором центральный процессор принудительно отключается от системных шин адреса и данных. Его реализация связана с введением двух линий для передачи сигналов запроса на захват шин (ЗЗхв) и подтверждения захвата (ПЗхв). Сигнал ЗЗхв формируется контроллером ПДП.

После получения сигнала ЗЗхв процессор:

● приостанавливает выполнение очередной команды, не дожидаясь ее завершения;

● выдает в системный интерфейс сигнал подтверждения захвата ПЗхв;

● отключается от шин адреса и данных, переводя в высокоомное состояние шинные формирователи.

После получения сигнала ПЗхв контроллер ПДП использует шины системного интерфейса для обмена байтом или словом между ВУ и памятью. Затем снимает сигнал запроса ЗЗхв и возвращает управление шинами центральному процессору. Подготовив очередной байт или слово данных, контроллер ПДП вновь посылает сигнал ЗЗхв процессору и т. д.

Как уже отмечалось, режим ПДП не требует сохранения состояния регистров процессора в стеке. Поэтому передача данных с «захватом цикла» происходит с большей скоростью, чем при обмене в режиме прерываний.

Способ ПДП с блокировкой процессора отличается от способа с «захватом цикла» тем, что управление шинами контроллеру передается на время обмена блоком данных, а не на время обмена байтом или словом. Его следует применять, когда время обмена байтом сопоставимо с циклом процессора. В этом случае между двумя операциями обмена процессор не успевает выполнить ни одной команды. При непрерывной передаче массива данных скорость обмена ограничивается длительностью циклов устройства памяти, быстродействием самого контроллера и скоростью выдачи/приема данных внешним устройством.

Обмен данными по каналу ПДП требует предварительной подготовки контроллера. Она заключается в том, что программа загрузки устанавливает необходимые параметры для передачи:

● количество байтов (слов) данных, которые должны быть переданы;

● начальный адрес передаваемых данных (адрес первого байта или слова);

● направление передачи (запись/чтение).

Для занесения этих параметров в контроллере предусмотрены регистр адреса и счетчик байтов (слов).

Реализация прямого доступа к памяти. В качестве примера рассмотрим особенности схемной реализации и работы канала ПДП при передаче из внешнего устройства в память блоков данных в режиме с «захватом цикла». Схема такого устройства ПДП приведена на рис. 3.10.2. В устройстве можно выделить три вида аппаратных средств.

Средства адресации и контроля переданных слов:

● суммирующий 16–разрядный счетчик текущего адреса, разделенный на две половины для младших (МР) и старших (СР) разрядов. Каждая половина имеет свой адрес, по которому происходит начальная загрузка счетчика. На выходе счетчиков включены управляемые буферы для передачи адреса в память;

● вычитающий 8–разрядный счетчик слов, контролирующий число оставшихся для передачи слов. На его выходе включен логический элемент ИЛИ–НЕ, формирующий для внешнего устройства Флаг = 1 по завершении передачи блока данных, когда на вход ИЛИ–НЕ (10) поступает код 000000002;

DС с тремя логическими элементами ИЛИ–НЕ (1, 2, 3), включенными на его выходе. Дешифратор с логическими элементами инициирует загрузку счетчиков адреса и слов.

Средство хранения данных, в качестве которого используется восьмиразрядный буферный регистр. К выходу регистра подключен управляемый буфер, обеспечивающий побайтное считывание данных из регистра и запись их в память.

Средства управления

К ним относятся:

● двухразрядный двоичный счетчик, управляющий записью данных в память и состоянием счетчиков адреса и слов;

● триггер запроса ТЗ, предназначенный для формирования сигнала запроса на ПДП (ЗПДП) для центрального процессора по стробу, поступающему от внешнего устройства, и хранения сигнала ЗПДП до конца передачи блока данных;

● логические элементы 4–9, обеспечивающие требуемый алгоритм управления. Назначение используемых сигналов приведено в табл. 3.10.1.

Принцип работы устройства ПДП. Программа, выполняемая центральным процессором, задает необходимые параметры для передачи данных:

● 16–разрядный адрес ячейки памяти для хранения первого слова путем последовательной загрузки в счетчик адреса младшего (МБ) и старшего (СБ) байтов;

● количество передаваемых слов путем загрузки числа л в счетчик слов. Из внешнего устройства ВУ поступают байт данных и строб, по которому байт данных заносится в буферный регистр. Строб также устанавливает триггер запроса ТЗ в единичное состояние. С выхода триггера ТЗ снимается сигнал запроса ПДП (ЗПДП). Получив сигнал ЗПДП, процессор приостанавливает выполнение программы, отключается от шин, предоставляя их устройству ПДП, и посылает сигнал разрешения ПДП (РПДП).

Сигнал РПДП выполняет следующие функции:

● открывает буфер для передачи содержимого буферного регистра на ШД;

● открывает буферы для передачи содержимого счетчика адреса на 16–разрядную шину адреса ША;

● запускает двухразрядный счетчик подачей сигнала на вход «Сброс» через инвертор (5);

● открывает элемент И (4) для поступления тактовых импульсов на вход «Счет» счетчика.

При втором тактовом импульсе ТИ на выходе счетчика появляются сигналы

Q0 = 0. При комбинации

Q0 =10 элемент 8 закрыт, элементы 7 и 9 — открыты. Сигнал «Запись в память» ЗпП, проходя через элемент И (9), инициирует запись в память байта данных из буферного регистра по адресу, выставленному на ША счетчиком адреса.

Третий ТИ переводит двухразрядный счетчик в состояние Q1

Q0 = 11, благодаря чему открывается элемент И (8). На его выходе формируется сигнал «Счет», который:

● увеличивает на 1 содержимое счетчика адреса;

● уменьшает на 1 содержимое счетчика слов;

● производит сброс триггера запроса ТЗ, снимая сигнал запроса ПДП.

В результате этих операций процессор возобновляет работу, а счетчики подготовлены к передаче следующего слова (байта данных). Процессор продолжает работать до тех пор, пока не будет загружен буферный регистр новым словом и не будет послан новый запрос на ПДП. Далее процесс передачи слов по каналу ПДП повторяется. После того, как содержимое счетчика слов станет равным нулю (000000002), включенный на его выходе элемент ИЛИ–НЕ (10) установит флаг в единичное состояние, свидетельствующее об окончании передачи блока данных.

Термин DMA наверняка не раз встречался читателям в различных компьютерных статьях. Что же он означает, влияет ли это понятие на работу компьютера, и если да, то как? В этом мы и попытаемся разобраться.

Принцип работы

Большинство устройств ПК нуждаются в периодическом обмене данными не только с центральным процессором (ЦП), но и с оперативной памятью. В первых вариантах персональных компьютеров процесс обмена данными какого-либо устройства с ОЗУ протекал при помощи процессора. Такой метод получил название PIO (Programmable Input-Output, программируемый ввод-вывод). Однако этот метод имел ряд недостатков. Прежде всего, было очевидно, что поскольку процессор загружен множеством задач, то он не всегда может отвлекаться на то, чтобы управлять процессом чтения и записи данных ОЗУ, тем более, что объем этих данных в результате прогресса компьютерной техники все увеличивался и увеличивался.

Так появилась идея технологии DMA (сокращение от Direct Memory Access, т.е. Прямой Доступ к Памяти), состоящая в том, чтобы позволить различным устройствам обращаться к оперативной памяти напрямую, минуя ЦП. Также часто используется русская аббревиатура данной технологии – ПДП.

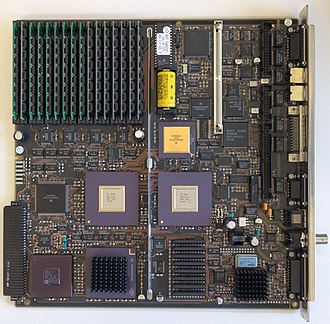

Первоначально практическая реализация этой технологии (в материнских платах на основе шины ISA) была осуществлена при помощи встроенного в материнскую плату контроллера ПДП, который был призван управлять процессом обмена данными между устройством и ОЗУ. При этом процессор также не был полностью исключен из этого процесса. Прежде всего, механизм ПДП инициализировался самим процессором, однако в ход процесса передачи данных он не вмешивался, занимаясь в это время другими задачами. После того, как обмен информацией между устройством и ОЗУ завершался, то процессор получал соответствующее прерывание, которое отсылал ему контроллера DMA.

В шине ISA также использовались специальные каналы ПДП, которые часто закреплялись за отдельным устройством:

Обычно данные каналы можно было устанавливать программным путем, но на некоторых старых устройствах, например, картах расширения для подключения накопителей CD-ROM, необходимо было вручную устанавливать значения нужных каналов при помощи перемычек.

Современная реализация

Начиная с появления шины ввода-вывода PCI, концепция практической реализации ПДП претерпела изменения. В материнских платах с шиной PCI больше не использовался контроллер DMA, а вместо этого стала применяться технология Bus Mastering. Суть этой технологии заключается в том, что любое устройство может обратиться к шине и полностью использовать ее в своих целях, в том числе, и для доступа к оперативной памяти. Кроме того, в шине PCI отпала необходимость в использовании каналов доступа к памяти. Подобный механизм используется также и в преемниках шины PCI –сверхбыстрых шинах AGP и PCI-Express.

Прямой доступ к памяти могут использовать любые устройства, расположенные в слотах расширения материнской платы, или подключенные к ней при помощи внутренних шин. Это могут быть, например, жесткие диски, накопители для оптических дисков, видеокарты, звуковые и сетевые карты, и т.д. Кроме того, технология DMA может использоваться как внутри процессоров – для передачи данных между отдельными ядрами, так и внутри самой оперативной памяти – для обмена данными между различными участками памяти.

Современные операционные системы, такие как MS Windows, умеют управлять режимом ПДП для многих устройств. В частности, пользователь имеет возможность включить или выключить режим DMA для жестких дисков.

В жестких дисках с интерфейсом IDE технология ПДП получила свое развитие в виде дополнительных режимов ПДП, получивших название Ultra DMA (UDMA). Всего стандарт Ultra DMA поддерживает 8 основных режимов передачи данных, обеспечивающих скорость от 16,7 до 167 МБ/c. Использование режимов Ultra DMA для винчестеров позволило значительно увеличить пропускную способность шины IDE. Включить или изменить режим Ultra DMA для жестких дисков можно при помощи специальной опции BIOS, обычно носящей название DMA (UDMA) Mode.

Заключение

Появление технологии ПДП позволило разгрузить процессор и избавить его от большого объема рутинной работы по пересылке данных между оперативной памятью и устройствами, расположенными на материнской плате или подключенными к ней. Особенно важно использование разновидности технологии ПДП – Ultra DMA в винчестерах на основе интерфейса IDE, что позволяет значительно ускорить обмен данными между накопителем IDE и материнской платой.

Прямой доступ к памяти ( DMA ) - это функция компьютерных систем, которая позволяет некоторым аппаратным подсистемам получать доступ к основной системной памяти ( оперативной памяти ) независимо от центрального процессора (ЦП).

Без DMA, когда ЦП использует запрограммированный ввод / вывод , он обычно полностью занят на протяжении всей операции чтения или записи и, таким образом, недоступен для выполнения другой работы. При использовании DMA ЦП сначала инициирует передачу, затем выполняет другие операции, пока выполняется передача, и, наконец, получает прерывание от контроллера DMA (DMAC), когда операция завершена. Эта функция полезна в любое время, когда ЦП не может поддерживать скорость передачи данных или когда ЦП должен выполнять работу в ожидании относительно медленной передачи данных ввода-вывода. Многие аппаратные системы используют DMA, включая контроллеры дисководов , графические карты , сетевые карты и звуковые карты . DMA также используется для передачи данных внутри кристалла в многоядерных процессорах . Компьютеры, у которых есть каналы DMA, могут передавать данные на устройства и с них с гораздо меньшей нагрузкой на ЦП, чем компьютеры без каналов DMA. Точно так же элемент обработки внутри многоядерного процессора может передавать данные в свою локальную память и из нее, не занимая свое процессорное время, что позволяет выполнять вычисления и передачу данных параллельно.

DMA также может использоваться для копирования или перемещения данных в памяти «из памяти в память». DMA может выгружать дорогостоящие операции с памятью, такие как большие копии или операции сбора данных , с ЦП на выделенный механизм DMA. Примером реализации является технология ускорения ввода-вывода . DMA представляет интерес для вычислительных архитектур " сеть на кристалле" и " в памяти" .

СОДЕРЖАНИЕ

Принципы

Третья сторона

Стандартный DMA, также называемый сторонним DMA, использует контроллер DMA. Контроллер DMA может генерировать адреса памяти и инициировать циклы чтения или записи памяти. Он содержит несколько аппаратных регистров, которые могут быть записаны и прочитаны ЦП. К ним относятся регистр адреса памяти, регистр подсчета байтов и один или несколько регистров управления. В зависимости от того, какие функции предоставляет контроллер DMA, эти регистры управления могут определять некоторую комбинацию источника, пункта назначения, направления передачи (чтение с устройства ввода-вывода или запись на устройство ввода-вывода), размер единица передачи и / или количество байтов, передаваемых за один пакет.

Для выполнения операций ввода, вывода или преобразования памяти в память главный процессор инициализирует контроллер прямого доступа к памяти, подсчитывая количество слов для передачи и адрес памяти для использования. Затем ЦП дает команду периферийному устройству инициировать передачу данных. Затем контроллер DMA предоставляет адреса и линии управления чтением / записью в системную память. Каждый раз, когда байт данных готов для передачи между периферийным устройством и памятью, контроллер DMA увеличивает свой внутренний адресный регистр до тех пор, пока не будет передан полный блок данных.

Освоение автобуса

В системе управления шиной , также известной как первичная система прямого доступа к памяти (DMA), ЦП и периферийные устройства могут получать управление шиной памяти. Если периферийное устройство может стать мастером шины, оно может напрямую записывать в системную память без участия ЦП, предоставляя адрес памяти и управляющие сигналы по мере необходимости. Должны быть предусмотрены некоторые меры для перевода процессора в состояние удержания, чтобы не возникало конкуренции на шине.

Режимы работы

В режиме серийной съемки

В пакетном режиме весь блок данных передается в одной непрерывной последовательности. Как только контроллер DMA получает доступ к системной шине от ЦП, он передает все байты данных в блоке данных, прежде чем отдать управление системными шинами обратно ЦП, но делает ЦП неактивным на относительно длительные периоды времени. Этот режим также называют «режимом блочной передачи».

Циклический режим кражи

Кража цикла режим используется в системах , в которых процессор не должен быть отключен для продолжительности времени , необходимого для пакетных режимов передачи. В режиме перехвата цикла контроллер DMA получает доступ к системной шине таким же образом, как и в пакетном режиме, используя сигналы BR ( запрос шины ) и BG (предоставление шины ) , которые являются двумя сигналами, управляющими интерфейсом между ЦП и Контроллер DMA. Однако в режиме перехвата цикла после передачи одного байта данных управление системной шиной передается ЦП через BG. Затем он постоянно запрашивается снова через BR, передавая один байт данных за запрос, пока не будет передан весь блок данных. Постоянно получая и освобождая управление системной шиной, контроллер прямого доступа к памяти чередует передачи инструкций и данных. ЦП обрабатывает инструкцию, затем контроллер DMA передает одно значение данных и так далее. Данные передаются не так быстро, но ЦП не простаивает так долго, как в пакетном режиме. Режим Cycle Stealing полезен для контроллеров, которые отслеживают данные в реальном времени.

Прозрачный режим

Прозрачный режим требует больше всего времени для передачи блока данных, но он также является наиболее эффективным с точки зрения общей производительности системы. В прозрачном режиме контроллер DMA передает данные только тогда, когда ЦП выполняет операции, не использующие системные шины. Основным преимуществом прозрачного режима является то, что ЦП никогда не прекращает выполнение своих программ, а передача DMA бесплатна с точки зрения времени, а недостатком является то, что аппаратное обеспечение должно определять, когда ЦП не использует системные шины, что может быть сложным. . Это также называется « скрытым режимом передачи данных DMA ».

Согласованность кеша

DMA может привести к проблемам с когерентностью кеша . Представьте себе ЦП, оснащенный кэш-памятью и внешней памятью, к которой могут напрямую обращаться устройства, использующие DMA. Когда ЦП обращается к ячейке X в памяти, текущее значение сохраняется в кэше. Последующие операции с X будут обновлять кэшированную копию X, но не версию X во внешней памяти, предполагая кеш с обратной записью . Если кэш не будет сброшен в память до следующей попытки устройства получить доступ к X, устройство получит устаревшее значение X.

Точно так же, если кэшированная копия X не становится недействительной, когда устройство записывает новое значение в память, то ЦП будет работать с устаревшим значением X.

Эта проблема может быть решена одним из двух способов при проектировании системы: системы с когерентной кэш-памятью реализуют аппаратный метод, называемый отслеживанием шины , при котором внешние записи передаются контроллеру кеша, который затем выполняет аннулирование кеша для записей DMA или очистку кеша для DMA читает. Некогерентные системы оставляют это на усмотрение программного обеспечения, где ОС должна затем гарантировать, что строки кэша очищаются до начала исходящей передачи DMA и становятся недействительными до того, как будет получен доступ к диапазону памяти, затронутому входящей передачей DMA. ОС должна убедиться, что в это время к диапазону памяти не обращаются никакие запущенные потоки. Последний подход вводит некоторые накладные расходы на операцию DMA, поскольку для большинства аппаратных средств требуется цикл для аннулирования каждой строки кэша по отдельности.

Также существуют гибриды, в которых вторичный кэш L2 согласован, а кэш L1 (обычно на ЦП) управляется программным обеспечением.

Примеры

Каждый канал DMA имеет 16-битный адресный регистр и связанный с ним 16-битный счетный регистр. Чтобы инициировать передачу данных, драйвер устройства устанавливает адрес канала DMA и регистры счета вместе с направлением передачи данных, чтения или записи. Затем он инструктирует оборудование DMA начать передачу. Когда передача завершена, устройство прерывает работу ЦП.

Дискретно-сборный или векторный ввод-вывод DMA позволяет передавать данные в и из нескольких областей памяти за одну транзакцию DMA. Это эквивалентно объединению в цепочку нескольких простых запросов DMA. Мотивация состоит в том, чтобы разгрузить несколько задач прерывания ввода / вывода и копирования данных из ЦП.

DRQ означает запрос данных ; DACK для подтверждения данных . Эти символы, которые можно увидеть на схемах оборудования компьютерных систем с функциями DMA, представляют собой линии электронной сигнализации между ЦП и контроллером DMA. Каждый канал DMA имеет одну строку запроса и одну строку подтверждения. Устройство, использующее DMA, должно быть настроено для использования обеих линий назначенного канала DMA.

16-битное управление шиной разрешено ISA.

Стандартные назначения ISA DMA:

PCI архитектура не имеет центрального контроллера DMA, в отличие от ISA. Вместо этого любое устройство PCI может запросить управление шиной («стать мастером шины ») и запросить чтение и запись в системную память. Точнее, компонент PCI запрашивает владение шиной у контроллера шины PCI (обычно мост хоста PCI и мост PCI-PCI), который будет выполнять арбитраж, если несколько устройств запрашивают владение шиной одновременно, поскольку одновременно может быть только один мастер шины. Когда компоненту предоставляется право собственности, он будет выдавать обычные команды чтения и записи на шине PCI, которые будут востребованы контроллером шины PCI.

Например, на ПК на базе AMD Socket AM2 южный мост будет перенаправлять транзакции на контроллер памяти (который встроен в кристалл ЦП) с помощью HyperTransport , который, в свою очередь, преобразует их в операции DDR2 и отправит их на Шина памяти DDR2. В результате, передача PCI DMA состоит из множества этапов; однако это не создает особых проблем, поскольку устройство PCI или сама шина PCI на порядок медленнее, чем остальные компоненты (см. список полос пропускания устройства ).

Современный процессор x86 может использовать более 4 ГБ памяти, используя расширение физического адреса (PAE), 36-разрядный режим адресации или собственный 64-разрядный режим процессоров x86-64 . В таком случае устройство, использующее DMA с 32-битной адресной шиной, не может адресовать память выше линии 4 ГБ. Новый механизм двойного цикла адресации (DAC), если он реализован как на шине PCI, так и на самом устройстве, обеспечивает 64-битную адресацию DMA. В противном случае операционной системе необходимо было бы обойти проблему, используя либо дорогостоящие двойные буферы (номенклатура DOS / Windows), также известные как буферы отказов ( FreeBSD / Linux), либо она могла бы использовать IOMMU для предоставления услуг трансляции адресов, если они есть. .

I / OAT

В качестве примера механизма DMA, встроенного в ЦП общего назначения, некоторые наборы микросхем Intel Xeon включают в себя механизм DMA, называемый технологией ускорения ввода-вывода (I / OAT), который может разгружать копирование памяти с основного ЦП, освобождая его для выполнения другой работы. . В 2006 году разработчик ядра Linux для Intel Эндрю Гровер провел тесты с использованием ввода-вывода для разгрузки копий сетевого трафика и обнаружил не более 10% улучшения использования ЦП при приеме рабочих нагрузок.

Дальнейшие ориентированные на производительность усовершенствования механизма DMA были внесены в процессоры Intel Xeon E5 с их функцией прямого ввода-вывода данных ( DDIO ), позволяющей «окнам» DMA располагаться в кэшах ЦП, а не в системной ОЗУ. В результате кэши ЦП используются в качестве основного источника и места назначения для ввода-вывода, позволяя контроллерам сетевого интерфейса (NIC) выполнять прямой доступ к памяти напрямую в кэш последнего уровня (кэш L3) локальных ЦП и избегать дорогостоящего извлечения данных ввода-вывода. данные из системной оперативной памяти. В результате DDIO снижает общую задержку обработки ввода-вывода, позволяет полностью выполнять обработку ввода-вывода в кэше, предотвращает превращение доступной полосы пропускания / задержки ОЗУ в узкое место производительности и может снизить энергопотребление, разрешив ОЗУ дольше оставаться в маломощном состоянии.

В системах на кристалле и встраиваемых системах типичная инфраструктура системной шины представляет собой сложную на кристалле шину, такую как высокопроизводительная шина AMBA . AMBA определяет два типа компонентов AHB: главный и подчиненный. Подчиненный интерфейс похож на программный ввод-вывод, через который программное обеспечение (работающее на встроенном ЦП, например, ARM ) может записывать / читать регистры ввода-вывода или (реже) блоки локальной памяти внутри устройства. Устройство может использовать главный интерфейс для выполнения транзакций DMA в / из системной памяти без большой нагрузки на ЦП.

Следовательно, устройства с высокой пропускной способностью, такие как сетевые контроллеры, которым необходимо передавать огромные объемы данных в / из системной памяти, будут иметь два интерфейсных адаптера к AHB: главный и подчиненный интерфейс. Это связано с тем, что встроенные в микросхемы шины, такие как AHB, не поддерживают преобразование шины в три положения или изменение направления любой линии на шине. Как и PCI, центральный контроллер DMA не требуется, поскольку DMA управляет шиной, но в случае наличия в системе нескольких мастеров требуется арбитр .

Внутри устройства обычно присутствует многоканальный механизм прямого доступа к памяти (DMA), который выполняет несколько одновременных операций сбора и разброса, как это запрограммировано программным обеспечением.

Клетка

В качестве примера использования DMA в многопроцессорной системе на кристалле , процессор Cell от IBM / Sony / Toshiba включает механизм DMA для каждого из своих 9 процессорных элементов, включая один элемент процессора Power (PPE) и восемь элементов синергетического процессора (SPE). . Поскольку инструкции загрузки / сохранения SPE могут считывать / записывать только свою собственную локальную память, SPE полностью зависит от DMA для передачи данных в основную память и локальную память других SPE и из них. Таким образом, DMA действует как основное средство передачи данных между ядрами внутри этого ЦП (в отличие от согласованных с кешем архитектур CMP, таких как отмененный универсальный графический процессор Intel , Larrabee ).

DMA в ячейке полностью согласован с кешем (обратите внимание, однако, локальные хранилища SPE, управляемые DMA, не действуют как глобально согласованный кеш в стандартном смысле ). Как при чтении («получить»), так и при записи («положить») команда DMA может передавать либо одну область блока размером до 16 КБ, либо список от 2 до 2048 таких блоков. Команда DMA выдается путем указания пары локального адреса и удаленного адреса: например, когда программа SPE выдает команду put DMA, она указывает адрес своей собственной локальной памяти в качестве источника и адрес виртуальной памяти (указывающий на либо основная память, либо локальная память другого SPE) в качестве цели вместе с размером блока. Согласно эксперименту, эффективная пиковая производительность DMA в ячейке (3 ГГц при равномерном трафике) достигает 200 ГБ в секунду.

Конвейерная обработка

Процессоры с блокнотом памятью и DMA (например, цифровые сигнальными процессорами и сотовым процессором) могут извлечь выгоду из программного обеспечения , перекрывающего операцию памяти DMA с обработкой, с помощью двойной буферизации или мультибуферизации. Например, внутренняя память разделена на два буфера; процессор может работать с данными в одном, в то время как механизм DMA загружает и сохраняет данные в другом. Это позволяет системе избежать задержки памяти и использовать пакетные передачи за счет необходимости предсказуемой схемы доступа к памяти .

Использование механизма прерываний позволяет разумно загружать процессор в то время, когда устройство ввода-вывода занимается своей работой. Однако запись или чтение большого количества информации из адресного пространства ввода-вывода (например, с диска) приводят к большому количеству операций ввода-вывода, которые должен выполнять процессор. Для освобождения процессора от операций последовательного вывода данных из оперативной памяти или последовательного ввода в нее был предложен механизм прямого доступа внешних устройств к памяти – ПДП или Direct Memory Access – DMA. Давайте кратко рассмотрим, как работает этот механизм.

Для того чтобы какое-либо устройство, кроме процессора, могло записать информацию в память или прочитать ее из памяти, необходимо чтобы это устройство могло забрать у процессора управление локальной магистралью для выставления соответствующих сигналов на шины адреса, данных и управления. Для централизации эти обязанности обычно возлагаются не на каждое устройство в отдельности, а на специальный контроллер – контроллер прямого доступа к памяти . Контроллер прямого доступа к памяти имеет несколько спаренных линий – каналов DMA, которые могут подключаться к различным устройствам. Перед началом использования прямого доступа к памяти этот контроллер необходимо запрограммировать, записав в его порты информацию о том, какой канал или каналы предполагается задействовать, какие операции они будут совершать, какой адрес памяти является начальным для передачи информации и какое количество информации должно быть передано. Получив по одной из линий – каналов DMA, сигнал запроса на передачу данных от внешнего устройства, контроллер по шине управления сообщает процессору о желании взять на себя управление локальной магистралью . Процессор, возможно, через некоторое время, необходимое для завершения его действий с магистралью, передает управление ею контроллеру DMA, известив его специальным сигналом. Контроллер DMA выставляет на адресную шину адрес памяти для передачи очередной порции информации и по второй линии канала прямого доступа к памяти сообщает устройству о готовности магистрали к передаче данных. После этого, используя шину данных и шину управления , контроллер DMA, устройство ввода-вывода и память осуществляют процесс обмена информацией. Затем контроллер прямого доступа к памяти извещает процессор о своем отказе от управления магистралью, и тот берет руководящие функции на себя. При передаче большого количества данных весь процесс повторяется циклически.

При прямом доступе к памяти процессор и контроллер DMA по очереди управляют локальной магистралью . Это, конечно, несколько снижает производительность процессора, так как при выполнении некоторых команд или при чтении очередной порции команд во внутренний кэш он должен поджидать освобождения магистрали, но в целом производительность вычислительной системы существенно возрастает.

При подключении к системе нового устройства, которое умеет использовать прямой доступ к памяти , обычно необходимо программно или аппаратно задать номер канала DMA, к которому будет приписано устройство. В отличие от прерываний , где один номер прерывания мог соответствовать нескольким устройствам, каналы DMA всегда находятся в монопольном владении устройств.

Логические принципы организации ввода-вывода

Рассмотренные в предыдущем разделе физические механизмы взаимодействия устройств ввода-вывода с вычислительной системой позволяют понять, почему разнообразные внешние устройства легко могут быть добавлены в существующие компьютеры. Все, что необходимо сделать пользователю при подключении нового устройства, – это отобразить порты устройства в соответствующее адресное пространство, определить, какой номер будет соответствовать прерыванию , генерируемому устройством, и, если нужно, закрепить за устройством некоторый канал DMA. Для нормального функционирования hardware этого будет достаточно. Однако мы до сих пор ничего не сказали о том, как должна быть построена подсистема управления вводом-выводом в операционной системе для легкого и безболезненного добавления новых устройств и какие функции вообще обычно на нее возлагаются.

Структура системы ввода-вывода

Если поручить неподготовленному пользователю сконструировать систему ввода-вывода, способную работать со всем множеством внешних устройств, то, скорее всего, он окажется в ситуации, в которой находились биологи и зоологи до появления трудов Линнея [Linnaes, 1789]. Все устройства разные, отличаются по выполняемым функциям и своим характеристикам, и кажется, что принципиально невозможно создать систему, которая без больших постоянных переделок позволяла бы охватывать все многообразие видов. Вот перечень лишь нескольких направлений (далеко не полный), по которым различаются устройства.

- Скорость обмена информацией может варьироваться в диапазоне от нескольких байтов в секунду (клавиатура) до нескольких гигабайтов в секунду (сетевые карты).

- Одни устройства могут использоваться несколькими процессами параллельно (являются разделяемыми), в то время как другие требуют монопольного захвата процессом.

- Устройства могут запоминать выведенную информацию для ее последующего ввода или не обладать этой функцией. Устройства, запоминающие информацию, в свою очередь, могут дифференцироваться по формам доступа к сохраненной информации: обеспечивать к ней последовательный доступ в жестко заданном порядке или уметь находить и передавать только необходимую порцию данных.

- Часть устройств умеет передавать данные только по одному байту последовательно ( символьные устройства ), а часть устройств умеет передавать блок байтов как единое целое ( блочные устройства ).

- Существуют устройства, предназначенные только для ввода информации, устройства, предназначенные только для вывода информации, и устройства, которые могут выполнять и ввод, и вывод.

В области технического обеспечения удалось выделить несколько основных принципов взаимодействия внешних устройств с вычислительной системой, т. е. создать единый интерфейс для их подключения, возложив все специфические действия на контроллеры самих устройств. Тем самым конструкторы вычислительных систем переложили все хлопоты, связанные с подключением внешней аппаратуры, на разработчиков самой аппаратуры, заставляя их придерживаться определенного стандарта.

Похожий подход оказался продуктивным и в области программного подключения устройств ввода-вывода. Подобно тому как Линнею удалось заложить основы систематизации знаний о растительном и животном мире, разделив все живое в природе на относительно небольшое число классов и отрядов, мы можем разделить устройства на относительно небольшое число типов, отличающихся по набору операций, которые могут быть ими выполнены, считая все остальные различия несущественными. Мы можем затем специфицировать интерфейсы между ядром операционной системы, осуществляющим некоторую общую политику ввода-вывода, и программными частями, непосредственно управляющими устройствами, для каждого из таких типов. Более того, разработчики операционных систем получают возможность освободиться от написания и тестирования этих специфических программных частей, получивших название драйверов, передав эту деятельность производителям самих внешних устройств. Фактически мы приходим к использованию принципа уровневого или слоеного построения системы управления вводом-выводом для операционной системы (см. рис. 13.1).

В последующих разделах мы подробнее рассмотрим организацию и функции набора драйверов и базовой подсистемы ввода-вывода .

Читайте также: