Какой регистр микроконтроллера 80с51 используется для адресации внешней памяти данных

Обновлено: 06.07.2024

Предыдущая статья цикла " Микроконтроллеры для начитающих. Часть 4. Очень кратко о микропрограммах " была факультативной. Однако, теперь мы еще на шаг приблизимся к практическому использованию микроконтроллеров. Пусть и упрощенно, схематически, но мы теперь представляем, как устроен процессор микроконтроллера. Пришло время подключать его к остальным узлам управляющей микроЭВМ микроконтроллера.

При слове архитектура большинство людей вспоминает о дворцах и зданиях, строительстве, возникает ассоциация со словом зодчий. Это правильно, но термин архитектура применим не только к строительству. Фактически, архитектура обозначает основные принципы использованные при проектировании и создании чего-либо.

Применительно к ЭВМ, под архитектурой обычно называют совокупность основных принципов, идей, подходов, методов, которые использовались при ее проектировании. Чаще всего входит в понятие архитектура ЭВМ входят:

- Организация памяти. Это количество различных типов памяти, их организация, способы подключения к процессору, особенности работы памяти.

- Система команд. Обратите внимание, я не сказал набор команд, я сказал система команд. В наборе команд ЭВМ(точнее, процессора) некоторые команды могут отсутствовать, могут включаться дополнительные команды, но подход к формированию системы команд остается неизменным. Набор команд это подмножество системы команд. Сюда входит адресность команд (количество операндов), режимы адресации операндов, тонкости выполнения (количество циклов, возможно, переменное), типы выполняемых операций, возможность расширения.

- Подсистема ввода-вывода. Способы подключения и адресации внешних (периферийных). Сюда же относится и наличие (и организация) канала прямого доступа к памяти ЭВМ.

- Возможность построения многопроцессорных комплексов. Одновременная работа нескольких процессоров в составе ЭВМ далеко не так проста, как может показаться. Причем и с точки зрения программиста.

- Механические параметры. Да, как ни странным это кажется. Наверное все знают платы расширения устанавливаемые в настольные ПК или в гнезда PCMCIA. Были и определенные требования к размерам ТЭЗ (типовой элемент замены), так назывались платы устанавливаемые в стойки больших ЭВМ (ЕС, СМ). Механические параметры далеко не всегда входят в понятие архитектуры, но иногда такое встречается.

Подробно архитектуру рассматривать мы не будем, для наших целей в этом нет смысла. Но некоторые аспекты для нас очень важны. И начнем мы с архитектуры памяти, точнее, с того, как память подключается к процессору (или наоборот).

"Чистые архитектуры" идеального мира

Наиболее известны две архитектуры подключения памяти к процессору. Первая, знакомая всем по IBM PC совместимым ЭВМ (точнее, микропроцессорам 80x86), архитектура фон Неймана . Вторая, менее известная, но более важная для нас, как станет видно в дальнейшем, Гарвардская архитектура .

Наиболее известные архитектуры ЭВМ с точки зрения организации памяти. Наиболее известные архитектуры ЭВМ с точки зрения организации памяти.Как видно, основное различие здесь в использовании памяти.

Архитектура фон Неймана

Хранит и программу, и данные, в единой памяти. Это выглядит привлекательно, так как позволяет эффективно использовать память небольшого объема. У нас небольшая программа, которая обрабатывает большие объемы данных? Нет никаких проблем, главное, что бы суммарный размер программы и данных мог поместиться в память. Большая программа требующая мало данных? Тоже все просто.

Кроме того, мы можем заполнить область памяти данными и потом передать ей управление. Или использовать коды команд как данные, возможно, изменяя их.

Архитектура фон Неймана вполне естественна для универсальных ЭВМ, ведь в этом случае неизвестно, что именно потребуется программе и какое будет соотношение объема кода программы и данных. Мы можем легко загрузить новую программу и данные в память и начать выполнение.

Однако, и минусов хватает. Самый большой плюс, лежащий в основе архитектуры, является и самым большим минусом. Представьте, что по какой то причине программа записала часть данных в область команд. Это приведет к неработоспособности программы, если управление будет передано этой измененной области. Или к остановке ЭВМ (когда то давно это называлось АВОСТ - аварийный останов).

Второй, менее очевидный минус, невозможность одновременного считывания очередной команды и операнда, или считывания команды и записи результата. Доступ к памяти может быть только последовательным.

Гарвардская архитектура

Используется разная память для программ и данных. Здесь у нас нет опасности исказить команды программы ошибкой с записью данных. И мы можем считывать очередную команду и записывать результат или считывать операнд одновременно, так как у нас разные блоки памяти. Минусы исчезли? Не совсем.

Теперь мы не можем передать управление области данных или использовать команды как данные. То есть, мы не можем изменять саму программу. Но это иногда все таки требуется. Теперь мы должны по отдельности загружать в области памяти коды команд и данные перед началом выполнения программы. Для универсальных ЭВМ эта архитектура менее удобна, чем архитектура фон Неймана. Зато для микроконтроллеров она подходит хорошо. Ведь программа в микроконтроллер обычно загружается если не однократно, то надолго и изменять ее не требуется. А отдельная область данных позволяет повысить надежность работы и уменьшить объем ОЗУ (оперативная память зачастую дороже). Теперь стало немного понятнее, почему я сказал, что Гарвардская архитектура для более важна, мы же говорим как раз о микроконтроллерах.

При этом довольно неприятным минусом, пусть и не критичным, является снижение гибкости в использовании памяти. Представьте, что нам не хватает, совсем чуть чуть, памяти данных, но есть свободная память команд. Мы никак не можем решить проблему, так как память программ под хранение данных использовать нельзя. И наоборот.

Суровый реальный мир и компромиссы

Реальные ЭВМ не используют в чистом виде ни одну из описанных выше архитектур. Хотя существовали и ЭВМ полностью им соответствующие. Архитектура реальных ЭВМ это некий компромисс. Но прежде чем двигаться дальше нам нужно кратко остановиться на понятии адресного пространства.

Адресное пространство

Под адресным пространством мы будем понимать логически единую совокупность адресуемых ячеек памяти . Звучит туманно? Не волнуйтесь, сейчас все станет понятно. Давайте начнем разбираться с более знакомой всем универсальной ЭВМ (в виде ПК, например).

Из каких областей памяти обычно состоит программа? Во первых, собственно код (команды) программы. Во вторых, область данных. Причем можно выделить область инициализированных данных, которые получают определенные значения перед началом выполнения программы, и не инициализированных данных, значения которых не определены до момента явного присвоения. В третьих, область стека, где хранятся адреса возвратов из подпрограмм и временные данные. В четвертых, динамически выделяемая область памяти.

Совокупность этих областей памяти программы, или задачи, называется адресным пространством задачи. Выглядит это, примерно, так

Пример упрощенного представления об адресном пространстве программы. Иллюстрация моя Пример упрощенного представления об адресном пространстве программы. Иллюстрация мояДля процессоров 80х86 области памяти обычно называют сегментами. В рамках своего адресного пространства программа может как угодно распоряжаться памятью. Но выход за пределы адресного пространства запрещен (обычно, операционной системой). Видно, что адресное пространство задачи занимает часть, в общем случае, все имеющейся памяти ЭВМ.

Совокупность сегментов, показанных на иллюстрации выше, логически единая , так все эти области памяти относятся к одной и той же программе. Причем не требуется, в общем случае, такого смежного размещения областей памяти программы в физической памяти ЭВМ. Может быть, например, такое расположение

Пример отображения адресного пространства задачи на физическую память ЭВМ. Серым цветом отмечены не используемые области памяти. Иллюстрация моя Пример отображения адресного пространства задачи на физическую память ЭВМ. Серым цветом отмечены не используемые области памяти. Иллюстрация мояТакое отображение выполняется аппаратно специальными блоками управления памятью, которые могут входить как в состав процессора, так и в состав памяти. При этом адреса памяти используемые в программе называют логическими, а адреса физической памяти ЭВМ физическими. Я не буду углубляться в тему преобразования адресов и управления памятью, это очень обширная и интересная тема, но нам достаточно такого упрощенного представления.

Команды и данные не обязательно занимают все доступное адресное пространство программы. Если реальная потребность программы меньше, чем ей выделено памяти, то часть адресов остается неиспользованной. Доступное адресное пространство задачи может быть меньше, чем ее потребности в памяти. В этом случае приходится использовать методы организации виртуальной памяти, если это возможно. Виртуальную память я так же не буду рассматривать.

Адресные пространства могут полностью изолированными, могут частично перекрываться, могут полностью совпадать, одно из пространств может быть подмножеством другого. С точки зрения математики можно рассматривать адресные пространства как некий вид множеств (множества ячеек памяти) с почти всеми применимыми к множествам операциями.

В рамках приведенного ранее примера с адресным пространством задачи можно показать пример частичного перекрытия

Пример перекрывающихся адресных пространств. Иллюстрация моя Пример перекрывающихся адресных пространств. Иллюстрация мояНо какое это отношение имеет к микроконтроллерам? Самое прямое! И сейчас это станет видно.

Адресные пространства ЭВМ

Да, именно так. Микроконтроллер включает в себя управляющую ЭВМ, как мы уже видели ранее. Какие области памяти могут быть в ЭВМ? Вспомним наши "чистые архитектуры". Область команд программы и область данных . Но это не все, есть еще область стека , которая может оказаться не такой простой, и область ввода-вывода .

Почему ввод-вывод относится к памяти? Все просто. Мы должны как то адресовать устройства ввода-вывода, управлять ими, передавать им данные и получать ответы. Внешние устройства обычно представлены набором управляющих регистров, каждый из которых имеет определенный адрес. Вероятно, некоторым из вас знакомы команды IN и OUT , которые иногда используются для доступа к таким регистрам. Адреса в командах IN и OUT как раз и относятся к области ввода-вывода.

Еще я назову область специальных регистров процессора , о которой вспоминают не часто. Специальные регистры процессора могут иметь свои адреса, а могут и не иметь.

Таким образом, у нас есть пять областей памяти, каждая из которых может иметь собственные адреса, свой размер, и является логически единой(по смыслу). Другими словами, у нас есть пять адресных пространств.

В общем случае мы не можем сказать, что именно хранится в ячейке с некоторым адресом, если не указано, к какому адресному пространству она относится. Например, ячейка с адресом 10 может хранить команду, если она в адресном пространстве команд (программ), или являться, например, регистром управления внешнего устройства, если она в адресном пространстве ввода-вывода, или быть просто некоторой переменной, если она в адресном пространстве данных.

Если еще раз вспомнить "чистые архитектуры", то станет видно, что в архитектуре фон Неймана адресные пространства программ и данных полностью совпадают. А в Гарвардской архитектуре они полностью изолированы.

А вот со стеком все немного интереснее. Стек хранит адреса возвратов и временные данные. С архитектурой фон Неймана все понятно, там адресные пространства совпадают. А как быть с Гарвардской? Мы не можем поместить стек в память программ, так он может содержать и данные. А в микроконтроллерах память программ еще и обычно представлена ПЗУ. Мы не можем поместить стек в память данных, так это позволит изменять адреса возвратов, которые относятся к памяти программ.

Мы можем решить проблемы поместив стек в специальную, изолированную, область памяти. Или сделать два различных стека, один для адресов возвратов, второй для временных данных. Теперь понятно, почему я выделил стек как отдельную область памяти, отдельное адресное пространство?

Но вернемся к нашей теме. Даже в Гарвардской архитектуре иногда требуется доступ к памяти программ, как к данным. Это можно сделать несколькими способами, я кратко расскажу о двух.

Пример организации доступа к памяти программ как к внешнему устройству. Иллюстрация моя Пример организации доступа к памяти программ как к внешнему устройству. Иллюстрация мояПроще всего добавить в ЭВМ (или процессор) специальный блок, через который и будет осуществляться доступ к памяти программ, как к данным. С большой долей вероятности, этот блок позволит достаточно легко читать память программ, а вот запись будет или сложнее, или не будет доступна совсем. С точки зрения чистоты архитектуры это решение ничего не нарушает, адресные пространства по прежнему изолированы, а дополнительный блок является обычным внешним устройством. При этом доступ к памяти программ будет медленнее, чем к памяти данных. И потребует больших усилий при программировании.

А вот второй способ гораздо хитрее и, на первый взгляд, нарушает все различия между архитектурами. Мы можем построить виртуальное адресное пространство, которое и будет использовать процессор, и которое будет являться объединением адресных пространств данных и программ. Вот так

Пример объединения адресных пространств программ и данных в единое виртуальное адресное пространство. Иллюстрация моя Пример объединения адресных пространств программ и данных в единое виртуальное адресное пространство. Иллюстрация мояОбратите внимание, здесь нет принципиальных схемотехнических отличий от первого варианта, где мы работали с памятью программ как с внешним устройством. У нас лишь добавился дешифратор, который маскирует особенности памяти программ с точки зрения программиста. Доступ от этого не становится быстрее, но вот использовать его в программе проще. Самое виртуальное адресное пространство теперь выглядит примерно так

Пример единого виртуального адресного пространства программ и данных. Иллюстрация моя Пример единого виртуального адресного пространства программ и данных. Иллюстрация мояКто то может сказать, а чем это вообще отличается от архитектуры фон Неймана? А действительно, чем? Особенно с учетом того, что я сказал, что адресное пространство не обязательно должно отображаться на непрерывные области физической памяти.

Все просто, на самом деле. В архитектуре фон Неймана у нас адресные пространства программ и данных полностью совпадают. Фактически, там можно говорить о едином адресном пространстве программ/данных. В данном же случае, у нас адресные пространства программ и данных по прежнему изолированны, а виртуальное пространство строится как их объединение, но без нарушения изоляции.

Таким образом, для Гарвардской архитектуры мы можем строить виртуальные адресные пространства по разному комбинируя отдельные адресные пространства не нарушая их изолированности. А можно и включать одно пространство в другое, без изоляции. Например, мы можем включить адресное пространство регистров процессора в адресное пространство данных. Так сделано, например, в микроконтроллерах PIC Microchip и AVR Atmel. При этом туда же входит и адресное пространство ввода-вывода (для Atmel это не совсем так, но разница нам сейчас не принципиальна). Подробнее обо всем этом поговорим в следующих статьях.

Остается кратко упомянуть, как можно обеспечить изоляцию адресных пространств программ и данных для архитектуры фон Неймана. Тут тоже используются отдельные блоки управления памятью. Поскольку эта темя далеко от микроконтроллеров особенно углубляться в нее не буду. Скажу лишь, что обычно используется запрет передачи управления на области памяти, которые должны считаться памятью данных. При этом можно и читать, и записывать эти области, а вот передавать управление туда нельзя. И, разумеется, никто не отменял включения защиты от записи в определенные области памяти.

Архитектура и адресные пространства микроконтроллеров

Ну вот мы и добрались до микроконтроллеров. Путь был длинным и не простым, зато сейчас будет гораздо легче.

При этом доступ к памяти программ как к данным имеют далеко не все микроконтроллеры. В некоторых случаях такой доступ организован как к внешнему устройству, в некоторых моделях через виртуальное адресное пространство. При этом, через виртуальное адресное пространство не всегда можно производить запись в память программ, даже используя специальные методы доступа.

В большинстве микроконтроллеров адресное пространство регистров процессора объединено (включено) в адресное пространство данных. Так же, во многих контроллерах с отдельным адресным пространством ввода-вывода оно частично, или полностью, может включаться в пространство данных. Более подробно я это буду рассматривать когда доберемся до организации памяти (не архитектуры).

Некоторые микроконтроллеры позволяют организовывать виртуальное адресное пространство. Как это выглядит для микроконтроллеров PIC Microchip можно посмотреть в статье, ссылку на которую я давал выше. А вот для STM8 я приведу упрощенный вид виртуального адресного пространства

Примечание. Команда NOP используется для визуального разделения отдельных программ при проверке их работы.

Исследуйте работу программы в пошаговом режиме. Наблюдайте за изменением содержимого регистров, а также флагами МК.

3.2. Исследование команд пересылки с прямой адресацией

Запишите в память симулятора коды следующих команд:

MOV A, 30H ; Переслать в аккумулятор содержимое ячейки ПД с адресом 30H

MOV R1, 30H ; Переслать в регистр R1 содержимое ячейки с адресом 30H

MOV P0, A ; Переслать в порт P0 содержимое аккумулятора

MOV A, P0 ; Переслать в аккумулятор данные из порта P0

Исследуйте работу программы в пошаговом режиме. Наблюдайте за изменением содержимого регистров, ячеек памяти, порта P0, а также флагами МК.

3.3. Исследование команд пересылки с косвенной адресацией

Запишите в память симулятора коды следующих команд:

MOV A, @R0 ; Переслать в аккумулятор содержимое ячейки ПД

MOV @R0, A ; Переслать содержимое аккумулятора в ячейку ПД

Исследуйте работу программы в пошаговом режиме. Наблюдайте за изменением содержимого регистров, ячейки памяти, а также флагами МК.

3.4. Команды пересылки с использованием регистра DPTR

В микроконтроллерах семейства МК51 имеется 16-разрядный регистр-указатель данных DPTR, который используется при выполнении некоторых команд. Загрузить в него 16-разрядные данные можно командой:

Эта команда с непосредственной адресацией имеет трехбайтный формат: 1-й байт – код операции, 2-й и 3-й байты – 16-разрядные данные.

Запишите в память симулятора коды команд:

MOV R1, DPL ; Переслать в R1 содержимое DPL

MOV R2, DPH ; Переслать в R2 содержимое DPH

MOV DPH, A ; Переслать аккумулятор в регистр DPH

MOV DPL, A ; Переслать аккумулятор в регистр DPL

Выполните программу в пошаговом режиме работы. Наблюдайте за изменением содержимого регистров, а также флагами МК.

3.5. Исследование команд пересылки, использующих внешнюю память данных

Для работы с внешней памятью данных (ВПД) в МК51 имеются команды MOVX с использованием косвенной адресации. Возможны 2 варианта задания адреса ячеек ВПД:

1) если адреса ячеек находятся в диапазоне 00H…FFH (т.е. их количество не превышает 256), то для их адресации используются регистры R0 или R1 текущего банка, а для пересылки данных применяются команды:

MOVX @Ri, A ; Пересылка аккумулятора в ячейку ВПД (запись в ВПД)

MOVX A, @Ri ; Пересылка в аккумулятор из ячейки ВПД (чтение из ВПД);

2) если адреса ячеек находятся в диапазоне 0000H…FFFFH (адресное пространство 64К), то для адресации используется регистр DPTR, а для пересылки данных команды:

Отдельный класс МП представляют однокристальные микроконтроллеры, являющиеся основной базой для построения встроенных систем управления нижнего уровня. Различными фирмами были разработаны ряды семейств однокристальных микроконтроллеров. Сегодня многие из них можно считать стандартными компонентами для построения встроенных МПС. Базовым представителем семейства MCS-51 является микроконтроллер 80С51 фирмы INTEL. В СССР это микроконтроллеры выпускались на базе n-МОП технологии (серия 1816) и на базе КМОП технологии (серия 1830).

Микроконтроллеры семейства MCS-51 выпускаются многими другими фирмами.Особого внимания заслуживают:- АТ89СXX фирмы Atmel, имеющие большое число модификаций с широким набором периферии и различными комплектами встроенных ЗУ.

Основные характеристики микроконтроллера 80С51:

· восьмиразрядный ЦП, оптимизированный для реализации функций управления;

· встроенный тактовый генератор;

· адресное пространство памяти программ - 64 К;

· адресное пространство памяти данных - 64 К;

· внутренняя память программ - 4 К;

· внутренняя память данных - 128 байт;

· дополнительные возможности по выполнению побитовых операций булевой алгебры;

· 32 двунаправленные и индивидуально адресуемые линии ввода/вывода;

· 2 шестнадцатиразрядных таймера/счетчика;

· полнодуплексный асинхронный приемопередатчик;

· векторная система прерываний с двумя уровнями приоритета и шестью источниками событий

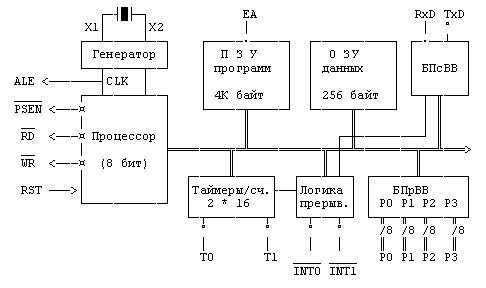

Структурная схема I-8051 показана на рис.7.1.

Рис. 7.1. Структурная схема I-8051

В MCS-51 используются следующие сигналы:

ALE - строб адреса;

PSEN\ - строб чтения внешней памяти программ;

RD\,WR\- стробы чтения и записи внешней памяти данных;

EA\ - разрешение обращения во внутреннюю память программ;

T0,T1 - входы счетчиков внешних событий;

INT0,INT1- запросы внешних радиальных прерываний;

RxD - вход данных последовательного канала;

TxD - выход данных последовательного канала.

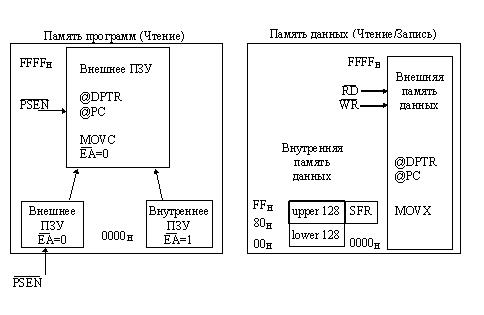

Организация памяти 80С51

MCS-51 имеет гарвардскую архитектуру, то есть раздельные адресные пространства памяти программ и данных. Организация памяти изображена на рис.7.2.

Рис.7.2. Организация памяти семейства MCS-51

Объем внутренней (резидентной) памяти программ (ROM, EPROM или OTP ROM), располагаемой на кристалле, в зависимости от типа микросхемы может составлять 0К (ROMless), 4К (базовый кристалл), 8К, 16К или 32К. При необходимости пользователь может расширять память программ установкой внешнего ПЗУ(ВПП). Доступ к ВПП возможен при выполнении двух условий: либо на вход отключения резидентной памяти программ (EA) подается активный сигнал, либо содержимое счетчика команд превышает значение 0FFFH.Доступ к внутреннему или внешнему ПЗУ определяется значением сигнала на выводе ЕА (External Access). Для кристаллов без ПЗУ (ROMless) вывод ЕА должен быть постоянно подключен к Vss(потенциал земли).

Строб чтения внешнего ПЗУ – PSEN (Program Store Enable) генерируется при обращении к внешней памяти программ и является неактивным во время обращения к ПЗУ, расположенному на кристалле.

Область нижних адресов памяти программ используется системой прерываний, архитектура микросхемы 8051обеспечивает поддержку пяти источников прерываний:

· двух внешних прерываний;

· двух прерываний от таймеров;

· прерывания от последовательного порта.

Рис.7.3. Адреса векторов прерываний семейства MCS-51

Адреса векторов прерываний расположены с интервалом в 8 байт:

· стартовый адрес при сбросе (вывод Reset);

· внешнее прерывание EINT0 –INT0;

· прерывание от таймера 0 –TF0;

· внешнее прерывание EINT1 –INT1;

· прерывание от таймера 1 –TF1;

· прерывание от последовательного порта Serial Port.

Память данных отделена от памяти программ. В этой области возможна адресация 64К внешнего ОЗУ. При обращении к внешней памяти данных ЦП микроконтроллера генерирует соответствующие сигналы чтения или записи ( ), взаимодействие с внутренней памятью данных осуществляется на командном уровне, при этом сигналы и не вырабатываются.

Нижние 128 байт внутренней памяти данных (lower 128) присутствуют на всех кристаллах MCS-51.Первые 32 байта представляют собой 4 банка (Register Bank) по 8 регистров (R7. R0). Регистры R0 и R1 в любом из банков могут использоваться в качестве регистров косвенного адреса.

Верхняя 128 байтная половина памяти ОЗУ (upper 128) в микросхеме I-8051 отсутствует, но имеется в версиях кристаллов с 256 байтами ОЗУ. В этом случае область "Upper 128" доступна только при косвенной адресации. Область SFR (Special Function Register) доступна только при прямой адресации.

Размещение регистров специальных функций в пространстве SFR показано на рис. 7.5. Они включают в себя регистры портов, таймеры, средства управления периферией и так далее. Для 16 адресов в пространстве SFR имеется возможность как байтовой, так и битовой адресации. Для побитно-адресуемых регистров шестнадцатеричный адрес заканчивается на "0Н" или на "8Н". Битовые адреса в этой области имеют значения от 80Н до FFH.

В кристаллах, представляющих собой дальнейшее развитие семейства MCS-51 в область SFR, добавляются новые регистры для расширения функциональных возможностей, например, матрица программируемых счетчиков (PCA), сторожевой таймер (WDT), аналого-цифровое преобразователь, синхронный последовательный интерфейс и так далее. Назначение регистров области SFR и отдельных битов этих регистров приведены ниже.

| 7FH 30H | Побайтно-адресуемая область ОЗУ (direct, indirect) | |||||||

| 2FH | 7FH | 7EH | 7DH | 7CH | 7BH | 7AH | 79H | 78H |

| 2EH | 77H | 76H | 75H | 74H | 73H | 72H | 71H | 70H |

| Побитно-адресуемая область ОЗУ (direct) | ||||||||

| 21H | 0FH | 0EH | 0DH | 0CH | 0BH | 0AH | 09H | 08H |

| 20H | 07H | 06H | 05H | 04H | 03H | 02H | 01H | 00H |

| 1FH 18H | RB3 | |||||||

| 17H 10H | RB2 | |||||||

| 0FH 08H | RB1 | |||||||

| 07H 00H | SP после RESET RB0(R7+R0) |

Рис.7.4. Организация нижней области ОЗУ семейства MCS-51

| F8H | FFH | ||||||

| F0H | B | F7H | |||||

| E8H | EFH | ||||||

| E0H | ACC | E7H | |||||

| D8H | DFH | ||||||

| D0H | PSW | D7H | |||||

| C8H | CFH | ||||||

| C0H | C7H | ||||||

| B8H | IP | BFH | |||||

| B0H | P3 | B7H | |||||

| A8H | IE | AFH | |||||

| A0H | P2 | A7H | |||||

| 98H | SCON | SBUF | 9FH | ||||

| 90H | P1 | 97H | |||||

| 88H | TCON | TMOD | TL0 | TL1 | TH0 | TH1 | 8FH |

| 80H | P0 | SP | DPL | DPH | PCON | 87H | |

| 0/8 | 1/9 | 2/A | 3/B | 4/C | 5/D | 6/E | 7/F |

Рис.7.5. Организация области регистров специальных функций (SFR)

Аккумулятор А (E0H).Команды MCS-51 используют аккумулятор как источник и как приемник при вычислениях и пересылках.

Регистр В (F0H).Регистр В используется как источник и как приемник при операциях умножения и деления.,

Регистр PSW (Слово состояния программы - D0H).Данный регистр содержит биты, отражающие результаты исполнения операций, биты выбора регистрового банка и бит общего назначения, доступный пользователю. PSW содержит:

| - | PSW.7 | - | бит переноса (Carry Flag, CY); |

| - | PSW.6 | - | бит вспомогательного переноса (Auxiliary Carry Flag, AC); |

| - | PSW.5 | - | пользовательский флаг (General Purpose Status Flag, F0); |

| - | PSW.4, PSW.3 | - | биты выбора регистрового банка (Register Bank Select Bits, RS1 и RS0); |

| - | PSW.2 | - | бит переполнения (Overflow Flag, OV); |

| - | PSW.1 | - | зарезервирован (Reserved); |

| - | PSW.0 | - | бит четности (Parity Flag, P). |

Регистры портов Р0+Р3 (адреса 80Н, 90Н, А0Н, В0Н).Каждый порт является фиксатором - защелкой и может адресоваться как побайтно, так и побитно. Помимо работы в качестве обычных портов ввода/вывода, линии портов могут выполнять ряд альтернативных функций:

· через порт 0 (в мультиплексном режиме) выводится младший байт адреса, а также выдается и принимается в микроконтроллер байт данных при работе с внешней памятью программ/данных. Задаются данные при программировании внутренней памяти программ и читается ее содержимое;

· через порт 2 выводится байт старший байт адреса внешней памяти программ и данных, а также задаются старшие разряды адреса при программировании и верификации УФРПЗУ;

· порт 1 предназначен для задания младшего байта адреса при программировании и проверке ПЗУ микросхемы. Линии порта используются также для обслуживания работы Т/С2 и модуля PCA (для тех версий кристаллов MCS-51, в составе которых имеются эти функциональные узлы);

· порт 3 имеет следующие альтернативные функции:

· Р3.7 - строб чтения из внешней памяти данных (Read Data for External Memory, );

· P3.6 - строб записи во внешнюю память данных (Write Data for External Memory, )

· P3.5 - внешний вход T/C1 (Timer/Counter 1 External Input, T1);

· P3.4 - внешний вход T/C0 (Timer/Counter 0 External Input, T0);

· P3.3 - вход внешнего прерывания 1 (External Interrupt 1 Input Pin, );

· P3.2 - вход внешнего прерывания 0 (External Interrupt 0 Input Pin, );

· P3.1 - выход данных передатчика последовательного порта (Serial Port Transmit Pin, TxD);

· P3.0 - вход данных передатчика последовательного порта (Serial Port Receive Pin, RxD).

Указатель стека SP (81Н).Используется для указания на вершину стека в операциях записи в стек и чтения из него. Неявно используется такими командами, как PUSH, RET, RETI, POP. По аппаратному сбросу от ЦП устанавливается в значение 07Н (область стека в этом случае начинается с адреса внутренней памяти данных 08Н) и инкрементируется при каждой записи в стек. Запись в SFR-регистр-SP (с использованием байтовой адресации) производится для предопределения положения стека во внутренней памяти данных.

Указатель данных DPTR (Data Pointer, адреса 82Н, 83Н).Команды MCS-51 используют DPTR для пересылки данных, пересылки кода и для переходов (JMP@A+DPTR). DPTR состоит из двух регистров: младшего - DPL и старшего - DPH, обращение к ним - только байтовое.

Регистр управления энергопотреблением PCON (Power Control Register, адрес 87Н).Для кристаллов, изготовленных по CHMOS-технологии, SFR-регистр PCON имеет следующее назначение битов:

PCON.7 - бит удвоения скорости передачи (Double Baud Rate Bit, SMOD);

PCON.6+PCON.4 - зарезервированы (Reserved);

PCON.3, PCON.2 - флаги общего назначения (General Purpose Flags, GF1, GF0);

PCON.1 - бит режима микропотребления (Power Down Bit, PD);

PCON.0 - бит холостого режима (Idle Mode Bit, IDL).

При установке холостого режима производится отключение ЦП при сохранении работоспособности внутрикристальных периферийных устройств и ОЗУ.

В режиме микропотребления приостанавливаются все операции при сохранении данных в ОЗУ (потребление тока микроконтроллером в этом случае менее 10 мкА). Выход из режима микропотребления осуществляется аппаратным сбросом длительностью не менее 10 мс (время восстановления работы задающего генератора), выход из холостого режима может быть произведен активизацией любого разрешенного прерывания, либо по сигналу RESET длительностью не менее двух машинных циклов.

Регистры таймеров/счетчиков TL0, TL1, TH0, TH1 (адреса 8АН, 8ВН, 8СН, 8DH).Образуют 16-битные (Low/High) регистры таймеров/счетчиков "Т/C0" и "Т/C1". Обращение к регистрам только байтовое.

Регистры управления режимами таймеров/счетчиков TMOD, TCON (89Н и 88Н).Предназначены для управления работой таймерной секции микроконтроллера.

Буфер последовательного порта SBUF (99Н).Представляет собой два отдельных регистра. При записи в SBUF загружается "буфер передачи" последовательного порта, при чтении SBUF считывается содержимое "буфера приема" последовательного порта.

Регистр управления последовательным портом SCON (98Н)Предназначен для управления работой последовательного порта. Обращение к данному регистру может быть как байтовым, так и побитным.

Регистр разрешения прерываний IE и регистр управления приоритетом прерывания IP (А8Н и В8Н).Поддерживают работу системы прерываний микроконтроллера.

Как и у большинства микроконтроллеров, у микроконтроллеров семейства 8051, память программ и память данных являются самостоятельными и независимыми друг от друга устройствами, адресуемыми различными командами и управляющими сигналами.

Объем встроенной памяти программ, расположенной на кристалле микроконтроллера 8051 и 8751, равен 4 Кбайт. При обращении к внешней памяти программ все микроконтроллеры семейства 8051 всегда используют 16-разрадный адрес, что обеспечивает им доступ к 64 Кбайт ПЗУ. Микроконтроллер обращается к программной памяти при чтении кода операции и операндов (используя счетчик команд PC), а также при выполнении команд переноса байта из памяти программ в аккумулятор. При выполнении команд переноса данных адресация ячейки памяти программ, из которой будут прочитаны данные, может осуществляться с использованием как счетчика PC, так и специального двухбайтового регистра-указателя данных DPTR.

Память данных (ОЗУ).

Объем расположенной на кристалле памяти данных—128 байт. Объем внешней памяти данных может достигать 64 Кбайт. Первые 32 байта организованы в четыре банка регистров общего назначения, обозначаемых соответственно банк 0 — банк 3. Каждый из них состоит из восьми регистров R0 — R7. В любой момент программе доступен только один банк регистров, номер которого содержится в третьем и четвертом битах слова состояния программы PSW (см. ниже).

Оставшееся адресное пространство может конфигурироваться разработчиком по своему усмотрению: в нем располагаются стек, системные и пользовательские области данных. Обращение к ячейкам памяти данных возможно двумя способами. Первый способ — прямая адресация ячейки памяти. В этом случае адрес ячейки является операндом соответствующей команды. Второй способ — косвенная адресация с помощью регистров R0 или R1: перед выполнением соответствующей команды в один из них должен быть занесен адрес ячейки, к которой необходимо обратиться.

Для обращения к внешней памяти данных используется только косвенная адресация с помощью регистров R0 и R1 или с помощью 16-разрядного регистра-указателя DPTR. Он относится к группе регистров специальных функций, и с его помощью можно адресовать все 64 Кбайта внешней памяти.

Часть памяти данных представляет собой так называемую битовую область, в ней имеется возможность при помощи специальных битовых команд адресовываться к каждому разряду ячеек памяти. Адрес прямо адресуемых битов может быть записан либо в виде (Адрес Байта ).(Разряд), например выражение 21.3 означает третий разряд ячейки памяти с адресом 21H, либо в виде абсолютного битового адреса. Соответствие этих двух способов адресации можно определить по таблице.

Адреса битов по разрядам

ПРИМЕЧАНИЕ.Адрес прямо адресуемых битов может быть записан либо в виде выражения (Адрес Байта ).(Разряд), например выражение 21.3 означает адрес третьего разряда ячейки памяти с адресом 21H, либо в виде абсолютного битового адреса, который для данного бита равен (см. таблицу) 0B.

Регистры специальных функций.

Адреса битов по разрядам

Adr

D7

D6

D5

D4

D3

D2

D1

D0

Name

ПРИМЕЧАНИЕ.Адрес прямо адресуемых битов может быть записан либо в виде выражения (Название Регистра ).(Разряд), например выражение SCON.3 означает адрес третьего разряда регистра SCON, либо в виде абсолютного битового адреса, который для данного бита равен (см. таблицу) 9B. Кроме того, некоторые биты управляющих регистров имеют собственные названия, так например данный бит имеет название TB8

К адресному пространству памяти данных примыкает адресное пространство регистров специальных функций SFR (SpecialFunctionRegister).

Регистр расширитель аккумулятора (MultiplicationRegister)

Слово состояния программы (ProgramStatusWord)

Регистр указатель стека (StackPointer)

Старший байт регистра указателя данных DPTR (DataPointerHigh)

Младший байт регистра указателя данных DPTR (DataPointerLow)

Старший байт таймера 0 ()

Младший байт таймера 0 ()

Старший байт таймера 1 ()

Младший байт таймера 1 ()

Регистр режимов таймеров счетчиков (Timer/Counter Mode Control Register)

Регистр управления статуса таймеров (Timer/Counter Control Register)

Регистр приоритетов (Interrupt Priority Control Register)

Регистр маски прерывания (Interrupt Enable Register)

Регистр управления мощностью (PowerControlRegister)

Регистр управления приемопередатчиком (Serial Port Control Register)

Буфер приемопередатчика (Serial Data Buffer)

Примечание. Регистры, символ которых отмечен знаком (*), допускают адресацию своих отдельных бит при использовании команд из группы команд операций над битами.

Адреса, по которым расположены эти регистры, приведены в таблице.

Регистры специальных функций управляют работой блоков, входящих в микроконтроллер.

Регистры-защелки SFR параллельных портов P0. P3 - служат для ввода-вывода информации.

Две регистровые пары с именами TH0, TL0 и TH1, TL1 представляют собой регистры двух программно-управляемых 16-битных таймеров-счетчиков.

Режимы таймеров-счетчиков задаются с использованием регистра TMOD, а управление ими осуществляется с помощью регистра TCON.

Для управления режимами энергопотребления микро-ЭВМ используется регистр PCON.

Регистры IP и IE управляют работой системы прерываний микро-ЭВМ,

Регистры SBUF и SCON управляют работой приемопередатчика последовательного порта.

Регистр-указатель стека SP в микро-ЭВМ рассматриваемого семейства — восьмибитный. Он может адресовать любую область внутренней памяти данных. В отличие от микропроцессора КР580ВМ80, у микро-ЭВМ семейства 8051 стек «растет вверх», т.е. перед выполнением команды PUSH или CALL содержимое SP инкрементируется, после чего производится запись информации в стек. Соответственно при извлечении информации из стека регистр SP декрементируется после извлечения информации. В процессе инициализации микро-ЭВМ после сигнала сброса или при включении питающего напряжения в SP заносится код 07Н. Это означает, что первый элемент стека будет располагаться в ячейке памяти с адресом 08Н.

Регистр-указатель данных DPTR чаще всего используют для фиксации 16-битного адреса в операциях обращения к внешней памяти программ и данных. С точки зрения программиста он может выступать как в виде одного 16-битного регистра, так и в виде двух независимых регистров DPL и DPH

Аккумулятор (АСС) является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвигов, проверка на нуль, формирование флага паритета и т.п. В распоряжении пользователя имеются 8 регистров общего назначения R0–R7 одного из четырёх возможных банков. При выполнении многих команд в АЛУ формируется ряд признаков операции (флагов), которые фиксируются в регистре PSW.

Регистр В используется как источник и как приемник при операциях умножения и деления, обращение к нему, как к регистру SFR, производится аналогично аккумулятору.

При выполнении ряда команд в арифметико-логическом устройстве (АЛУ) формируются признаки операций — флаги, которые фиксируются в регистре PSW.

Регистр флагов (PSW).

Имя и назначение

Флаг приоритета. Устанавливается и сбрасывается аппаратурно в каждом цикле команды и фиксирует нечетное/четное число единичных бит в аккумуляторе

Флаг переполнения. Устанавливается и сбрасывается аппаратурно при выполнении арифметических операций

Биты выбора используемого банка регистров. Могут быть изменены программным путем

Границы адресов ОЗУ

Флаг пользователя. Может быть установлен, сброшен или проверен программой пользователя

Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратными средствами при выполнении команд сложения и вычитания и сигнализирует о переносе или заеме в бите 3 аккумулятора

Флаг переноса. Устанавливается и сбрасывается как аппаратурно, так и программным путем

Наиболее “активным” флагом PSW является флаг переноса С, который принимает участие и модифицируется в процессе выполнения множества операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (C) выполняет функции “булева аккумулятора” в командах, манипулирующих с битами.Флаг переполнения(OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делает возможным использование арифметики в дополнительных кодах. ALU не управляет флагами селекции банка регистров (RS0, RS1), их значение полностью определяется прикладной программой и используется для выбора одного из четырёх регистровых банков.

В микропроцессорах, архитектура которых опирается на аккумулятор, большинство команд работают с ним, используя неявную адресацию. В Intel8051 дело обстоит иначе. Хотя процессор имеет в своей основе аккумулятор, он может выполнять множество команд и без его участия. Например, данные могут быть переданы из любой ячейки RDM в любой регистр, любой регистр может быть загружен непосредственным операндом и т.д. Многие логические операции могут быть выполнены без участия аккумулятора. Кроме того, переменные могут быть инкрементированы, декрементированы и проверены без использования аккумулятора. Флаги и управляющие биты могут быть проверены и изменены аналогично.

Работа с внешней памятью микроконтроллера 8051.

Обращения к внешней памяти подразделяются на обращения к внешней памяти программ и обращения к внешней памяти данных. В первом случае для формирования сигнала, активирующего ПЗУ с программой, используется сигнал PSEN, во втором — сигналы RD и WR, активизирующие ОЗУ с данными.

Если используется 16-битовый адрес, старшие восемь бит выводятся через порт Р2 , где они сохраняются в течение всего цикла обращения к внешней памяти. Отметим, что выходные каскады порта Р2 имеют внутреннюю нагрузку, несколько отличающуюся от Р1 и РЗ , благодаря чему в SFR Р2 при выводе адресной информации вовсе не обязательно защелкивать все единицы. Добавим также, что при выводе адресной информации информация из SFR Р2, хотя и не присутствует на выводах микроЭВМ, но и не теряется, восстанавливаясь на них после окончания обращений к внешней памяти (если в процессе этих обращений SFR Р2 не был модифицирован).

Если при обращении к внешней памяти данных используется восьми битный адрес, то на выводах порта остается та же информация, которая там была до начала обращения к внешней памяти. Это позволяет организовать постраничную адресацию внешней памяти данных.

Как уже отмечалось, на выводах порта P0 младший байт адреса мультиплексируется с данными. Сигналы адреса/ данных задействуют оба полевых транзистора выходного каскада порта P0. Таким образом, в этом случае выводы P0 уже не являются выводами с открытым стоком и не требуют внешних нагрузочных элементов.

Сигнал ALE используется для фиксации младшего байта адреса во внешнем регистре-защелке. Адресная информация достоверна в момент окончания сигнала ALE.

Выводимый в цикле записи байт заносится в P0 непосредственно перед активацией сигнала WR и остается неизменным до окончания этого сигнала. В цикле чтения данные на выводах P0 для достоверного считывания должны быть установившимися к моменту окончания сигнала RD.

Во время обращения к внешней памяти CPU записывает 0FFH в SFR P0, уничтожая, таким образом, хранимую там информацию. Таким образом, использовать для записи порт P0 при работе с внешней памятью надо с известной долей осторожности.

Обращение к внешней памяти программ возможно в двух случаях:

когда сигнал ЕА активен, т.е. имеет нулевой уровень,

когда программный счетчик РС содержит число больше 0FFH.

Следовательно, при использовании микро-ЭВМ, не имеющей встроенного ПЗУ или не использующей его, на входе ЕА должен присутствовать сигнал с нулевым уровнем.

Когда CPU работает с внешней памятью программ, все линии порта Р2 используются для вывода старшего байта адреса и не могут быть использованы для обычного ввода\вывода информации. При этом, как отмечалось выше, в SFR Р2 может быть занесена любая информация — адресная информация, выводимая через Р2, не зависит от состояния его SFR.

Читайте также: