Подключение ddr к плис

Обновлено: 07.07.2024

Контроллер SDRAM памяти для FPGA Altera Cyclone-4 (verilog).

Есть задачи (например захват и вывод видеосигнала) в которых не обойтись только внутри-

кристальной памятью ПЛИС, т.к. объем ее ограничен.

В таком случаи приходится рассматривать варианты подключения микросхемы внешней RAM

памяти. При этом можно использовать статическую память как самый простой вариант, но объем

микросхем подобного типа может быть недостаточен, к тому же стоимость микросхем статической

памяти весьма велика.

Если объема статической памяти не достаточно, то следующий вариант рассмотреть применение

динамической памяти SDRAM или DDR. При этом нужно понимать, что данный тип памяти сложнее в

работе чем статическая память.

Динамическая память требует строгого соблюдения всех временных параметров работы с памятью и

выполнение периодического обновления записанной информации (refresh).

Перед тем как разводить печатную плату, сначала нужно (по возможности) проверить работоспо-

собность решения на готовой плате (плате кита). Это позволяет при переходе от модели к железу

проверить работоспособность проекта или его части с минимальными потерями времени. При этом

железо (плата кита) заведомо исправно, это позволяет сконцентрироваться на разработке программной

части и не заниматься поисками проблем в только что собранной п лате !

В данной стать описана реализация контроллера SDRAM памяти.

Почему не DDR ? Работать с SDRAM памятью проще, она менее требовательна, до сих пор выпускается,

устанавливается на платах китов (DE0, DE0-NANO, DE1, DE2, DE2-115 и т.п.).

В качестве платы кита будет выступать DE0-NANO. Для отладки контроллера памяти этого хватит,

DDR оставим на следующий раз. На плате DE0-NANO установлена микросхема ПЛИС фирмы Altera

(сейчас Intel) EP4CE22F17C6 (Семейство CYCLONE 4) + микросхема SDRAM памяти фирмы ISSI

IS42S16160D-7TLI объем 32 мегабайт. Также плата содержит встроенный USB программатор.

Перед тем как начинать создавать контроллер, необходимо разыскать verilog модель микросхемы

памяти. Это необходимо для проведения моделирования работы контроллера, на модели которая

максимально приближена к реальной микросхеме памяти. Это позволит не изобретать велосипед в

виде модели SDRAM памяти, т.к. при создании модели сама модель тоже потребует времени на отладку.

Готовая модель сэкономит массу времени и сил.

Поиск модели памяти в интернете не дал результата, поэтому пришлось обратиться в службу

поддержки производителя и запросить модель памяти. Ответили быстро и без проблем прислали

Теперь необходимо определить требования к контроллеру.

Контроллер должен выполнять следующие операции:

- Начальная инициализация.

- Выполнять периодическое обновление памяти.

- Запись в память.

- Чтение из памяти.

Примечание: Зададим Programmable burst length = full page. Количество записываемых и читаемых

слов будет величиной переменной, и будет варьироваться от 1 и до full page слов. Т.е. если необходимо

произвести Запись/Чтение менее одной страницы, то длинна будет усекаться контроллером при помощи

команды BURST TERMINATE. При таком подходе контролер способен читать и писать как целыми страни-

цами, так и отдельными словами.

Для тестирования работы контролера был написан автомат (верхнего уровня) который производит

поочередную запись слов по всему массиву памяти: 0x0000, 0xffff, 0xaaaa, 0x5555 с последующей опера-

цией чтения и сравнения.

Результат операций чтения и сравнения выводятся на светодиоды.

LED7 - Операция чтения. Свечение соответствует чтению данных.

LED6 - Результат операции сравнения, (прочитанного с записанным значением) ОК.

LED5 - Результат операции сравнения, ОШИБКА.

Проект создан в среде Quartus v13.0, на языке verilog. Моделирование контроллера производится в

ModelSim ALTERA STARTER EDITION 10.1d. Исходники проекта доступны по ссылке.

После компиляции проекта, контроллер занимает 384 из 22320 логических элементов, что составляет

в районе 2 % от общей емкости кристалла Cyclone-4. На кристалле еще полно места для размещения

В статье описано подключение к процессорной системе подсистемы оперативной памяти с использованием MIG 7 Series в Vivado 2018.3. Будут рассмотрены основные моменты настройки IP ядра и его подключение к процессору MicroBlaze.

Память DDR очень часто является неотъемлемой частью многих проектов и охватывает широкий круг задач, потому включение в проект контроллеров памяти просто необходимо. MIG 7 Series поддерживает всю седьмую серию FPGA Xilinx, а также SoC Zynq-7000, и позволяет подключать DDR3 и DDR2 SDRAM, QDR II + SRAM, RLDRAM II / RLDRAM 3 и LPDDR2 SDRAM. [1]. Однако при сборке процессорной подсистемы с Microblaze возможно настроить контроллер для работы только с DDR3 и DDR2 SDRAM. Вероятнее всего, это связано с наличием AXI4 интерфейса только для этих конфигураций памяти и отсутствием такового у других. Однако эта тема выходит за рамки данной статьи, но, возможно, будет затронута в будущем.

Целью статьи является описание основных настроек MIG 7 для памяти DDR3 и DDR2 SDRAM и пояснение этапов подключения подсистемы к ядру MicroBlaze.

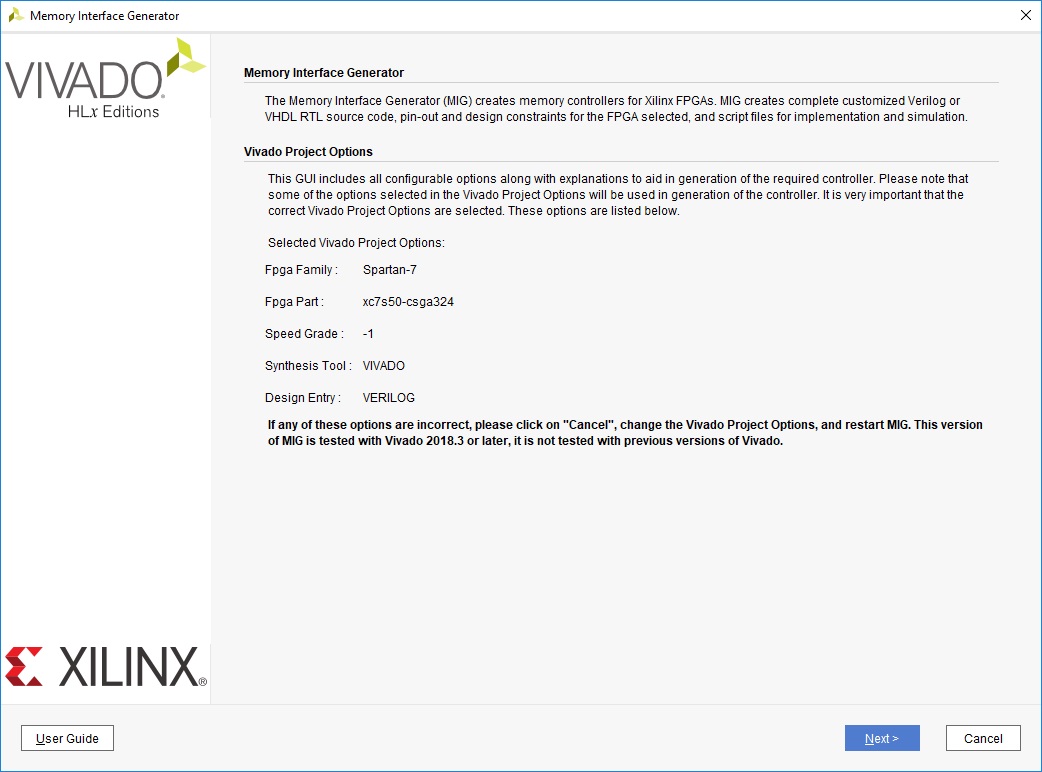

Перед началом настройки необходимо создать проект в Vivado. У меня на текущий момент установлена версия Vivado 2018.3, и создавать проект я буду под Spartan с 50К ячеек, который стоит на плате ARTY S7 от Digilent [2]. Так как это уже было описано ранее [3], повторяться не будем и сразу перейдем к моменту добавления IP Core в блок дизайне.

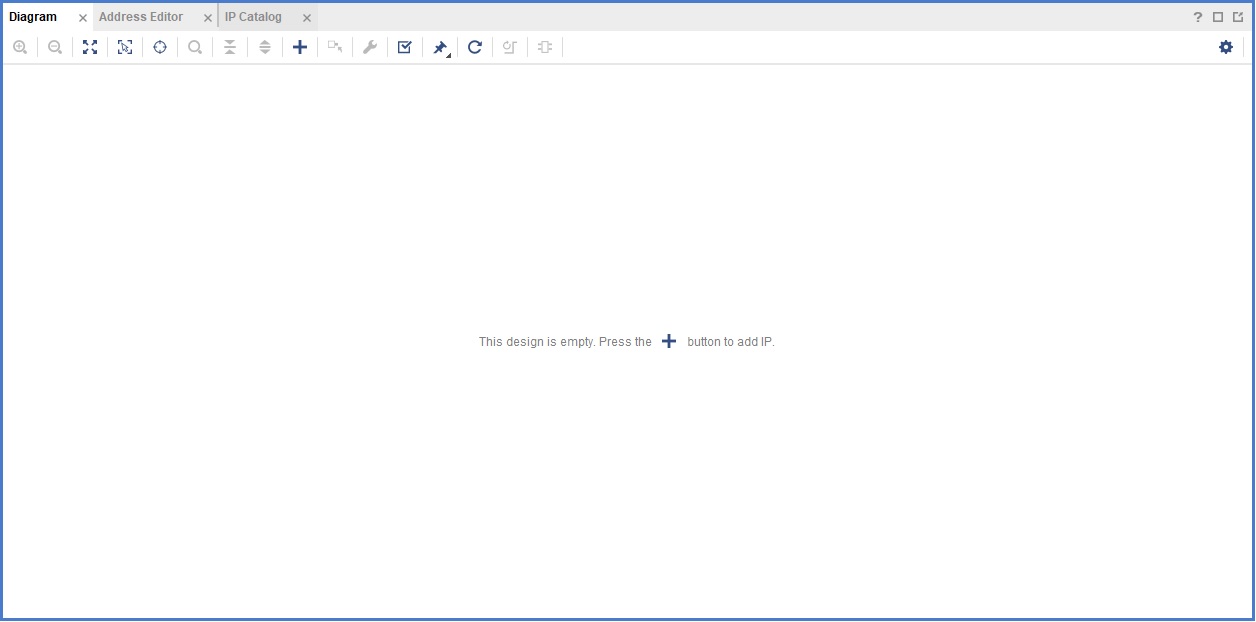

После создания проекта и блок дизайна мы видим следующее окно (рисунок 1):

Рисунок 1 – Окно Block Design

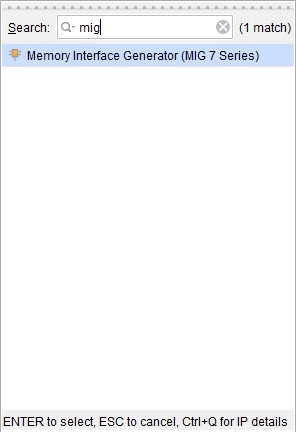

Теперь мы можем добавлять различные ядра, включая MIG 7, с него и начнем. Откроем каталог доступных ядер и введем MIG в строке поиска. Мы должны увидеть следующее окно (рисунок 2):

Рисунок 2 – Окно с доступными ядрами

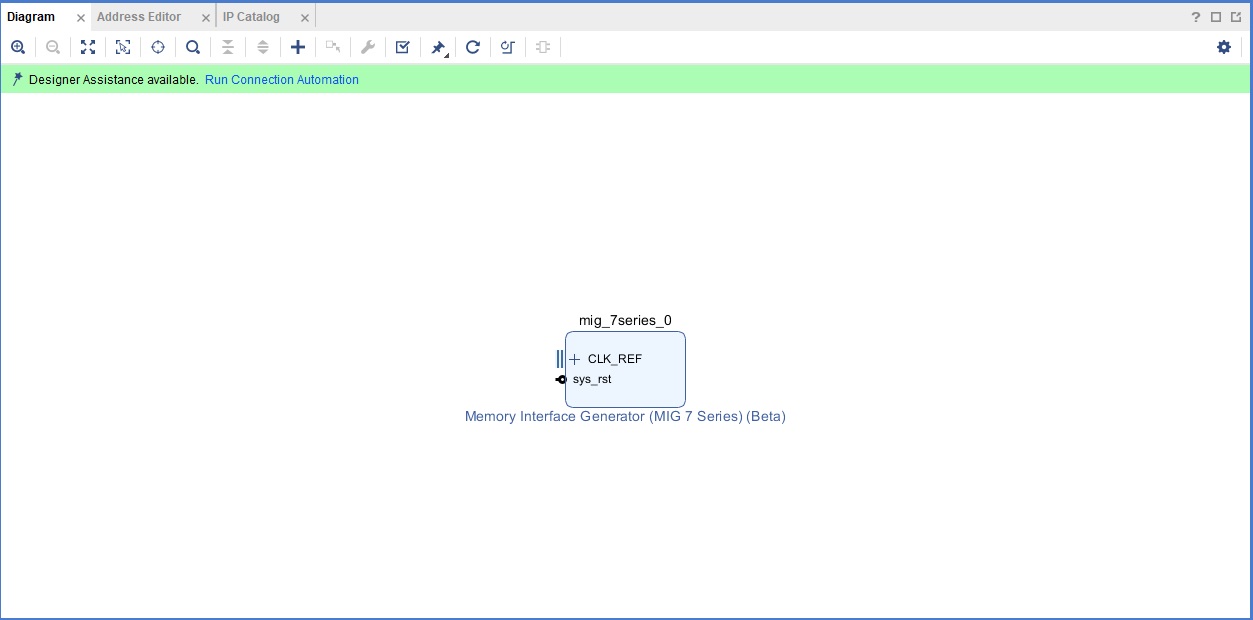

Дважды кликаем по нему и теперь можем увидеть, как он добавился в наш проект (рисунок 3).

Рисунок 3 – Окно Block Design с добавленным MIG 7

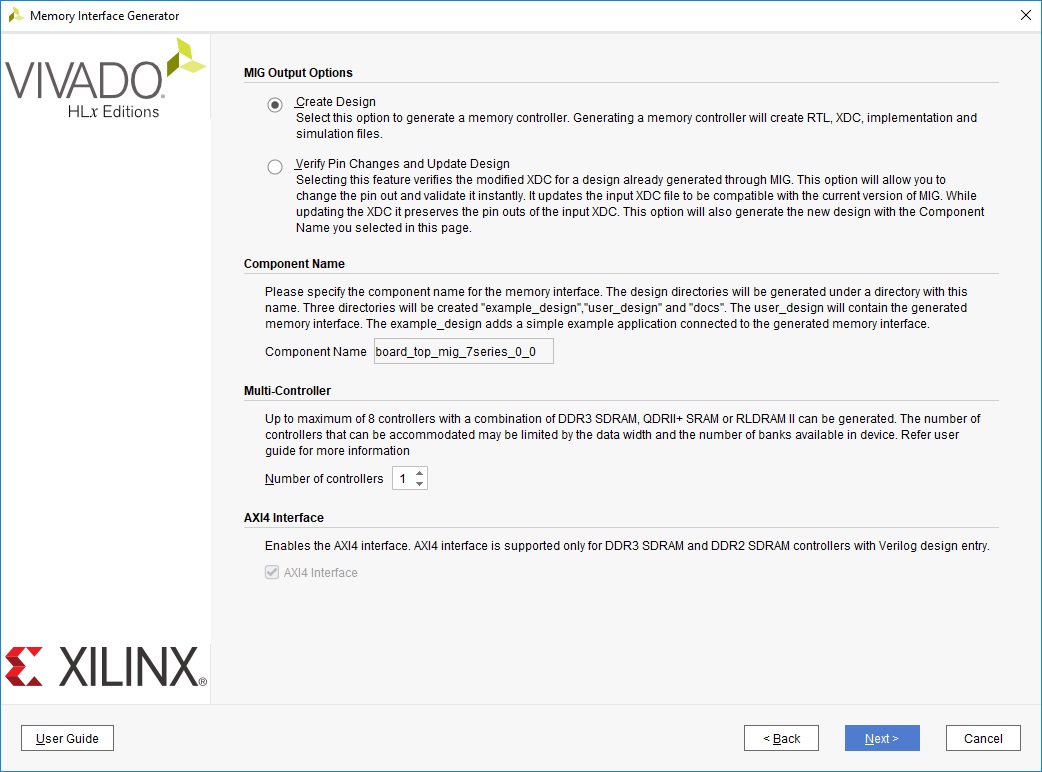

Дважды щелкнем мышкой по нему и вызовем окно настройки контроллера памяти (рисунок 4).

Рисунок 4 – Окно настройки MIG

Рисунок 5 – Вкладка настройки общих параметров

Тут мы имеем возможность выбора создания нового или верификации дизайна предыдущими настройками. Для плат Digilent’a можно найти эти настройки на гитхабе [5] и скачать или склонировать себе на компьютер. Также можно выбрать количество контроллеров в системе. Последняя неактивная вкладка должна давать нам возможность выбора интерфейса с шиной AXI. Но активной она становится только при запуске MIG из IP каталога в отдельной вкладке. Тут мы можем увидеть, что только контроллеры памяти DDR3 и DDR2 могут поддерживать эту опцию, и только если выбран Verilog как основной язык. На этой вкладке мы ничего не будем менять и потому продолжим на вкладке Pin Compatible FPGA (рисунок 6).

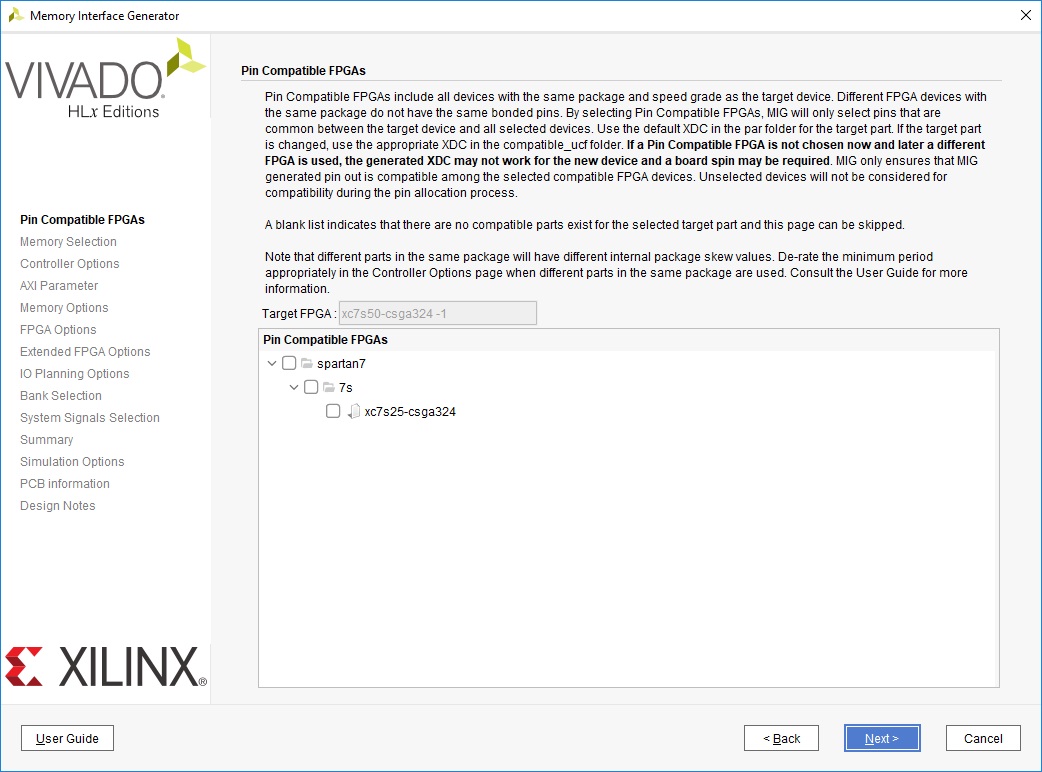

Рисунок 6 – Вкладка Pin Compatible FPGA

На текущей вкладке мы можем выбрать дополнительные FPGA, совместимые с нашей по корпусу и температуре. При выборе дополнительно совместимых FPGA, MIG будет резервировать только те выводы, которые являются общими для всех выбранных микросхем. Так как сейчас нам это не нужно, мы можем продолжить и перейти к вкладке Memory Selections (рисунок 7).

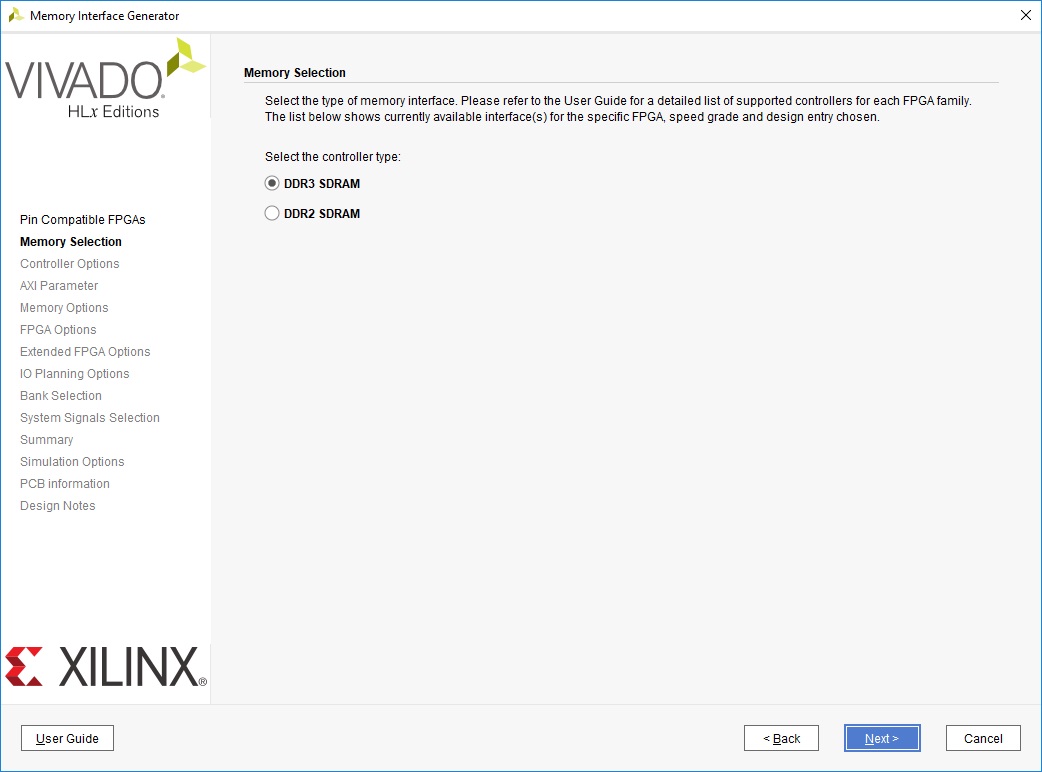

Рисунок 7 – Вкладка Memory Selection

Здесь мы выбираем необходимую нам память. На платах Digilent’a стоят микросхемы памяти DDR3, поэтому для моей платы ничего менять не нужно. Нажимаем «продолжить» и переходим к следующей вкладке (рисунок 8).

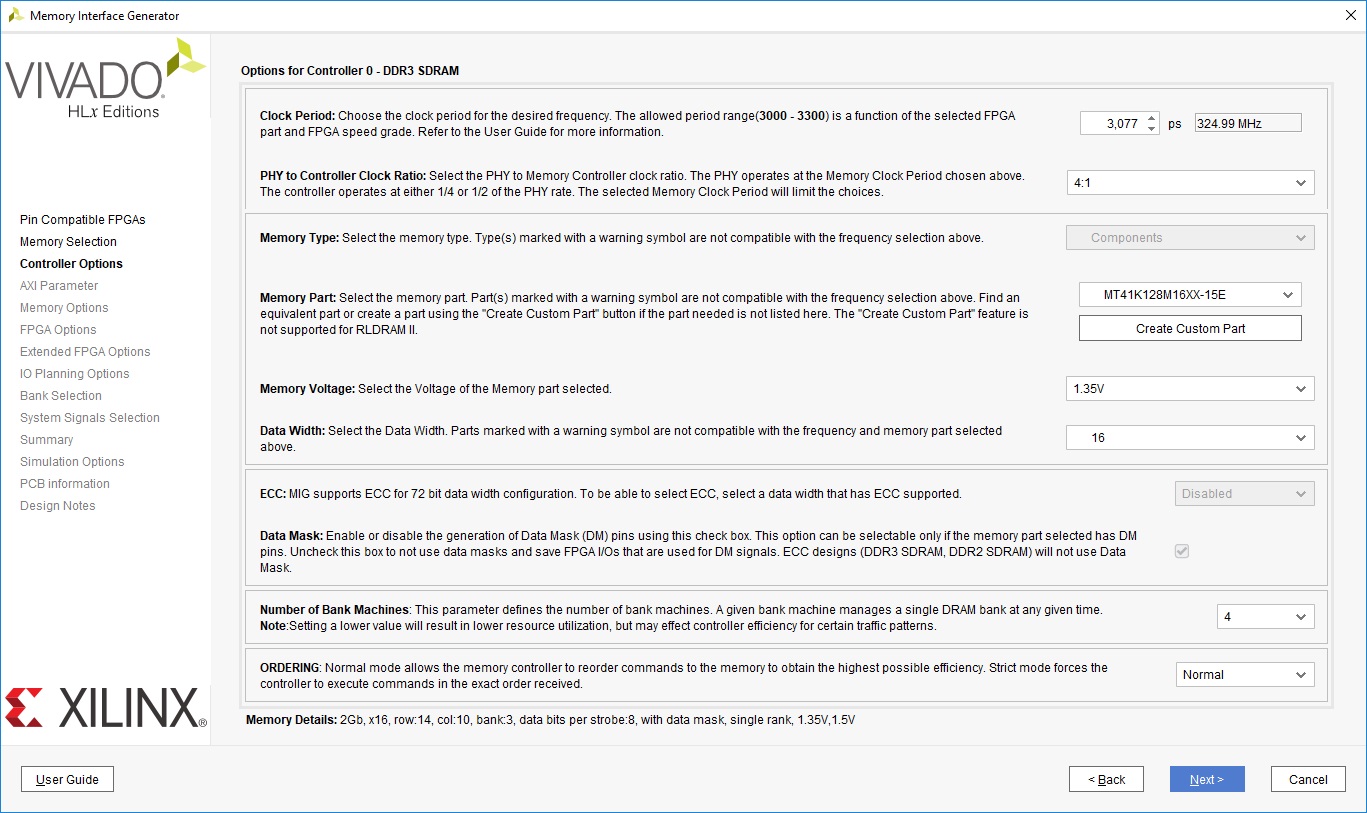

Рисунок 8 – Вкладка Controller Options

На этой вкладке мы выбираем частоту контроллера, частоту системного клока и настраиваем память. Мои настройки на этой странице совпадают с настройками Digilent’a, но на других платах они могут отличаться. Частота памяти настраивается в соответствии с вашей FPGAи ее Speed Grade’ом. Вторая строка настройки определяет отношение частоты работы памяти к частоте пользовательского клока. В нашем проекте этим клоком будет тактироваться MicroBlaze.

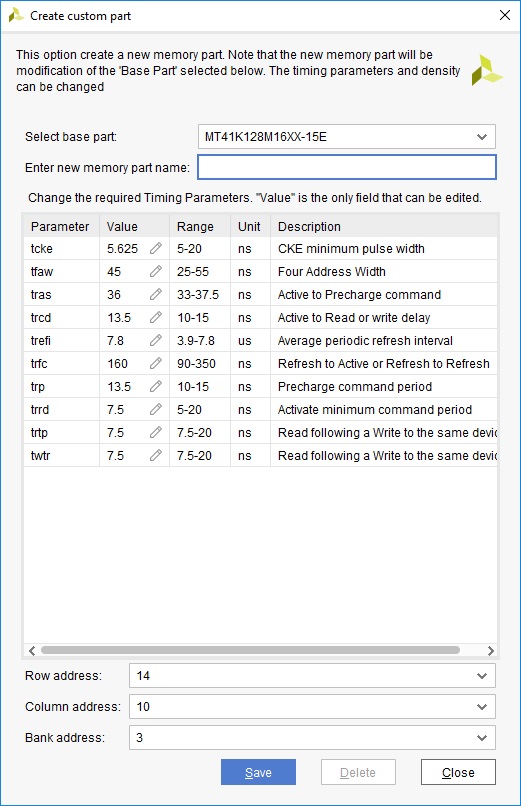

Следующий блок настраивает физические параметры используемой памяти. Временные параметры можно выбирать из некоторого количества предустановленных конфигураций, но даже если ее найти не получилось, можно создать свою конфигурацию на основе одной из имеющихся (рисунок 9).

Рисунок 9 – Настройка временных параметров

Все временные параметры можно найти в документации на вашу память. Напряжение питания и ширина шины данных также находятся в этой документации.

Number of Bank Machines оставим по умолчанию, а параметр Ordering сменим на Normal. Это должно повысить эффективность, так как дает контроллеру изменять приоритеты обращения к памяти автоматически, но принципиально никак не должно повлиять на будущий вид этого IP. Теперь можно перейти к следующей вкладке (рисунок 10).

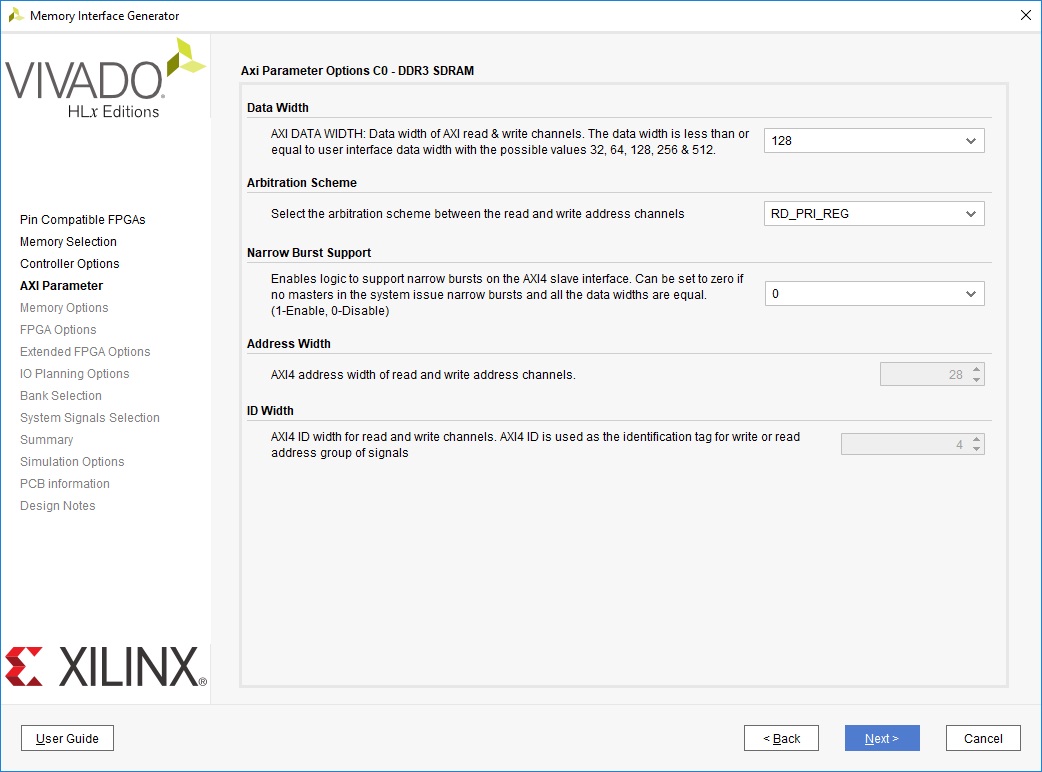

Рисунок 10 – Вкладка AXI Parameters

На данной вкладке требуется настроить внутреннюю шину, через которую наше ядро будет подключаться к Microblaze. Ширину шины данных можно выбрать из предложенных значений, но не меньше ширины подключаемого пользовательского интерфейса. Вторая вкладка определяет порядок приоритетов чтения и записи. Третья вкладка позволяет включить поддержку Narrow Burst. Она необходима, если ширина шин устройств не совпадает, однако, как указано в документе [4], XPS в состоянии сама рассчитать необходимость ее поддержки после анализа подключенных мастеров к шине. Оставим все настройки по умолчанию и перейдем к вкладке Memory Options (рисунок 11).

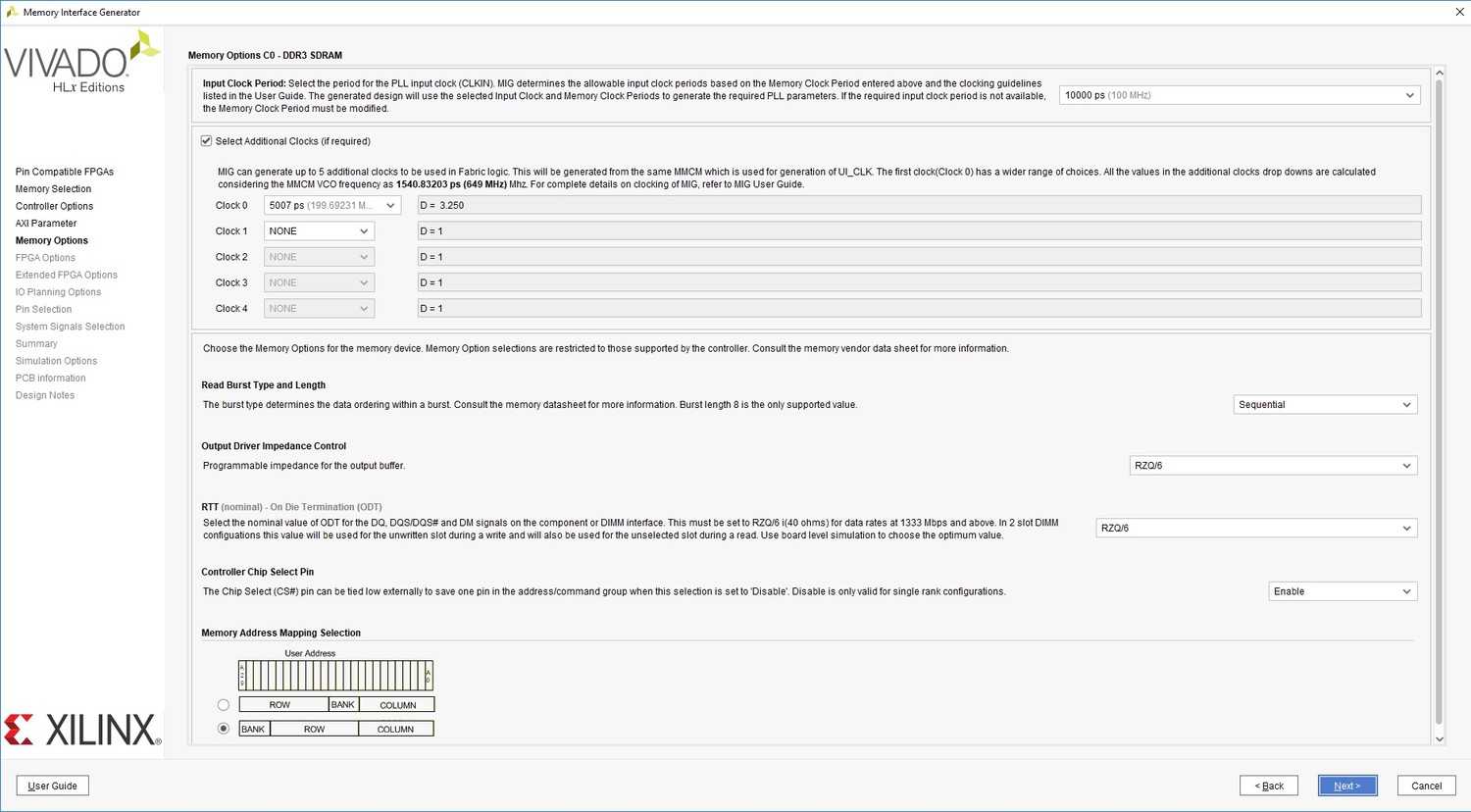

Рисунок 11 – Вкладка Memory Options

На этой вкладке мы настраиваем входные и выходные клоки, а также импеданс буферов и терминальных резисторов. На ARTY S7 в банке с DDR стоит генератор на 100 МГц, поэтому выбираем его как входной клок. Также дополнительно генерируем 200 МГц, они понадобятся нам в будущем для опорного клока. Помимо 200 МГц, можно вывести до пяти других частот, если такие понадобятся в нашем проекте. Если нужные частоты получить не удается, можно попытаться вернуться назад и изменить частоту памяти.

Burst Type and Length настраивает тип пакетных передач. Для DDR3 и DDR2 длина может быть только 8. Output Driver Impedance Control и ODT выставим в соответствии с настройками Digilent’a. При настройке другой платы выходной импеданс нужно искать в документации. Остальные настройки оставим по умолчанию и перейдем на вкладку FPGA Options (рисунок 12).

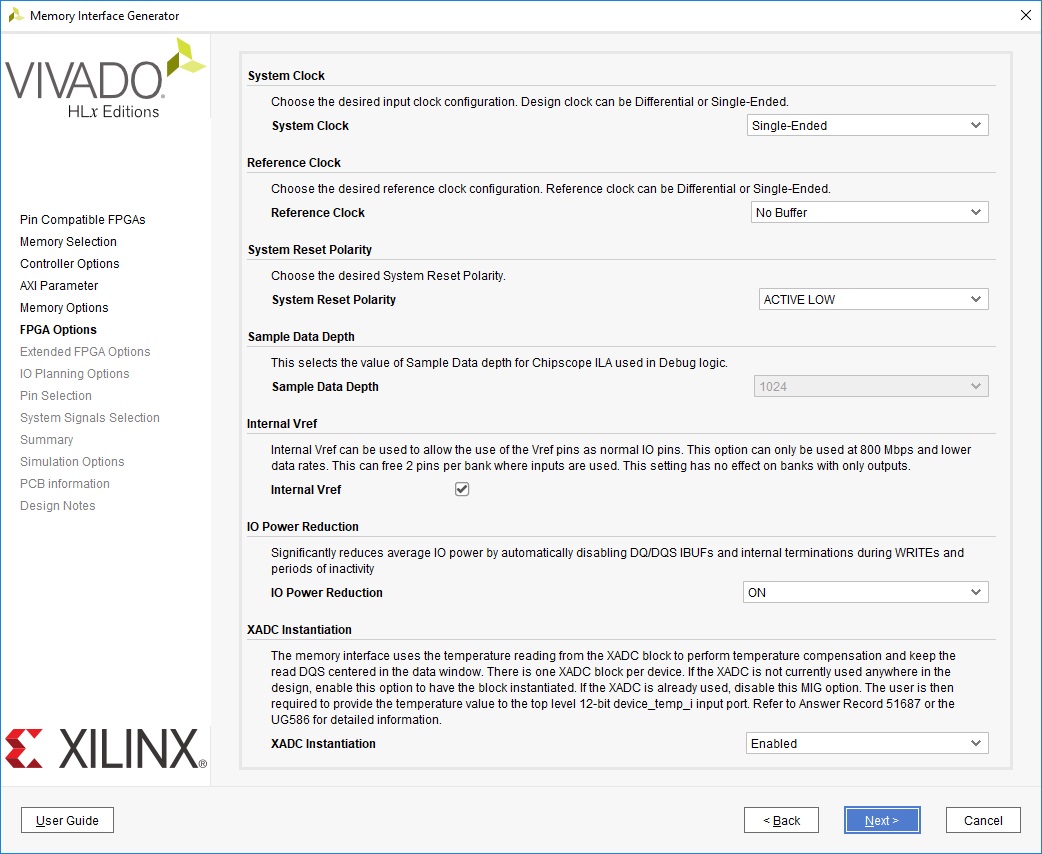

Рисунок 12 – Вкладка FPGA Options

Выбираем входную частоту как Single-Ended и опорную частоту как No Buffer. Опорную частоту можно тактировать и от входной частоты, если она входит в диапазон от 199 МГц до 201 МГц. Она нужна для тактирования модулей IDELAYCTRL и элементов IDELAY в банке ввода-вывода, подключаемом к памяти. Установим галочку напротив Internal Vref. Это позволит сэкономить выводы, отведенные под опору, и использовать их в проекте как Single-Ended. Однако это возможно только на скоростях передачи ниже 800 Mbps. Также оставим включение XADC в ядро, потому что использовать его в проекте больше не планируем. Пропустим вкладку Extended FPGA Options, потому что там ничего менять не будем, и перейдем на вкладку IO Planning Options (рисунок 13).

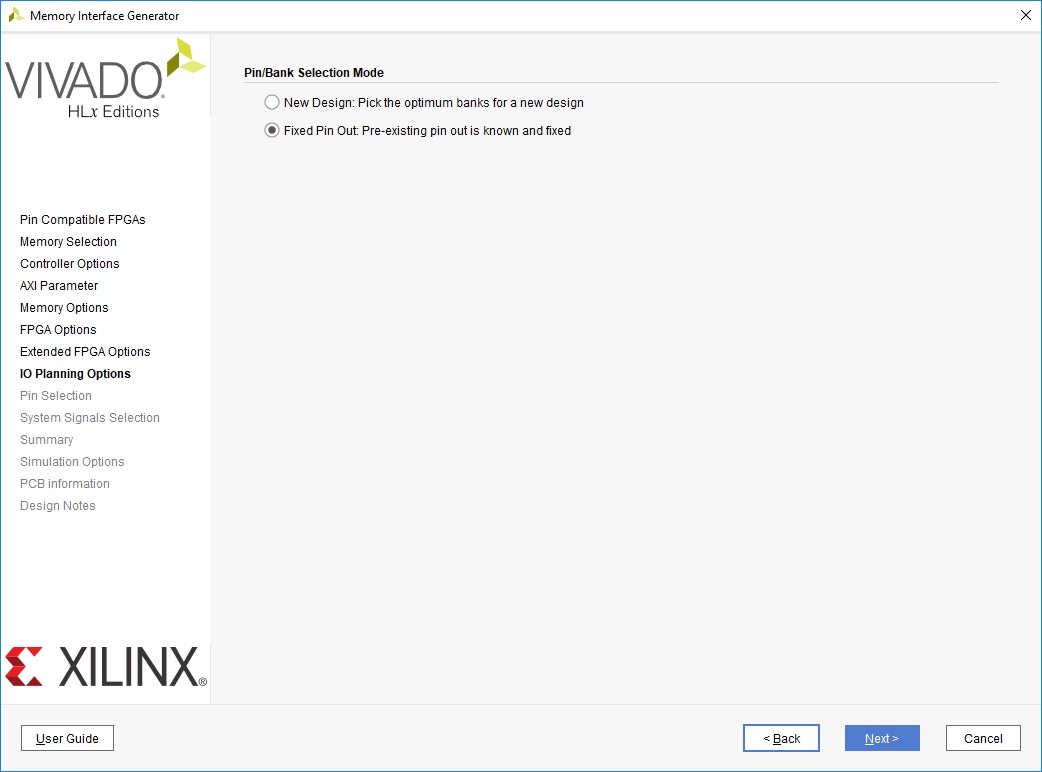

Рисунок 13 – Вкладка IO Planning Options

От выбора на этой вкладке зависит то, как будут назначены сигналы для памяти. Если ядро генерируется для нового проекта, то можно зарезервировать выводы в соответствии с группами байт. Мы же воспользуемся вторым вариантом, так как наши пины уже известны заранее. На следующей вкладке Pin Selection увидим следующую картинку (рисунок 14):

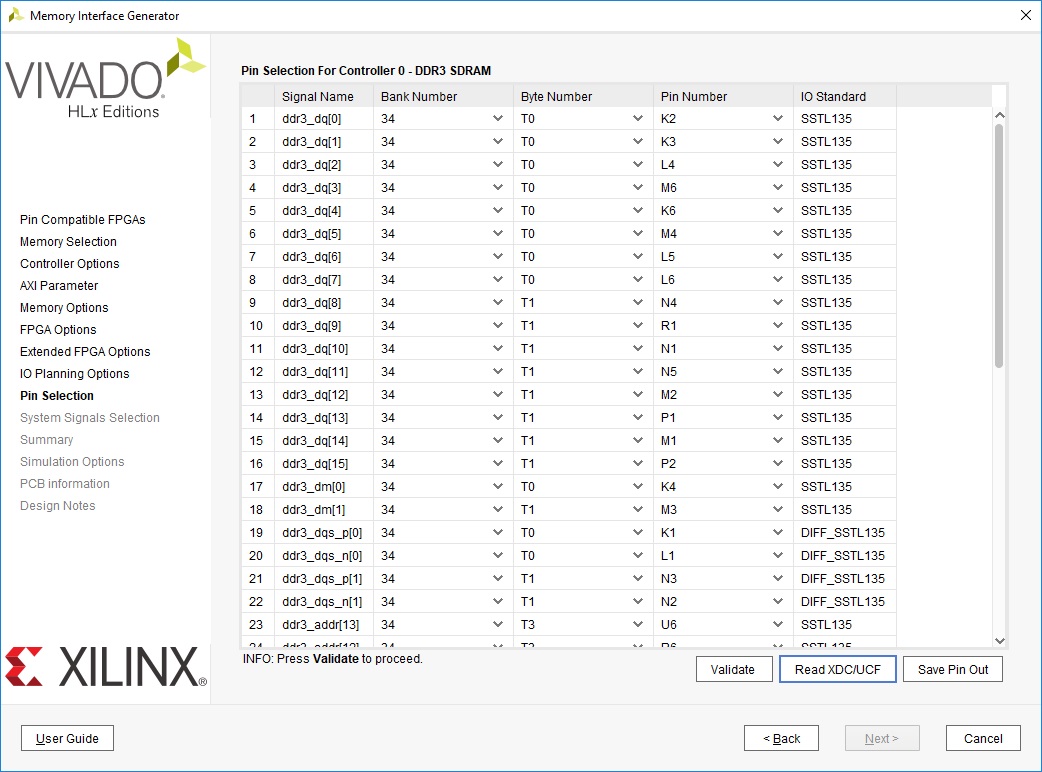

Рисунок 14 – Вкладка Pin Selection

Воспользуемся констрейнами от Digilent’a, нажав кнопку Read XDC/UCFи выбрав соответствующий файл из репозитория. Для каждого сигнала должны обновиться номера выводов и их стандарты. Нажимаем на кнопку Validate и, если все нормально, переходим к следующей вкладке (рисунок 15).

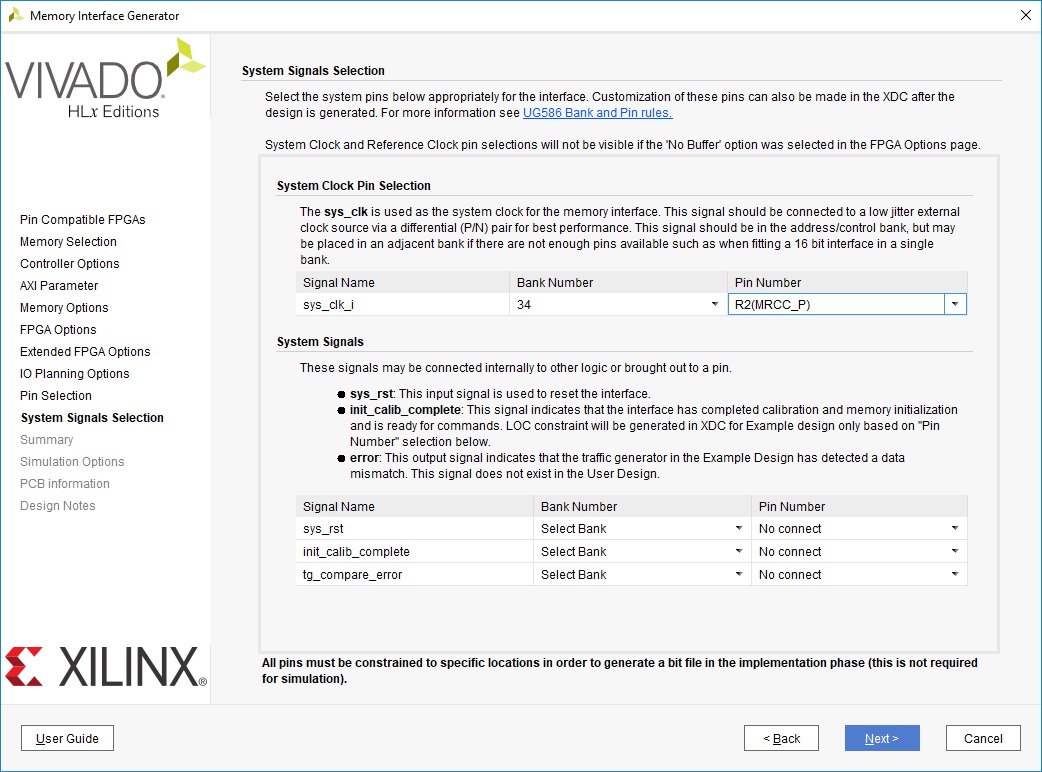

Рисунок 15 – Вкладка System Signals Selection

Выбираем выводы для задействованных сигналов. Так как внешним у нас является только системный клок, то назначаем ему один из предложенных выводов, предварительно сверившись со схемой отладочной платы. Генератор подключен на вывод R2, его и выбираем. Больше нас на этой вкладке ничего не интересует.

На оставшихся вкладках нет никаких настроек, потому с ними можно ознакомиться самому, принять лицензионное соглашение и на последней нажать кнопку Generate.

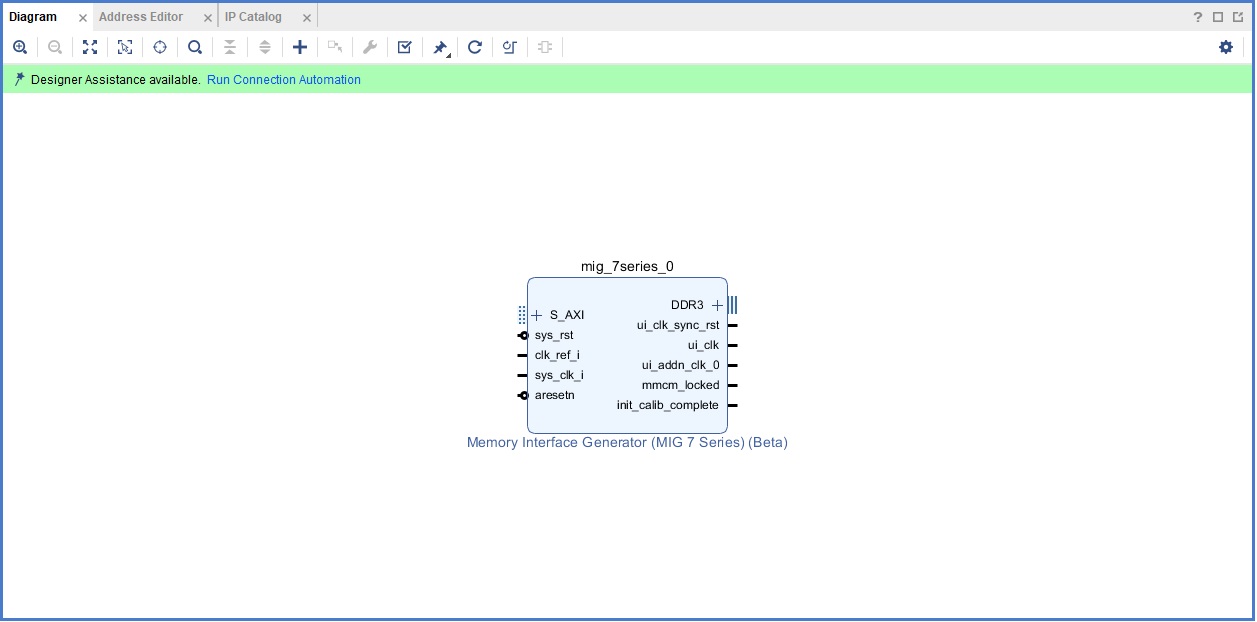

В результате чего наше ядро должно преобразоваться и принять следующий вид (рисунок 16):

Рисунок 16 – Окно Block Design с обновленным MIG 7

Подключение процессора к памяти

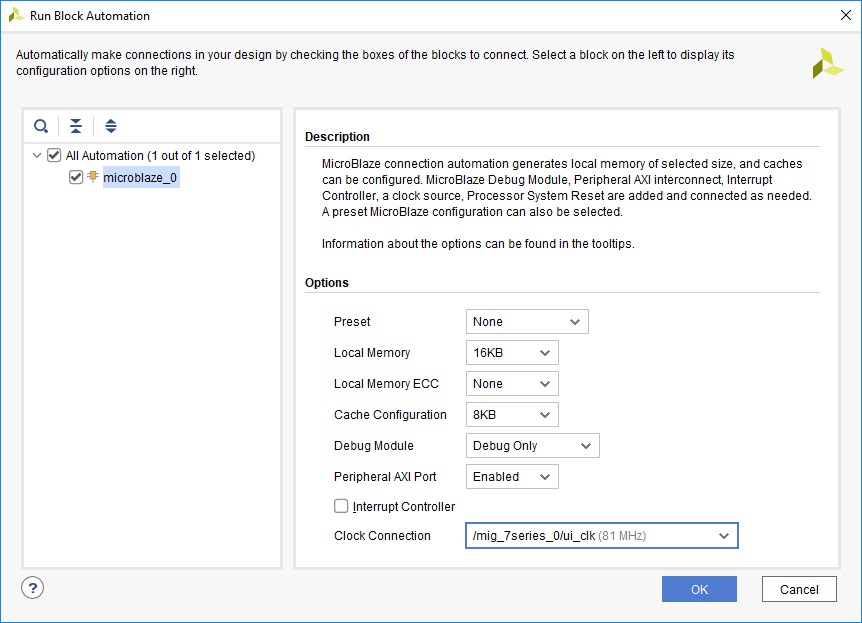

Теперь мы можем добавить MicroBlaze в наш проект. Нажимаем кнопку Add IP и добавляем его в рабочее пространство. Запустим Run Block Automation и установим следующие параметры (рисунок 17):

Рисунок 17 – Настройки для Microblaze

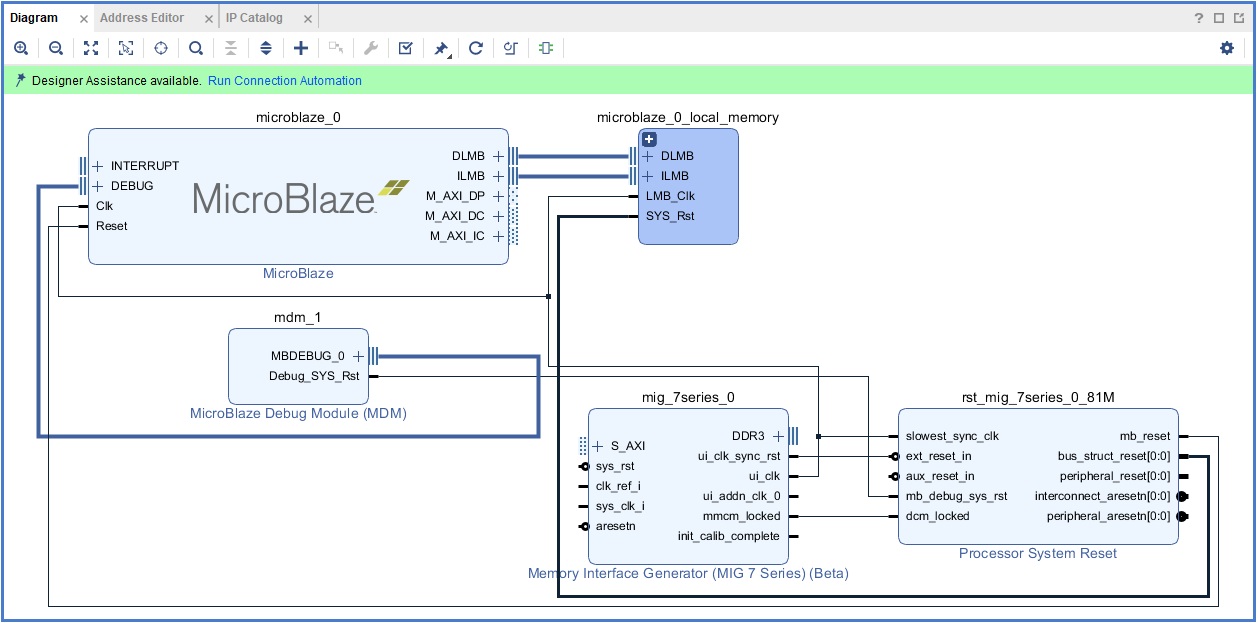

После завершения автоматизации появятся локальная память, модуль дебага и модуль сброса (рисунок 18).

Рисунок 18 – Окно Block Design после автоматизации

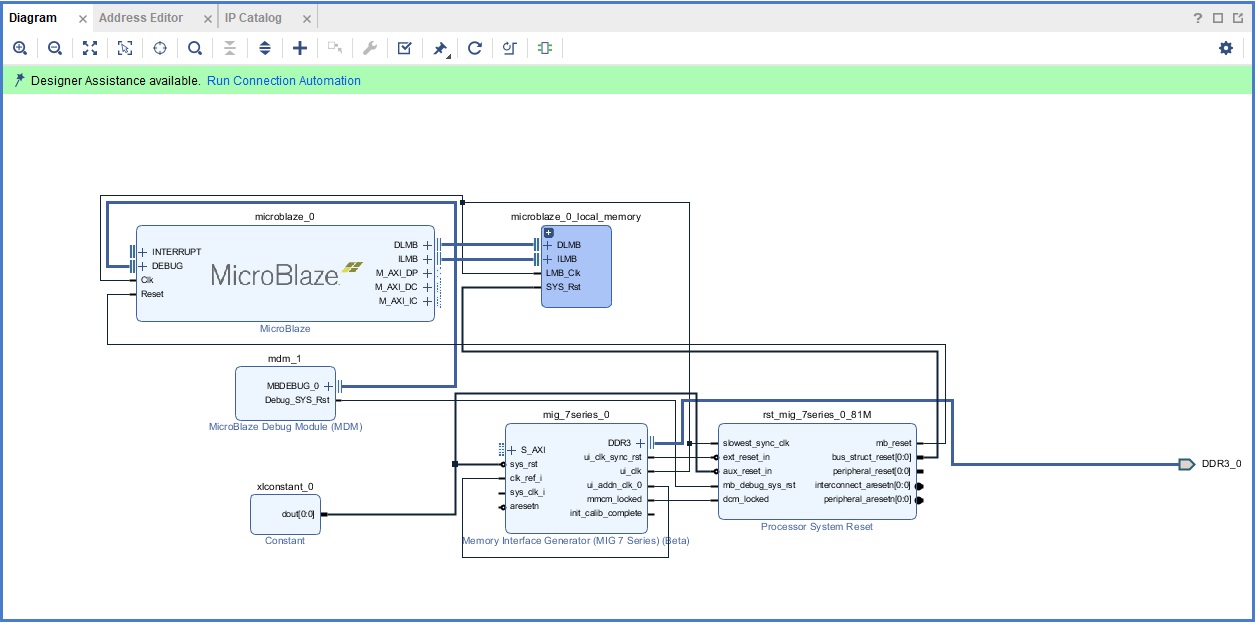

Добавим подтяжку к «1» для входов сброса, подключим опорную частоту к 200 МГц и выведем наружу сигналы памяти DDR. Окно теперь должно выглядеть вот так (рисунок 19):

Рисунок 19 – Окно Block Design после автоматизации

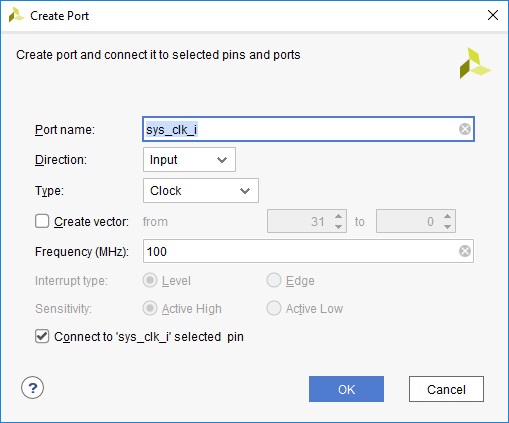

Теперь добавим внешний порт к нашей входной частоте. Нажмем один раз на sys_clk_i в блоке MIG 7, чтобы выделить его, затем в свободном поле щелкнем правой кнопкой мыши и выберем пункт Create Port. Должно открыться следующее окно (рисунок 20):

Рисунок 20 – Создание порта

Оставляем все по умолчанию и нажимаем Ok. Если просто выбрать опцию Make External, Vivado создаст внешний порт с именем, отличным от того, которое было создано в файле констрейнов, и на этапе синтеза и имплементации появится критическое предупреждение, указывающее на отсутствие в дизайне порта с именем sys_clk_i.

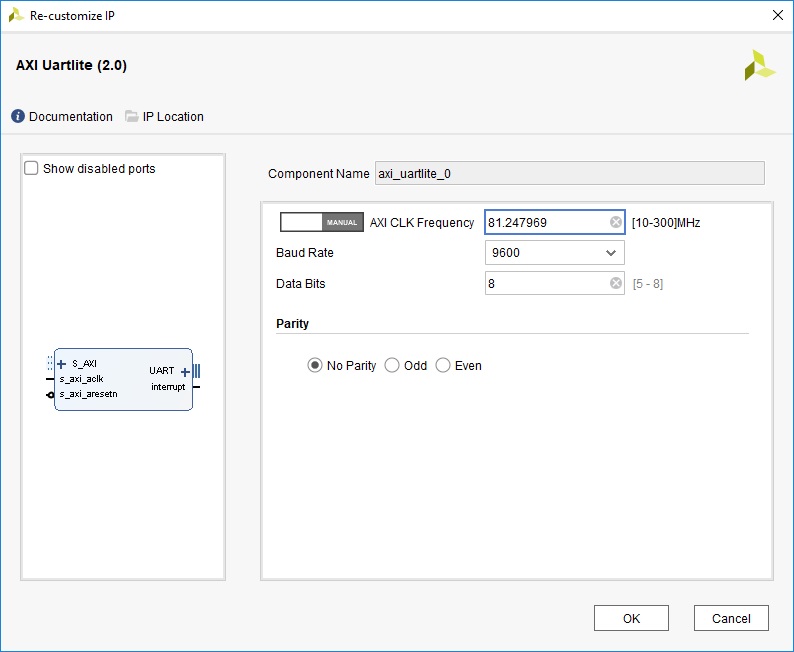

Добавим модуль UARTLite и сконфигурируем его следующим образом (рисунок 21):

Рисунок 21 – Конфигурация UARTLite

Установленная частота соответствует частоте, сгенерированной MIG 7 для пользовательского интерфейса. UART нам понадобится позже для теста памяти

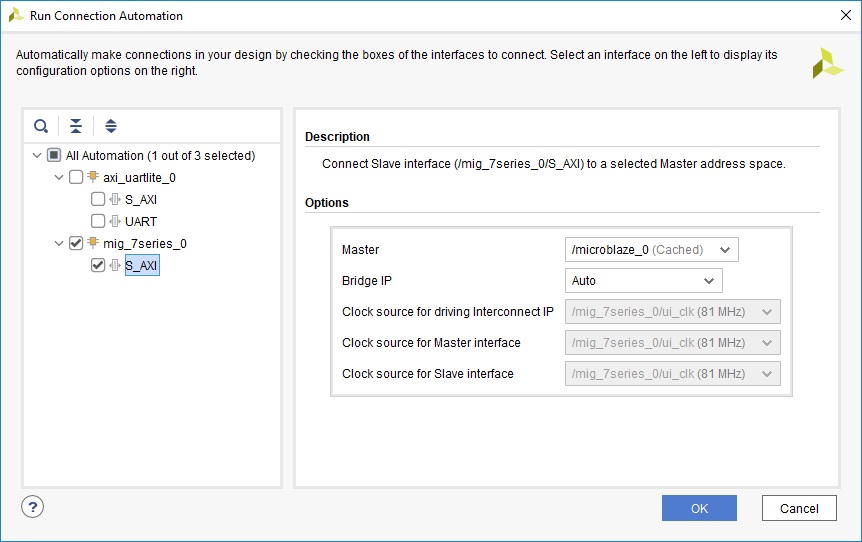

Теперь запустим Run Connection Automation для кэша MicroBlaze (рисунок 22).

Рисунок 22 – Run Connection Automation для кэша MicroBlaze

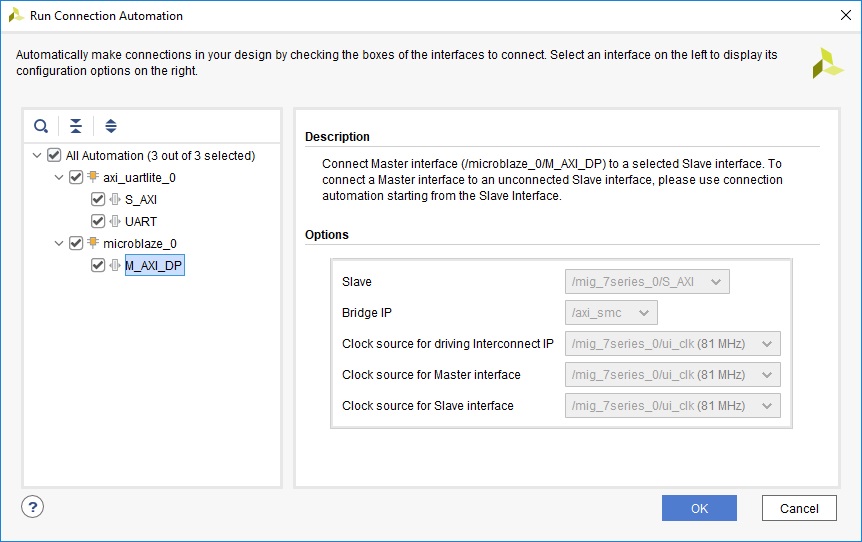

Теперь запустим автоматизацию подключения периферии (рисунок 23).

Рисунок 23 – Run Connection Automation для периферии

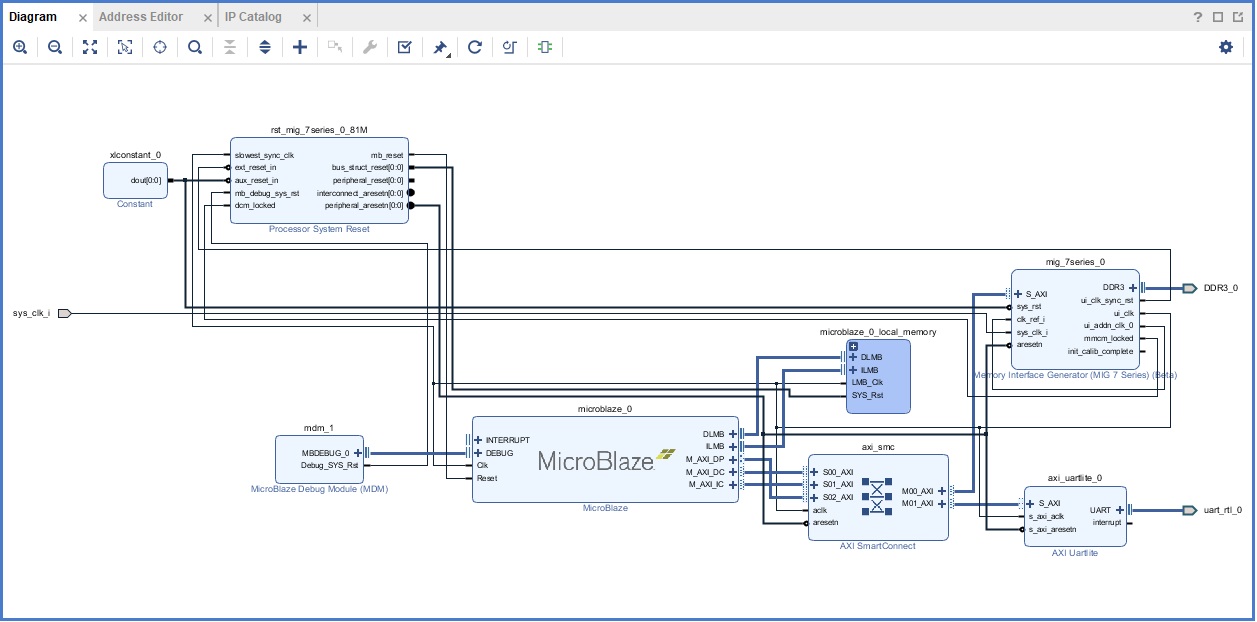

После этого нажмем кнопку Optimize Routing и получим следующее поле блок дизайна (рисунок 24):

Рисунок 24 – Окно Block Design после регенерации

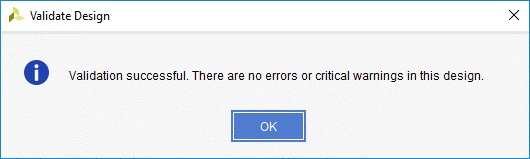

Теперь можно запустить Validate Design, и, если все правильно, мы получим следующее уведомление (рисунок 25):

Рисунок 25 – Уведомление об успешной проверке

Запустим синтез, предварительно создав обертку нашего блок дизайна, и немного подождем.

После синтеза откроем I/O Planning и назначим оставшимся сигналам порты. Сохраним свой констрейн файл и запустим генерацию битстрима. Если никаких ошибок и критических предупреждений не появилось, то после ее окончания выберем File -> Export -> Export Hardware без битстрима, а затем запустим SDK.

Запуск проверки памяти

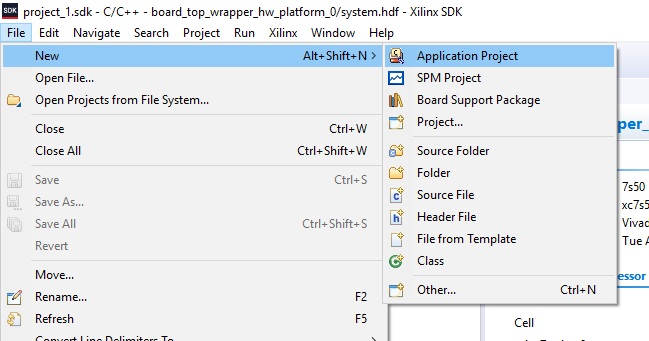

После запуска SDK создадим Application Project (рисунок 26):

Рисунок 26 – Создание нового проекта

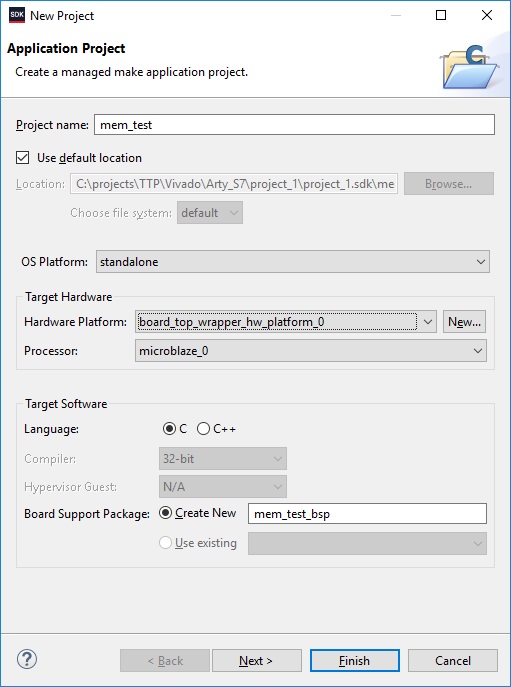

Выставим следующую конфигурацию в первой вкладке создания проекта (рисунок 27):

Рисунок 27 – Конфигурация на первой вкладке

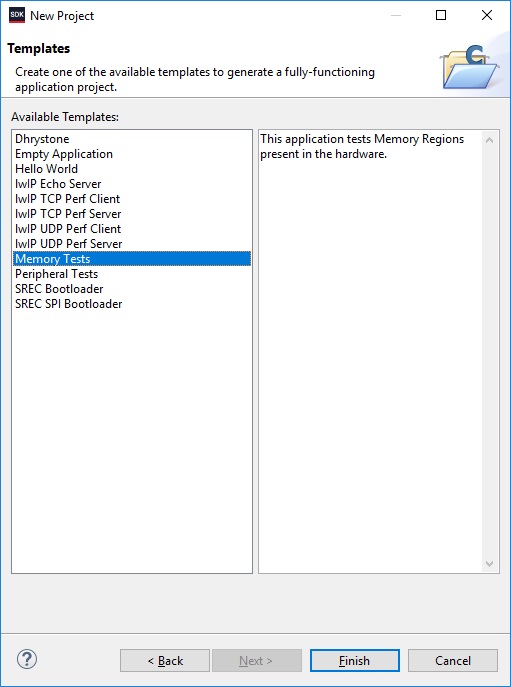

На второй вкладке выберем шаблон проекта Memory Tests (рисунок 28).

Рисунок 28 – Шаблоны проектов

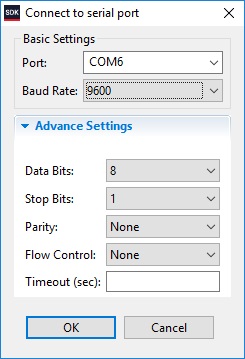

Теперь добавим и запустим SDK Terminal со следующими настройками, исключая номер COM-порта, так как он у вас может быть любым другим (рисунок 29):

Рисунок 29 – Настройки COM-порта

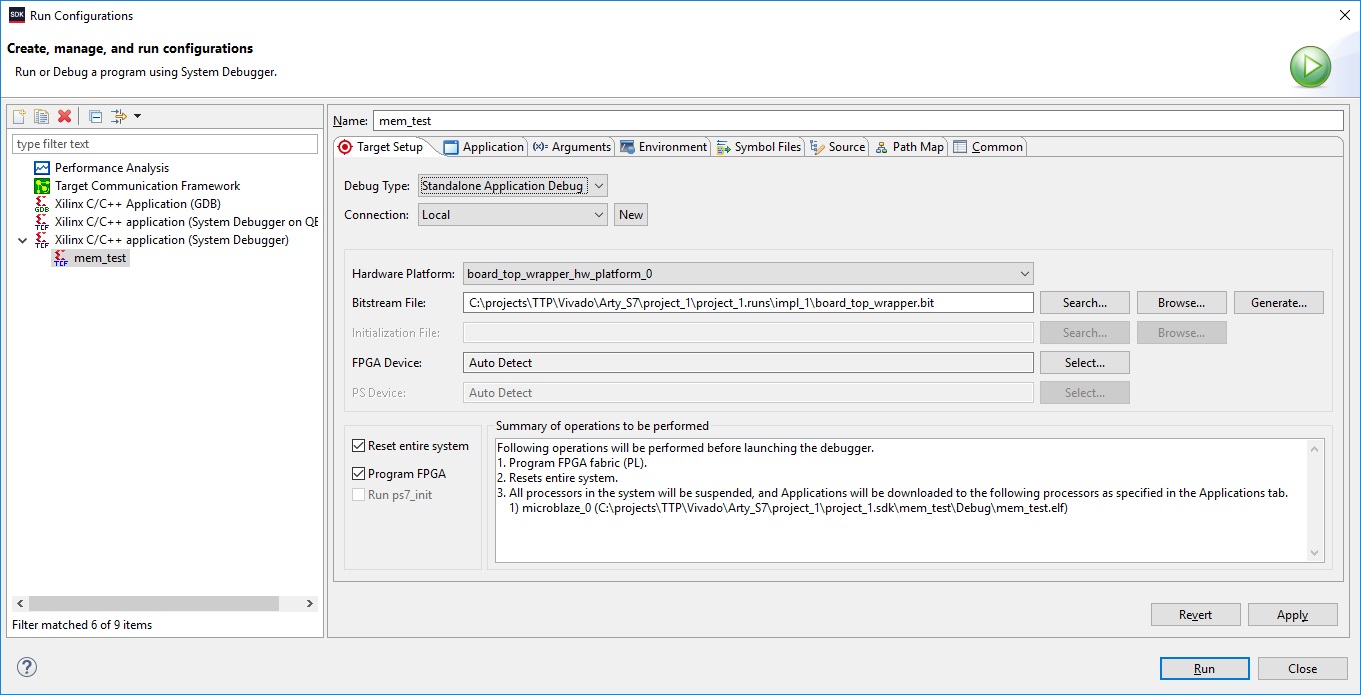

Теперь настроим Run Configuration (рисунок 30).

Рисунок 30 – Настройка Run Configuration, вкладки Target Setup

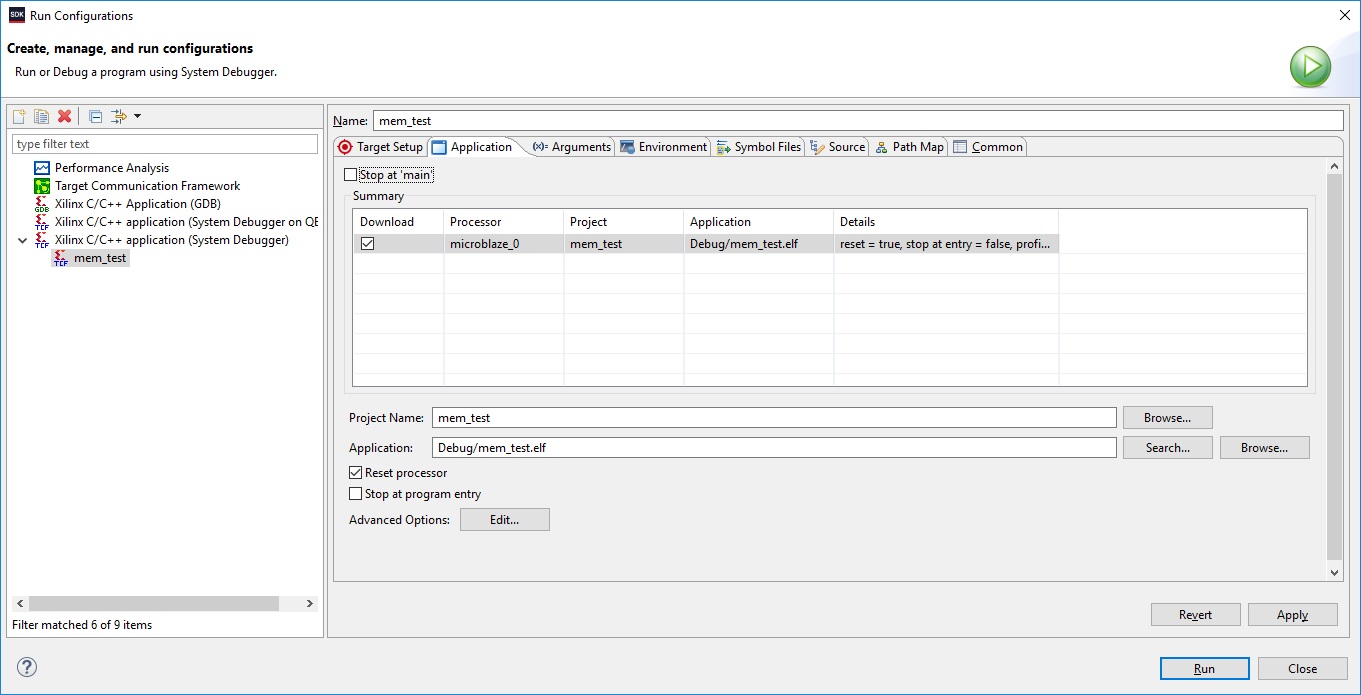

И во второй вкладке (рисунок 31):

Рисунок 31 – Настройка Run Configuration, вкладки Aplication

Теперь запустим программирование нашей FPGA. Если все было сделано правильно, то в строке терминала мы увидим похожую запись (рисунок 32):

Это означает, что тест нашей памяти был пройден и все настроено правильно. Теперь можно самостоятельно посмотреть файлы тестового проекта и попытаться в них разобраться. Если возникли ошибки, то можно вернуться к самому началу или попытаться почитать предыдущие статьи о настройке процессорной системы MicroBlaze.

Вы можете написать сейчас и зарегистрироваться позже. Если у вас есть аккаунт, авторизуйтесь, чтобы опубликовать от имени своего аккаунта.

Примечание: Ваш пост будет проверен модератором, прежде чем станет видимым.

Последние посетители 0 пользователей онлайн

Похожий контент

Я использовал такие микроконтроллеры как arduino и stm32 для управления LCD, я хотел бы знать, как управлять LCD с помощью FPGA, следующее вложение - лист данных LCD.Datasheet STONE STWI070WT-01.pdf

Требуется инженер-программист ПЛИС для проектирования плат и написания прошивок для нескольких проектов.

Требования к кандидату:

- Опыт работы с различными типами ПЛИС не менее 3 лет

- Опыт работы с микроконтроллерами STM32 и другими не менее 3 лет

- Опыт работы с Altium Designer, Quartus и другими средами.

- Опыт видеообработки с помощью ПЛИС

- Опыт работы в команде

- Умение разбираться в чужих проектах

- Проживание в Москве, желательно поближе к Люберецкому району

Немного общей информации по проектам:

1. Видеообработка (2 проекта) - ключевые моменты: сглаживание изображений, работа с видеобуфером, работа с MIPI, PAL/SECAM видеовыходом, работа ПЛИС в паре с микроконтроллером

2. Обработка сигналов (1 проект) - ключевые моменты: работа ПЛИС в паре с микроконтроллером, работа с таймером, точные временные измерения, детектирование аналоговых и цифровых сигналов, работа с оптическими датчиками

Оплата договорная

Есть перспектива трудоустройства на штатную должность.

Добрый день всем!

Подскажите пожалуйста куда мне двигаться дальше и с чего начать вообще.

Фотографии ПЛИС и сетевого модуля прилагаю.

Несмотря на то, что современные FPGA содержат внутренние блоки памяти (BRAM), количество этой доступной памяти всегда на порядки меньше, чем может быть с выделенными внешними микросхемами. Так что не сюрприз, что многие разработчики FPGA подключают некоторые типы памяти к своим проектам. В частности, микросхемы SDRAM очень популярны, так как они достаточно быстрые, имеют большую емкость и недорогие. К сожалению, управлять динамической памятью не так же просто, как статической, так что для этого часто используется контроллер SDRAM.

Для нашего контроллера мы будем подключать возможно самую простую их доступных SDRAM: Micron MT48LC1M16A1 16Mb SDRAM. Нашей тестовой системой будет Xylo-E, Xylo-EM и Xylo-LM (Xilinx или Altera FPGA с памятью от 16Mb до 256Mb SDRAM).

[От статики к динамике]

Представим себе, что нужно подключить 16Mb память к FPGA.

16Mb означает, что в памяти хранится 16 миллионов бит (или, если быть точным, 16777216 бит). Очень редко биты адресуются индивидуально, обычно они обрабатываются порциями по 8 или 16 (мы называем эти порции словами). Так что если наша память 16Mb организована как 1M слов по 16 бит, то понадобится 20-разрядная шина адреса и 16-разрядная шина данных, плюс сигналы разрешения записи (write enable, WE) и разрешения чтения (read enable, RE).

Реальные микросхемы памяти также имели бы сигнал выборки CS (chip select), и если память синхронная, еще и тактовый сигнал (на картинке для ясности эти сигналы опущены).

Стоит сделать оговорку, что если память находится внутри FPGA (так называемая блочная память BRAM), то она конечно совсем другая - нет BRAM такого размера. Просто предположим, что такая память 16Mb BRAM существует.

Как Вы можете видеть, это все еще один блок памяти, но здесь 2 адресные шины, это так называемая двухпортовая память (dual port memory BRAM), которая присутствует на современных кристаллах FPGA. Такая память позволяет двум агентам получить доступ к массиву памяти одновременно. Обычно один агент записывает в память, в то время как другой агент читает. Таким образом, у памяти есть независимые шины адреса и данных для каждого агента. Рисунок выше показывает, что шины первого (записывающего) агента находятся сверху, и шины второго (читающего) снизу. Более продвинутые BRAM позволяют каждому агенту и читать и записывать, но чаще всего используется архитектура, показанная выше. Также BRAM обычно используются синхронно, так что каждый агент предоставляет сигнал тактов (не показан на рисунке).

Показанная до сих пор память статическая, это означает, что данные в ней хранятся до тех пор, пока подано питание. Также статическую память можно рассматривать как линейный массив слов. Вы просто предоставляете адрес, чтобы получить доступ к соответствующим данных, никакой дополнительной сложности. Платить за это приходится высокой стоимостью каждого бита, которая намного больше, чем у динамической памяти (SDRAM).

Динамическая память. Перейдем к SDRAM, которая является динамической памятью (dynamic, отсюда появилась "D" в аббревиатуре SDRAM). И в динамической памяти мы больше не увидим линейную организацию слов, вместо этого память организована как матрица слов со строками и столбцами (row, column).

Рисунок выше показывает 12 бит на строку и 8 бит на столбец, и всего получается 20 бит адреса.

Здесь есть одно усложнение: чтобы повысить быстродействие, каждая память делится на одинаковые по размеру куски, которые называются "банками". Это потому что операции с динамической памятью медленные, и делением памяти на банки позволяет работать с одним из банком, ожидая готовности к работе другого банка.

Если в нашей памяти 16Mb SDRAM есть 2 банка, то в каждом будет 8Mb.

Когда осуществляется доступ к SDRAM, FPGA выбирает банк (bank, 1 бит), строку (row, теперь это только 11 бит) и столбец (column 8 бит), всего получается 20 бит. Но этот процесс занимает 2 шага: сначала row+bank, затем column:

• FPGA выбирает банк, и активирует одну из его строк. Затем FPGA ждет несколько тактов (для того, чтобы строка стала готова к работе).

• Теперь строка активна, и FPGA может осуществить доступ (чтение и/или запись) любых нужных данных, просто предоставив адрес столбца.

• Как только FPGA завершила работу со строкой, она должна закрыть её перед открытием новой.

Для лучшей производительности пользователь (т. е. FPGA) хотел бы избежать слишком частого открытия и закрытия строк, вместо этого максимально часто, насколько это возможно, работая со строками, и чередовать операции в разных банках, чтобы не терять такты на ожидание. Большинство микросхем SDRAM в действительности имеют 4 или 8 банков, и каждый банк не зависим друг от друга, так что может иметь свою собственную активную строку.

Выводы SDRAM. Если мы посмотрим на выводы реальной микросхемы SDRAM, то увидим кое-что новое.

Обновление данных. SDRAM является динамической памятью: её содержимое нуждается в периодическом обновлении, потому что значение каждого бита памяти (0 или 1) содержится в маленьком конденсаторе, у которого заряд со временем снижается из-за токов утечек. Однако скорость разряда конденсатора достаточно низкая, чтобы допускать периодические операции чтения и записи обратно (так называемая операция обновления, refresh). Когда эти операции обновления делаются через определенные периоды времени, производитель гарантирует, что данные не будут потеряны.

Доступны два механизма обновления:

• FPGA использует команду "auto-refresh": обновление осуществляется периодической отправкой в SDRAM этой команды.

• FPGA достаточно часто осуществляет доступ к каждой строке: открытие строки приводит в действие специальную схему усилителей (sense amplifiers) в SDRAM, чтобы получить копию всех зарядов конденсаторов строки. Тогда когда строка закрывается, значения, прочитанные ранее, копируются обратно в конденсаторы, обновляя данные во время этого процесса.

Почему нужен контроллер памяти? Микросхемы динамической памяти более сложные для доступа, чем статические. У нас есть строки, столбцы, банки, и циклы обновления, и обо всем этом нужно заботиться. Но SDRAM востребованы благодаря их достаточно высокой скорости и низкой стоимости в пересчете на бит.

Таким образом, нам нужен способ доступа к SDRAM, достаточно простой, как доступ к статической памяти. Это именно та причина, по которой делают контроллеры памяти. Они функционируют как слой трансляции: с одной стороны они предоставляют простой для пользователя интерфейс к памяти, и с другой стороны делают всю грязную работу по управлению сигналами микросхемы SDRAM, в том числе функции обновления.

[Простой контроллер SDRAM]

У нашего контроллера SDRAM будут следующие свойства:

• Простой в использовании: SDRAM будет выглядеть как статическая память (или все равно максимально близко к этому, насколько возможно).

• Быстрый: SDRAM используется в пакетном режиме (burst mode), если Вы предоставите следующие друг за другом адреса.

• Простой: без планировщика, в любой момент времени активен только один банк.

• Мощный: SDRAM появляется как простая двухпортовая память (т. е. с одним агентом записи и одним агентом чтения).

Последнее свойство свойство контроллера самое необычное. SDRAM это память с одним портом, но FPGA значительно выигрывают от доступа к двухпортовой памяти (наподобие BRAM), так что это полезное свойство мы оставим.

Сигналы контроллера. Вот упрощенный вид на наш контроллер SDRAM.

Первые 3 сигнала слева используются для агента записи (запрос записи "write request", за которым идет адрес записи "write address" и записываемые данные "write data"). Ниже идут 3 сигнала для агента чтения. Справа сигналы, которыми контролер управляет SDRAM. Для рассмотрения в перспективе ниже показана типовая система FPGA с использованием нашего контроллера SDRAM.

Контроллер представляет SDRAM для использования как двухпортовую память. Но SDRAM в реальности память однопортовая, поэтому нашему контроллеру нужен какой-то трюк для обработки двух запросов. Если 2 запроса поступили одновременно, то либо один из агентов приостанавливается, или их запросы записываются и выполняются позже. Наш контроллер выбирает первую стратегию. Для этого добавлены сигналы предоставления доступа "grant": агент может выставить запрос в любое время, но контроллер решает, предоставлять доступ или нет. Если запрос запрещен, нужно его удерживать, и доступ будет предоставлен по возможности.

Еще одна сложность с SDRAM происходит от факта, что данные, возвращаемые в ответ на запрос чтения, поступают с задержкой (это называется CAS latency в даташитах на SDRAM). Контроллер также может добавлять несколько тактов задержки. Так что даже когда контроллер может предоставить разрешение на запрос чтения, соответствующие данные становятся доступными только через фиксированное количество тактов. Для удобства добавлен сигнал достоверности данных "data valid", который выставляется тогда, когда данные действительно доступны.

Машина состояний. Сердцем нашего контроллера SDRAM является машина состояний. Контроллер ждет запроса (чтения read или записи write), открывает соответствующий банк/строку (bank/row), выдает команды чтения ли записи (столько, сколько активный агент запрашивает в активной строке), и в конце закрывает строку.

По этой схеме в любой момент времени активен только один банк. Продвинутые контроллеры SDRAM позволяли бы одновременную активность нескольким банкам, но здесь мы решили упростить задачу.

Закрытие и открытие строки занимает некоторое время. Например, даташит на SDRAM дает следующие значения:

tRCD = 20ns (от состояния активности до чтения/записи)

tRP = 21ns (от состояния precharge до активности)

Таким образом, если мы будем работать с SDRAM на частоте 100 МГц, то период тактов окажется 10ns, и нужно добавить несколько пустых тактов (так называемых NOP) в машину состояний. Также нужны циклы восстановления, если агент чтения не гарантирует регулярного открытия каждой строки.

Машина состояний становится немного сложнее.

И наконец, может понадобиться подстроить количество тактов NOP. Например, на частоте 100MHz с временем tRP = 21ns, возможно будет достаточным применить 2 такта NOP после precharge (дает нам 30ns перед следующей активацией).

Инициализация. У SDRAM есть некоторые программируемые настройки (наподобие CAS latency), для этого есть регистр MODE, который нужно инициализировать при включении питания. Для этой цели существует команда LOAD MODE. В контроллер должна быть добавлена инициализация SDRAM, или отдельный шаг перед тем, как контроллер запустится.

Код контроллера показан ниже. Чтобы получить самые лучшие интервалы времени IO, все сигналы управления SDRAM сделаны без какой-либо комбинаторной логики вне FPGA.

Полный демонстрационный код можно скачать по ссылке []. Он функционален, но поскольку он обучающий, то максимально упрощен, и из него удалены не обязательные функции. См. комментарии в коде, описывающие ограничения и требования.

Пример использования. SDRAM часто используется в видеоадаптерах, где память нужна для сохранения графики. Это работает примерно так: процессор компьютера посылает данные графики в видеокарту. Видеокарта использует SDRAM для сохранения данные, и контроллер в карте периодически читает память, чтобы послать данные на дисплей. Поскольку чтение периодическое, в течение этого процесса данные, находящиеся в SDRAM, обновляются автоматически (специальный refresh не требуется).

Подобная базовая система была создана на плате Xylo-EM как часть проверки правильности работы контроллера. Тот факт, что контроллер SDRAM сделан двухпортовым, значительно упростил дизайн (PC/FX2 это агент записи, а видеоконтроллер это агент чтения).

[SDRAM DDR - борьба за скорость]

Когда производители памяти пытались найти способы повысить скорость SDRAM, была представлена память DDR SDRAM. DDR означает "double data rate", т. е. двойная скорость доступа.

Ячейки DDR SDRAM подобны обычной (single data rate) SDRAM (все еще есть банки и строки, которые нужно открывать). Ускорение происходит с повышением частоты тактов, удлинением периодов пакета, и доступ к двум битам за 1 такт (отсюда и пошло имя DDR). Это потребовало очень жесткой организации интервалов времени на сигналах данных, чтобы обеспечить надежное перемещение данных.

Читайте также: