Resolver to digital converter что это

Обновлено: 03.07.2024

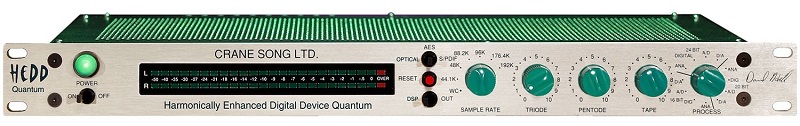

Одним из важнейших компонентов в любой современной студии является аудио конвертер. Использование дешевого преобразователя может привести к тому, что самый дорогой микрофон будет звучать так, словно он был записан через старый модем. С другой стороны высококачественный конвертер способен добавить глубины и детализации вашим записям.

В этой статье мы расскажем обо всем, что важно знать об аудио преобразователях, чтобы помочь вам найти идеальное решение для вашей студии.

Первая в мире цифровая запись была сделана и выпущена в 1971 году. Для этого была использована экспериментальная система записи PCM от японской радиовещательной компании NHK.

И хотя коммерческая цифровая запись была возможна уже в начале 70-х годов, только с выпуском компанией Sony цифрового аудио процессора PCM-501ES в 1984 году, данная технология стала широко доступной.

Студии быстро прочувствовали преимущества работы с цифрой. Однако первые цифровые записывающие устройства были чрезвычайно дорогими, и лишь немногие могли себе это позволить. Были и дешевые девайсы, но они звучали очень грубо и добавляли слишком много шума.

Поскольку технологии непрерывно развиваются, качество звука со временем улучшилось, и цифровые аудиоинтерфейсы стали обычным явлением в профессиональных студиях звукозаписи. В 1999 году песня "Livin' la Vida Loca" Рики Мартина стала первой полностью записанной, отредактированной и сведенной на компьютере. Сегодня большинство профессиональных студий полностью полагаются на цифровые аудиосистемы, причем большую часть рабочей нагрузки выполняют именно цифровые аудио конвертеры.

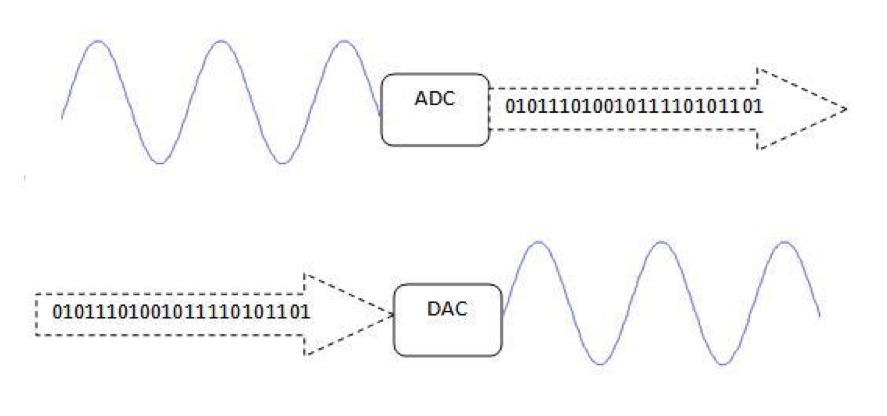

На самом базовом уровне, цифровые аудио преобразователи (ЦАП) преобразуют аудиосигналы из одного типа сигнала в другой.

Аналого-цифровые преобразователи

Аналого-цифровые (АЦ) преобразователи конвертируют аналоговые аудиосигналы, такие как выход с микрофонного предусилителя или внешнего синтезатора, в цифровые, которые могут обрабатываться вашим компьютером.

Цифро-аналоговые преобразователи

Цифро-аналоговые (ЦА) преобразователи работают в обратном порядке, преобразуя цифровые аудиосигналы, например, от вашей DAW или веб-браузера, в аналоговые, которые можно воспроизвести на студийных мониторах или наушниках.

Большинство современных аудиоинтерфейсов уже оборудованы ограниченными ЦАП, что позволяет осуществить простую цифровую запись. Но для высококачественной записи, а особенно для крупных проектов вам понадобится автономный ЦАП. Большинство таких устройств включают в себя как АЦ, так и ЦА преобразователи в одном устройстве, а также они оборудуются некоторыми другими дополнительными функциями.

ЦАПы отвечают за три основные задачи в процессе преобразования. Сначала они семплируют аналоговый аудиосигнал. Это не то же самое, что семплирование песни в хип-хопе. Этот процесс можно сравнить с серийной фотографией на смартфоне.

Во время семплирования аналогового аудиосигнала ЦАП снимают десятки тысяч «цифровых фото» каждую секунду. Чем больше семплов способен ЦАП захватить, тем точнее он может воссоздать исходный аудиосигнал в цифровом мире.

После семплирования аналогового звука ЦАП назначает каждому семплу разную временную метку посредством квантизации. Этот процесс схож с выравниванием транзиентов по сетке в вашей DAW.

Как только завершается процесс квантизации, сигнал преобразуется в двоичный код, который может обрабатывать ваш компьютер. Этот код представляет собой точные значения напряжения сигнала в любой момент времени. «Соединив» каждое значения напряжения каждого семпла, ваши динамики смогут точно воссоздать исходный звук.

Регулируя частоту дискретизации (кГц) и разрядность (Бит) вашего ЦАП, вы можете контролировать качество цифровых аудиозаписей.

Частота дискретизации определяет, как много семплов преобразователь захватывает каждую секунду при семплировании звука. Значения данного параметра стандартизированы:

Минимальная частота дискретизации для аудио с качеством CD составляет 44 100 выборок в секунду. Это число может показаться странным, но оно было выбрано не случайно.

Согласно теореме отсчётов Котельникова (в англоязычной литературе — теорема Найквиста-Шеннона): «частота дискретизации должна быть больше, чем максимальная воспроизводимая частота, умноженная на два». Поскольку диапазон человеческого слуха ограничивается примерно 20 кГц, частота дискретизации должна превышать 40 кГц.

Цифровое аудио разрабатывалось параллельно с цифровым видео. Так, значение 44,1 кГц считалось самой высокой допустимой частотой дискретизации, одновременно совместимой с двумя наиболее распространенными стандартами видео: PAL и NTSC. На сегодняшний день 44,1 кГц — это минимальная стандартная частота для цифрового аудио.

При использовании более высокой частоты дискретизации, ваш ЦАП способен захватывать больше информации и точнее воспроизводить исходный аудиосигнал. Однако это напрямую отражается на нагрузке на ваш процессор, ведет к ограничению количество каналов, с которыми вы можете одновременно работать, и увеличивает размеры аудиофайлов.

Разрядность отвечает за величину динамического диапазона в записи цифрового звука или, другими словами, определяет разницу между самыми громкими и самыми тихими звуками. Большинство профессиональных преобразователей работают со следующими значениями разрядности:

Бит — это двоичная цифра. Бит имеет только два значения: 1 или 0. Включен или выключен. Максимальная громкость или тишина. Но с увеличением количества битов, увеличивается и количество возможных комбинаций. Например, с двумя битами уже получится создать четыре уникальные комбинации: 00, 01, 10 и 11. Каждой из этих комбинаций может быть присвоено различное значение.

В цифровой аудиосистеме каждой комбинации присваивается определенное значение амплитуды звукового сигнала. С увеличением разрядности повышается точность отображения динамики исходного сигнала. Например, в 24-битной системе в вашем распоряжении более 16 миллионов значений, а в 16-битной — около 65000.

Минимальная стандартная разрядность для цифрового аудио с качеством CD составляет 16 бит, но использование больших значений обеспечивает больший динамический диапазон и лучшее соотношение сигнал/шум. Иными словами, большая разрядность позволит делать громкие моменты громче, а тихие — тише, не создавая при этом дополнительных шумов и искажений.

Выбор подходящего ЦАП обычно сводится к трем основным моментам: бюджету, качеству звука и возможностям подключения.

Бюджет

На рынке сегодня есть множество различных вариантов ЦАП на любой вкус и цвет, поэтому найти что-то подходящее в рамках вашего бюджета не составит особого труда. От простых аудиоинтерфейсов с встроенными АЦ/ЦА-конвертерами до модульных систем, таких как Burl Audio B80 Mothership. Важно понимать, что преобразователи — это такой же важный инструмент в вашей студии, как мониторы, поэтому советуем выделить на его приобретение значимую часть бюджета.

Качество звука

Что касается качества звука, профессиональные ЦАПы обычно стремятся к нейтральному, прозрачному звучанию. Однако некоторые преобразователи известны тем, что немного искажают звук, добавляют ему определенный окрас. Некоторые модели обеспечивают кристально чистые верхние частоты, другие ориентированы на передачу максимально глубоких басов. Общий совет при выборе ЦАПа по качеству звука: в большинстве случаев цена соответствует качеству.

Возможности для подключения

Когда дело доходит до подключения, первое, что нужно учитывать, это количество каналов. Мастеринг-конвертеры, такие как Antelope Audio Pure2, предлагают два канала преобразования АЦ/ЦА высокого разрешения. Однако для большинства проектов записи и сведения вам потребуется как минимум восемь выделенных входов и выходов.

Большинство ЦАП включают в себя как аналого-цифровые, так и цифро-аналоговые преобразователи в одном устройстве и могут беспрепятственно транслировать от 8 до 64 каналов одновременно, в зависимости от разрешения. Для особо крупных проектов, которым требуется более 64 каналов, в большинстве моделей предусмотрена возможность объединения нескольких ЦАПов друг с другом.

Некоторые производители выпускают отдельно ЦА- и АЦ-преобразователи. Как правило, АЦ-конвертеры оптимизированы для записи аудио и имеют встроенные предусилители. ЦА-преобразователи, с другой стороны, оптимизированы для целей сведения и мастеринга и оборудуются достаточным количеством выходных разъемов для подключения к внешнему оборудованию.

Профессиональные ЦАПы обычно предлагают сразу несколько вариантов для подключения к компьютеру. Для тех, кому нужна большая гибкость для взаимодействия с несколькими устройствами одновременно, многие ЦАПы оборудованы выходами Ethernet и AES. Если же вы просто ищете высококачественный преобразователь для использования с ноутбуком или компьютером, большинство моделей поставляются с соединениями USB, Thunderbolt или FireWire.

Основная цель — качественный звук. Хороший ЦАП лишь один из элементов, который помогает в достижении этой цели. По сути, любая модель способна улучшить звук вашей существующей аудиосистемы. Все, что вам нужно сделать, это выбрать подходящий ЦАП, подключить его и наслаждаться!

Low Cost, Complete 12-Bit Resolver-to-Digital Converter

Обзор

Особенности и преимущества

- Complete Monolithic Resolver-to-Digital Converter

- Incremental Encoder Emulation (1024-Line)

- Absolute Serial Data (12-Bit)

- Differential Inputs

- 12-Bit Resolution

- Industrial Temperature Range

- 20-Lead PLCC

- Low Power (50 mW)

Подробнее о продукте

The AD2S90 is a complete 12-bit resolution tracking resolver-to- digital converter. No external components are required to operate the device.

The converter accepts 2 V rms ± 10% input signals in the range 3 kHz-20 kHz on the SIN, COS and REF inputs. A Type II servo loop is employed to track the inputs and convert the input SIN and COS information into a digital representation of the input angle. The bandwidth of the converter is set internally at 1 kHz. The maximum tracking rate is 375 rps at 12-bit resolution.

Angular position output information is available in two forms, absolute serial binary and incremental A quad B.

The absolute serial binary output is 12-bit (1 in 4096). The data output pin is high impedance when Chip Select CS is logic HI. This allows the connection of multiple converters onto a common bus. Absolute angular information in serial pure binary form is accessed by CS followed by the application of an external clock (SCLK) with a maximum rate of 2 MHz.

The encoder emulation outputs A, B and NM continuously produce signals equivalent to a 1024 line encoder.

When decoded this corresponds to 12-bits resolution. Three common north marker pulse widths are selected via a single pin (NMC).

An analog velocity output signal provides a representation of velocity from a rotating resolver shaft traveling in either a clockwise or counterclockwise direction.

The AD2S90 operates on a ±5 V dc ± 5% power supplies and is fabricated on Analog Devices' Linear Compatible CMOS process (LC 2 MOS). LC 2 MOS is a mixed technology process that combines precision bipolar circuits with low power CMOS logic circuits.

Продукты

Области применения и технологии

Совместимые продукты Показать все в параметрическом поиске

Статус продукта Производство

По меньшей мере, одна модель из данной серии продукции находится в производстве и доступна для приобретения. Продукт подходит для применения в новых разработках, но возможно наличие новейших альтернатив.

ПОМОЩЬ ПО ТЕХНИЧЕСКИМ ОПИСАНИЯМ

Технические описания оптимизированы для просмотра с помощью Adobe Acrobat Reader 6.0.

Переводы этого технического описания с английского на другие языки предоставляются для удобства пользователей, однако новейшими можно считать только последние версии на английском языке.

ADXL345

Техническая документация

Техническое описание (1)

Статьи по применению (4)

ПО и системные требования

Драйверы устройств

AD2S90 IIO Resolver-to-Digital Converter Linux Driver

Материалы по теме

Руководства по подбору сопутствующих компонентов (1)

Технические статьи (3)

Ресурсы проектирования

Компания Analog Devices всегда уделяла повышенное внимание обеспечению максимальных уровней качества и надежности предлагаемых продуктов. Для этого мы внедряем контроль качества и надежности на каждом этапе проектирования технологических процессов и продуктов, а также на этапе производства. Нашим принципом является обеспечение "полного отсутствия дефектов" поставляемых компонентов.

Информация о PCN-PDN

Поддержка и обсуждения

AD2S90 Обсуждения

Образцы и покупка

Функционирование раздела Образцы и покупка возможно только в полной версии сайтаПриведенные цены действительны в США и указаны только для примерного бюджетного рассчета. Цены указаны в долларах США (за штуку в указанном размере партии) и могут быть изменены. Цены в других регионах могут отличаться в зависимости от местных пошлин, налогов, сборов и курсов валют. Для уточнения стоимости обращайтесь в местные офисы продаж Analog Devices, или к официальным дистрибьюторам. Цены на оценочные платы и наборы указаны за штуку независимо от количества.

The model number is a specific version of a generic that can be purchased or sampled.

Status indicates the current lifecycle of the product. This can be one of 4 stages:

- Pre-Release: The model has not been released to general production, but samples may be available.

- Production: The model is currently being produced, and generally available for purchase and sampling.

- Last Time Buy: The model has been scheduled for obsolescence, but may still be purchased for a limited time.

- Obsolete: The specific part is obsolete and no longer available. Other models listed in the table may still be available (if they have a status that is not obsolete).

The package for this IC (i.e. DIP, SOIC, BGA). An Evaluation Board is a board engineered to show the performance of the model, the part is included on the board.

For detailed drawings and chemical composition please consult our Package Site.

Pin Count is the number of pins, balls, or pads on the device. Pin-out diagrams & pin function descriptions may be found in the datasheet.

This is the acceptable operating range of the device. The various ranges specified are as follows:

Indicates the packing option of the model (Tube, Reel, Tray, etc.) and the standard quantity in that packing option.

The USA list pricing shown is for BUDGETARY USE ONLY, shown in United States dollars (FOB USA per unit for the stated volume), and is subject to change. International prices may differ due to local duties, taxes, fees and exchange rates. For volume-specific price or delivery quotes, please contact your local Analog Devices, Inc. sales office or authorized distributor. Pricing displayed for Evaluation Boards and Kits is based on 1-piece pricing.

This is the date Analog Devices, Inc. anticipates that the product will ship from the warehouse. Most orders ship within 48 hours of this date.Once an order has been placed, Analog Devices, Inc. will send an Order Acknowledgement email to confirm your delivery date. It is important to note the scheduled dock date on the order entry screen. We do take orders for items that are not in stock, so delivery may be scheduled at a future date. Also, please note the warehouse location for the product ordered. We have warehouses in the United States, Europe and Southeast Asia. Transit times from these sites may vary.

Sample availability may be better than production availability. Please enter samples into your cart to check sample availability.

Due to environmental concerns, ADI offers many of our products in lead-free versions. For more information about lead-free parts, please consult our Pb (Lead) free information page.

This is the list of Product Change Notifications (PCN) and Product Discontinuance Notifications (PDN) published on the web for this model. Click on the link to access PCN/PDN information. Online PCNs are available starting in 2009 and online PDNs are available starting in 2010. To obtain older PCNs or PDNs, contact your ADI Sales Rep. For more information on ADI's PCN/PDN process, please visit our PCN/PDN Information page.

The Purchase button will be displayed if model is available for purchase online at Analog Devices or one of our authorized distributors. Select the purchase button to display inventory availability and online purchase options.The Sample button will be displayed if a model is available for web samples. If a model is not available for web samples, look for notes on the product page that indicate how to request samples or Contact ADI.

Analog Devices использует файлы cookie для повышения качества работы сайта

Некоторые файлы cookie необходимы для безопасного входа в систему, в то время как другие являются дополнительными и нужны лишь для функциональных действий. Мы собираем данные для улучшения наших продуктов и услуг. Мы рекомендуем вам принять наши файлы cookie, чтобы обеспечить максимальную функциональность, которую может предоставить наш сайт. Для получения дополнительной информации вы можете просмотреть подробные сведения о файлах cookie. Узнайте больше о политике конфиденциальности.

На рисунке — первый в мире спутник квантовой связи «Мо-Цзы», который запустили из Китая в 2016 году, в нем летает TDC, реализованная в FPGA.

Объяснить своей девушке (или парню), что такое ADC и DAC, и в каких домашних приборах они используются, может каждый человек, называющий себя инженером. А вот что такое TDC, и почему у нас дома их нет, зачастую можно узнать только после свадьбы.

TDC — это time-to-digital converter. По-русски говоря: времяизмерительная система.

Основные потребители быстродействующих TDC — научные группы. Как правило, под определенный исследовательский проект требуется что-то очень специфическое. То каналов надо много, то разрешение очень высокое, то исполнение компактное. А уровень развития современных FPGA и их доступность как раз дают исследователям возможность экспериментировать с реализациями и подстраивать их под собственные нужды.

В этой хабрастатье приводится детальное описание простенькой времяизмерительной системы на FPGA Cyclone IV. Статья будет полезна не только для расширения кругозора, но и с методической точки зрения, поскольку реализация системы нетривиальная.

Сразу отметим, что пришедшая на ум мысль «Да о чем они тут пишут? Считываем по событию счетчик/таймер CPU/MCU и дело в шляпе» тут не годится. Дело в том, что в приложениях требуется точность на порядок большая, чем могут обеспечить «стандартные» счетчики, а также детерминированная латентность, многоканальность и большая «пропускная способность событий».

Формально задача, которую решает TDC, — определение временного интервала между событиями. В многоканальных системах логика верхнего уровня дополнительно может вычислять корреляции между событиями. В качестве события, как правило, выступает срабатывание какого-либо детектора частиц или оптического датчика. В быту, конечно, такие системы не находят применения. И вообще, в масштабе пикосекунд имеет смысл измерять физические процессы, протекающие в сравнимых временах, например, пролет элементарных частиц в детекторе. Отметим некоторые направления применения TDC:

- Масспектроскопия, позитронно-эмиссионная томография (ПЭТ) — регистрируются времена прихода частиц на детекторы.

- ЛИДАРы — по временным отсчетам определяется расстояние до облученной области.

- Квантовая криптография — регистрируются времена срабатывания детекторов одиночных фотонов.

- Генерация случайных чисел — времена наступления событий используются в качестве энтропии.

Реализация TDC в FPGA

С электронной точки зрения реализация задача сводится к «регистрированию положения» фронта сигнала относительно какого-либо синхросигнала. Элементы FPGA, имеющиеся в нашем распоряжении, это физически линии сигналов на кристалле, регистры, логические блоки, линии клока и PLL. Основные подходы к реализации TDC с использованием этих элементов были предложены относительно давно: субтактовая линия задержки (tapped delay line), линия задержки Вернье (Vernier delay line), «фазированные PLL». Но инженеры до сих пор работают над их усовершенствованием и имплементацией на современных платформах.

В нашей FPGA-шной реализации мы в основном следовали этой публикации, описывающей субтактовую линию задержки, а также некоторым общим идеям, почерпнутым в публикациях Jinyuan Wu из CERN`а 2000-x годов.

Вспоминаем устройство FPGA семейства Cyclone от компании Intel (Altera). Логические элементы (LE) сгруппированы в блоки (LAB), управляемые одной линией клока и соединены линиями переноса разряда (carry line). Это как раз нужная нам схема. То есть входной сигнал будем заводить на какой-нибудь LE и направлять его по линиям переноса разряда на соседние. При этом LE должны работать в арифметическом режиме. Тактировать все LE будем одним клоком и забирать термокод по появлению входного сигнала.

Теперь перед нами стоят несколько практических вопросов:

- Как описать схему линии задержки на Verilog?

- Как объяснить Quartus`у, что мы хотим использовать именно линии переноса и отключить их оптимизацию?

- Как сформировать линию задержки на соседних LE из одного LAB?

С точки зрения Quartus`а, линия задержки — штука бессмысленная. Зачем вести сигнал хитрым способом, если его сразу можно провести из точки A в точку B? Для того чтобы Quartus не пытался оптимизировать линию задержки, и результате выкинул составляющие ее LE, используем директиву /* synthesis keep = 1 */ напротив объявления элемента, к которому она относится. В результате основной код выглядит следующим образом:

Для указания на использование соседних LE и их размещения в конкретном месте на кристалле применим инструмент LogicLock Regions. То есть укажем на кристалле прямоугольную область и явно укажем набор LE, которые Quartus должен в ней разместить. На рисунке ниже область line содержит линию задержки, а область delay_line включает дополнительную логику обработки термокода.

Ниже приведем схему размещения элементов линии задержки из Chip Planner со схематическим отображением сигналов и детальную схему первых двух элементов линии задержки.

Отметим, что реализованная схема имеет мертвое время в один такт, необходимое для «сброса» регистров линии задержки.

Описанная схема была разложена на чипе Cyclone IV EP4CE22. Эксперименты с длиной линии задержки и частотой клока привели к следующим параметрам: длина линии задержки 64 LE, частота клока

120МГц. Линия задержки и логика обработки термокода умещаются в 42 LABs.

Калибровка TDC

Очевидно, что физические задержки на каждом логическом элементе отличаются. Для учета этого факта необходимо провести калибровку устройства. Первым, что приходит в голову, видится подача на вход TDC сигнала с известным периодом. Однако такой путь является достаточно трудоемким, поскольку требуется прецизионное сканирование периода сигнала в относительно широком диапазоне.

Следующим предложением является калибровка методом случайных событий: подаем на вход сигналы с равномерно распределенными случайными задержками и наблюдаем гистограмму попадания событий в тайм-бины. В этом случае точность растет по мере накопления событий как , где N — число поданных событий. Мы же воспользуемся методом коррелированных событий. В этом методе точность ограничена изначально и может быть достигнута сравнительно небольшим числом измерений.

Суть способа в подборе частоты генерации событий, при которой они будут равномерно распределены в тайм-бинах. Для этого необходимо удовлетворить соотношению:

где N — число событий, которые мы хотим равномерно распределить в временном интервале T1, 1/T2 — частота генерации событий, — дробная часть числа.

При этом сигналы могут быть сформированы внутренним PLL. В нашем примере входная частота PLL равна 50МГц и для числа событий N = 256 мы выбрали следующие рабочие частоты:

- 1/T1 = 50МГц * 93/40 = 116.26МГц: частота клока TDC

- 1/T2 = 50МГц * 32/285 = 5.614МГц: частота генерации событий

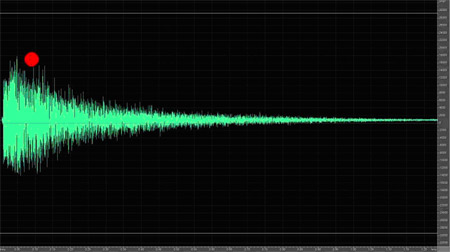

Процедура калибровки заключается в многократном измерении непрерывной последовательности из 256 событий. В нашем эксперименте общее число измеренных событий равно 8192. Полученная в результате гистограмма соответствует доле отдельных элементов задержки в одном такте TDC.

На верхнем графике приведено распределение отсчетов по элементам линии задержки. Номер отсчета следует понимать как границу между единицами и нулями в скорректированном термокоде. Провал на 45-м элементе линии задержки соотвует одновременному срабатыванию двух соседних элементов, что является характерным для подобной реализации (bubble error [Wu08]). Положение провала зависит от области размещения линии задержки на кристалле. При увеличении числа регистрируемых событий не происходит существенного изменения распределения отсчетов.

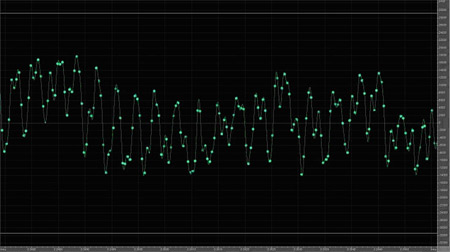

На нижнем графике приведена калибровочная кривая, сопоставляющая номер интервала с длительностью задержки. Сумма всех отсчетов по тайм-бинам соответствует времени T1 = 8.6нс. Перевод номера бина во временные интервалы может осуществляться непосредственно в кристалле или с помощью программируемого процессора Nios II.

Далее приведены абсолютные временные интервалы соотвующие элементам линии задержки с существенным числом срабатываний и распределение интервалов. Среднее значение интервала равно 160 ps, дисперсия времен — 31 ps. В результате, можно утверждать, что достигнутое разрешение времяизмерительной системы составляет

200 ps. Чтобы почувствовать это число отметим, что оно соответствует частоте 5ГГц. И это только самая простая реализация в FPGA не на самом последнем кристалле!

Читайте также: