Сигнал clk на шине pci

Обновлено: 04.07.2024

Описание работы шины PCI.

Введение

PCI (Peripheral Component Interconnect bus) - шина для подсоединения периферийных устройств. Стала массово применяться для Pentium-систем, но используется и с 486 процессорами. Частота шины от 20 до 33 МГц, теоретически максимальная скорость 132/264 Мбайт/с для 32/64 бит. В современных материнских платах частота на шине PCI задается как 1/2 входной частоты процессора, т.е при частоте 66 MHz на PCI будет 33 MHz, при 75 MHz - 37.5 MHz.

Имеет версии с питанием 5V, 3.3V и универсальную (с переключением линий +VI/O c 5V на 3,3V). Ключами являются пропущенные ряды контактов 12, 13 и 50, 51. Для слота с питанием 5V ключ расположен на месте контактов 50, 51, для 3,3 В - 12, 13, а для универсального - два ключа: 12, 13 и 50,51. 32-битный слот заканчивается контактами А62/В62, 64-битный - А94/В94.

Слот PCI самодостаточен для подключения любого контроллера (VLB не работала без ISA), на системной плате может сосуществовать с любой из других шин ввода-вывода.

Шина PCI - первая шина в архитектуре IBM PC, которая не привязана к этой архитектуре. Она является процессорно-независимой и применяется, например, в компьютерах Macintosh.

В отличие от остальных шин, компоненты расположены на левой поверхности плат PCI-адаптеров. По этой причине крайний PCI-слот обычно разделяет использование посадочного места с соседним ISA-слотом (Shared slot).

Процессор через так называемые мосты (PCI Bridge) может быть подключен к нескольким каналам PCI, обеспечивая возможность одновременной передачи данных между независимыми каналами PCI (возможно только в спецификации 2.1).

Автоконфигурирование устройств (выбор запросов прерывания, каналов DMA) поддерживается средствами BIOS материнской платы по образу и подобию стандарта Plug & Play. В настоящее время действует спецификация PCI 2.1.

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 восьмибитных регистров, не приписанных ни к пространству памяти, ни к пространству ввода-вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода-вывода.

На PCI определены два основных вида устройств - инициатор (по ГОСТ - задатчик), т.е. устройство, получившее от арбитра шины разрешение на захват ее и устройство назначения, цель (target) с которым инициатор выполняет цикл обмена данными.

Сигналы шины PCI

Знак - (минус) перед названием сигнала означает, что активный уровень этого сигнала логический ноль, обозначение означает группу сигналов с номерами от 0 до XX.

AD - мультиплексированная шина адреса/данных. Адрес передается по сигналу - FRAME, в последующих тактах передаются данные.

-C/ BE - команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины (чтение-запись памяти, ввода/вывода или чтение/запись конфигурации, подтверждение прерывания и другие) задается четырехбитным кодом в фазе адреса по сигналу - FRAME.

-FRAME - индикатор фазы адреса (иначе - передача данных).

-DEVSEL - выбор инициатором устройства назначения.

-IRDY - готовность инициатора к обмену данными.

-TRDY - готовность устройства назначения к обмену данными.

-STOP - запрос устройства назначения к инициатору на останов текущей транзакции.

-LOCK - используется для установки, обслуживания и освобождения захвата ресурса на PCI.

-REQ - запрос от PCI-устройства на захват шины (для слотов 3:0).

-GNT - разрешение мастеру на использование шины.

PAR - общий бит четности для линий AD и C/BE.

-ParityER - сигнал об ошибке по четности (от устройства, ее обнаружившего).

-RST - сброс всех устройств.

IDSEL - выбор устройства назначения в циклах считывания и записи конфигурации.

-SERR - системная ошибка, активизируется любым устройством PCI и вызывает немаскируемое прерывание процессора (NMI).

-REQ64 - запрос на 64-битный обмен.

-ASK64 - подтверждение 64-битного обмена.

-INTR A,B,C,D - линии запросов прерывания, направляются на доступные линии IRQ BIOS компьютера. Запрос по низкому уровню допускает разделяемое использование линий прерывания.

Clock - сигнал синхронизации на тактовой частоте шины.

Test Clock, -TSTRES, TestDO, TestDI - сигналы для тестирования адаптеров по интерфейсу JTAG (на системной плате обычно не задействованы).

Вы здесь: Главная PCI и PCI-X Протокол, команды и транзакции шин PCI и PCI-X Сигнальный протокол шин PCI и PCI-XАрхитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Сигнальный протокол шин PCI и PCI-X

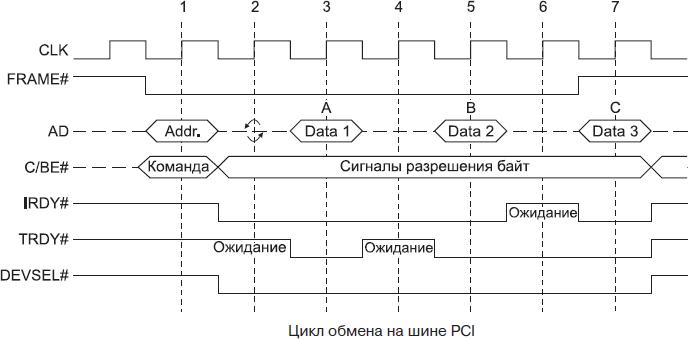

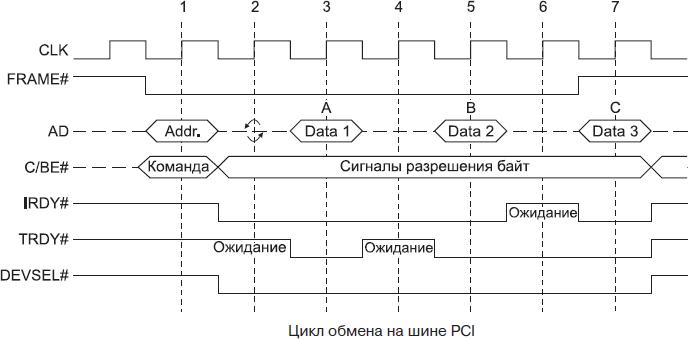

Обмен информацией по шине PCI и PCI-X организован в виде транзакций — логически завершенных операций обмена. В типовой транзакции участвуют два устройства —инициатор обмена (initiator), он же ведущее устройство (master), и целевое устройство (ЦУ, target)), оно же ведомое (slave). Правила взаимодействия этих устройств определяются протоколом шины PCI. Устройство может следить за транзакциями на шине и не являясь их участником (не вводя никаких сигналов); режиму слежения соответствует термин Snooping. Есть особый тип транзакции (Special Cycle) — широковещательный, в котором инициатор протокольно не взаимодействует ни с одним из устройств. В каждой транзакции выполняется одна команда — как правило, чтение или запись данных по указанному адресу. Транзакция начинается с фазы адреса, в которой инициатор задает команду и целевой адрес. Далее могут следовать фазы данных, в которых одно устройство (источник данных) помещает данные на шину, а другое (приемник) их считывает. Транзакции, в которых присутствует множество фаз данных, называются пакетными. Есть и одиночные транзакции (с одной фазой данных). Транзакция может завершиться и без фаз данных, если целевое устройство (или инициатор) не готово к обмену. В шине PCI-X добавлена фаза атрибутов, в которой передается дополнительная информация о транзакции.

Состав и назначение интерфейсных сигналов шины раскрывает таблице ниже. Состояния всех сигнальных линий воспринимаются по положительному перепаду CLK, и именно эти моменты в дальнейшем описании подразумеваются под тактами шины (на рисунках отмечены вертикальными пунктирными линиями). В разные моменты времени одними и теми же сигнальными линиями управляют разные устройства шины, и для корректной (бесконфликтной) «передачи полномочий» требуется, чтобы существовал промежуток времени, в течение которого линией не управляет ни одно устройство. На временных диаграммах это событие — так называемый «пируэт» (turnaround) — обозначается парой полукруглых стрелок.

Таблица. сигналы шины PCI

Возможности PCI-X: на платах PCI — заземлен, на PCI-X133 соединен с землей через конденсатор 0,01 мкФ, на PCI-X66 — параллельной RC-цепочкой 10 кОм, 0,01 мкФ.

Ведущее устройство может завершить транзакцию одним из следующих способов:

Использование трех типов прекращения транзакции вовсе не обязательно для всех целевых устройств, однако любое ведущее устройство должно быть готово к завершению транзакций по любой из этих причин.

PCI Express, или PCIe, или PCI-E (также известная как 3GIO for 3rd Generation I/O; не путать с PCI-X и протокол , основанный на последовательной передаче данных .

Разработка стандарта PCI Express была начата фирмой Intel после отказа от шины 2002 года . Развитием стандарта PCI Express занимается организация

Содержание

Описание [ ]

В отличие от стандарта PCI, использовавшего для передачи данных общую шину с подключением параллельно нескольких устройств, PCI Express, в общем случае, является топологией типа звезда .

Устройства PCI Express взаимодействуют между собой через среду, образованную коммутаторами, при этом каждое устройство напрямую связано соединением типа PCI-X . Де-факто PCI Express заменила эти шины в персональных компьютерах.

Разъёмы [ ]

Mini PCI-E [ ]

Для этого стандарта разъёма выпускается много периферийных устройств:

MiniPCI и MiniPCI Express

SSD Mini PCI Express [ ]

- PATA

- SATA

- USB

- Питание 3.3 В

Контакты SSD Mini PCI Express Шаблон:Нет АИ

| 33 | Sata TX+ | 34 | GND |

| 31 | Sata TX- | 32 | IDE_DMARQ |

| 29 | GND | 30 | IDE_DMACK |

| 27 | GND | 28 | IDE_IOREAD |

| 25 | Sata RX+ | 26 | GND |

| 23 | Sata RX- | 24 | IDE_IOWR |

| 21 | GND | 22 | IDE_RESET |

| 19 | IDE_D7 | 20 | IDE_D8 |

| 17 | IDE_D6 | 18 | GND |

| Перегородка | Перегородка | ||

| 15 | GND | 16 | IDE_D9 |

| 13 | IDE_D5 | 14 | IDE_D10 |

| 11 | IDE_D4 | 12 | IDE_D11 |

| 9 | GND | 10 | IDE_D12 |

| 7 | IDE_D3 | 8 | IDE_D13 |

| 5 | IDE_D2 | 6 | IDE_D14 |

| 3 | IDE_D1 | 4 | GND |

| 1 | IDE_D0 | 2 | IDE_D15 |

ExpressCard [ ]

Описание протокола [ ]

Видеокарта для PCI Express x16

На электрическом уровне каждое соединение использует низковольтную дифференциальную передачу сигнала ( SONET / Пропускная способность [ ]

Шина Конкурирующие протоколы [ ]

Кроме PCI Express, существует ещё ряд высокоскоростных стандартизованных последовательных интерфейсов, вот только некоторые из них: HyperTransport , PCI Express 2.0 [ ]

Группа 2007 года . Основные нововведения в PCI Express 2.0:

- Увеличенная пропускная способность: ПСП одной линии 500 МБ/с, или 5 ГТ/с ( Гигатранзакций/с ).

- Внесены усовершенствования в протокол передачи между устройствами и программную модель.

- Динамическое управление скоростью (для управления скоростью работы связи).

- Оповещение о пропускной способности (для оповещения ПО об изменениях скорости и ширины шины).

- Шаблон:Lang-en ) внутри устройства ( Шаблон:Lang-en ).

- Переопределение предела по мощности (для переопределения лимита мощности слота при присоединении устройств, потребляющих бо́льшую мощность).

PCI Express 2.0 полностью 7 февраля 2007 года PCI-SIG выпустила спецификацию внешней кабельной системы PCIE. Новая спецификация позволяет использовать кабели длиной до 10 метров, работающие с пропускной способностью 2,5 ГТ/с.

PCI Express 2.1 [ ]

По физическим характеристикам (скорость, разъём) соответствует 2.0, в программной части добавлены функции, которые в полной мере планируют внедрить в версии 3.0. Так как большинство системных плат продаются с версией 2.0, наличие только видеокарты с 2.1 не даёт задействовать режим 2.1.

PCI Express 3.0 [ ]

PCI Express 4.0 [ ]

Обмен информацией по шине PCI и PCI-X организован в виде транзакций — логически завершенных операций обмена. В типовой транзакции участвуют два устройства —инициатор обмена (initiator), он же ведущее устройство (master), и целевое устройство (ЦУ, target)), оно же ведомое (slave). Правила взаимодействия этих устройств определяются протоколом шины PCI. Устройство может следить за транзакциями на шине и не являясь их участником (не вводя никаких сигналов); режиму слежения соответствует термин Snooping. Есть особый тип транзакции (Special Cycle) — широковещательный, в котором инициатор протокольно не взаимодействует ни с одним из устройств. В каждой транзакции выполняется одна команда — как правило, чтение или запись данных по указанному адресу. Транзакция начинается с фазы адреса, в которой инициатор задает команду и целевой адрес. Далее могут следовать фазы данных, в которых одно устройство (источник данных) помещает данные на шину, а другое (приемник) их считывает. Транзакции, в которых присутствует множество фаз данных, называются пакетными. Есть и одиночные транзакции (с одной фазой данных). Транзакция может завершиться и без фаз данных, если целевое устройство (или инициатор) не готово к обмену. В шине PCI-X добавлена фаза атрибутов, в которой передается дополнительная информация о транзакции.

Состав и назначение интерфейсных сигналов шины раскрывает таблице ниже. Состояния всех сигнальных линий воспринимаются по положительному перепаду CLK, и именно эти моменты в дальнейшем описании подразумеваются под тактами шины (на рисунках отмечены вертикальными пунктирными линиями). В разные моменты времени одними и теми же сигнальными линиями управляют разные устройства шины, и для корректной (бесконфликтной) «передачи полномочий» требуется, чтобы существовал промежуток времени, в течение которого линией не управляет ни одно устройство. На временных диаграммах это событие — так называемый «пируэт» (turnaround) — обозначается парой полукруглых стрелок.

Таблица. сигналы шины PCI

Возможности PCI-X: на платах PCI — заземлен, на PCI-X133 соединен с землей через конденсатор 0,01 мкФ, на PCI-X66 — параллельной RC-цепочкой 10 кОм, 0,01 мкФ.

Ведущее устройство может завершить транзакцию одним из следующих способов:

Использование трех типов прекращения транзакции вовсе не обязательно для всех целевых устройств, однако любое ведущее устройство должно быть готово к завершению транзакций по любой из этих причин.

Команды шины PCI

Команды PCI определяют направление и тип транзакций, а также адресное пространство, к которому они относятся. Набор команд шины PCI включает следующие:

| Код C/BE[3:0] | PCI команда | PCI-X команда | Длина | Возможность расщепления |

| 0000 | Interrupt Acknowledge | Interrupt Acknowledge, подтверждение прерывания | DWORD | + |

| 0001 | Special Cycle | Special Cycle, специальный широковещательный цикл | DWORD | - |

| 0010 | I/O Read | I/O Read, чтение ввода/вывода | DWORD | + |

| 0011 | I/O Write | I/O Read, запись ввода/вывода | DWORD | + |

| 0100 | Резерв | Резерв | - | - |

| 0101 | Резерв | Device ID Message (DIM), посылка собщения устройству (PCI-X 2.0) | Пакет | - |

| 0110 | Memory Read | Memory Read DWORD, одиночное чтение памяти | DWORD | + |

| 0111 | Memory Write | Memory Write, запись памяти | Пакет | - |

| 1000 | Резерв | Alias to Memory Read Block псевдоним чтения блока памяти | Пакет | + |

| 1001 | Резерв | Alias to Memory Write Block, псевдоним записи блока памяти | Пакет | - |

| 1010 | Configuration Read | Configuration Read, конфигурационное чтение | DWORD | + |

| 1011 | Configuration Write | Configuration Write, конфигурационная запись | DWORD | + |

| 1100 | Memory Read Multiple | Split Completion, завершение расщепленной транзакции | Пакет | - |

| 1101 | Dual Address Cycle | Dual Address Cycle (DAC), цикл передачи расширенного адреса памяти | - | - |

| 1110 | Memory Read Line | Memory Read Block, чтение блока памяти | Пакет | + |

| 1111 | Memory Write and Invalidate | Memory Write Block, запись блока памяти | Пакет | - |

Таблица. Декодирование команд шин PCI и PCI-X

В каждой команде шины указывается адрес, относящийся к первой фазе данных пакета. Для каждой последующей фазы данных пакета адрес увеличивается на 4 (следующее двойное слово) или 8 (для 64-битных передач), но в командах обращения к памяти предусматривался и иной порядок.

Для каждого из трех пространств — памяти, портов ввода/вывода и конфигурационных регистров — адресация различна; в специальных циклах адрес игнорируется.

Адресация памяти

На шине PCI передается физический адрес памяти; в процессорах x86 (и других) он получается из логического посредством постраничной табличной трансляции блоком MMU.

В командах обращения к памяти на шине PCI адрес, выровненный по границе двойного слова, передается по линиям AD[31:2]; линии AD[1:0] задают порядок адресов в пакете:

- 00 — линейное инкрементирование; адрес последующей фазы отличается от предыдущего на число байтов шины (4 для 32-битной и 8 для 64-битной шины);

- 10 — сворачивание адресов с учетом длины строки кэш-памяти (Cacheline Wrap mode). В транзакции адрес для очередной фазы увеличивается до достижения границы строки кэша, после чего переходит на начало этой строки и увеличивается до адреса, предшествующего начальному. Если транзакция длиннее строки кэша, то она продолжится в следующей строке с того же смещения, что и началась. Так, при длине строки 16 байт и 32-битной шине транзакция, начавшаяся с адреса xxxxxx08h, будет иметь последующие фазы данных, относящиеся к адресам xxxxxx0Ch, xxxxxx00h, xxxxxx04h; и далее к xxxxxx18h, xxxxxx1Ch, xxxxxx10h, xxxxxx14h. Длина строки кэша прописывается в конфигурационном пространстве устройства. Если устройство не имеет регистра Cache Line Size, то оно должно прекратить транзакцию после первой фазы данных, поскольку порядок чередования адресов оказывается неопределенным;

- 01 и 11 — зарезервированы, могут использоваться как указание на отключение (Disconnect) после первой фазы данных.

Если требуется доступ к адресам свыше 4 Гбайт, то используется двухадресный цикл, передающий младшие 32 бита полного 64-битного адреса для последующей команды, вместе с которой передаются старшие биты адреса. В обычных командах подразумевается нулевое значение бит [63:32] полного адреса.

Адресация ввода/вывода

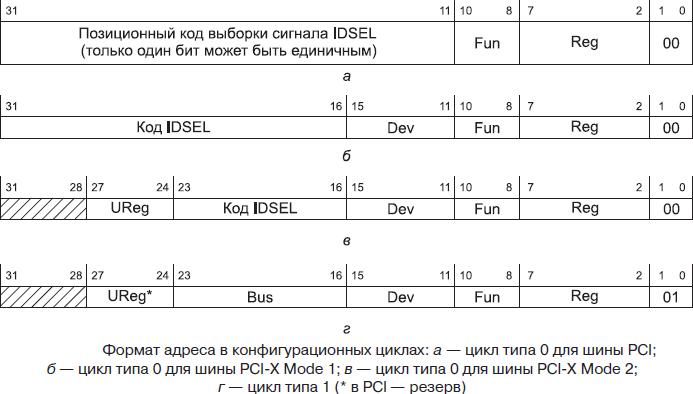

Адресация конфигурационных регистров и специальный цикл

В командах конфигурационной записи/считывания применяется специфическая трактовка адреса, здесь формат адреса может быть одним из двух типов. Для доступа к регистрам устройства, расположенного на данной шине, используются конфигурационные транзакции типа 0. При этом устройство (карта расширения) выбирается индивидуальным сигналом IDSEL, который формируется мостом этой шины из номера устройства. Выбранное устройство на шине в битах AD[10:8] «видит» номер функции Fun, а в битах AD[7:2] — номер конфигурационного регистра Reg, при этом AD[1:0] = 00 является признаком типа 0. Линии AD[31:11] используются в качестве источника сигналов IDSEL для устройств данной шины. В спецификации на саму шину по линии AD11 передается IDSEL для устройства 0, по AD12 — для устройства 1, … по AD31 — для устройства 20. В спецификации на мосты приводится таблица, в которой используются только линии c AD16 (устройство 0) по AD31 (устройство 15). Устройства PCI, скомбинированные с мостом (расположенные с ним в одной микросхеме), могут использовать и большие номера, для которых линий AD уже не хватает. В PCI-X по линиям AD[15:11] передается недекодированный номер устройства Dev — он нужен устройству для передачи в качестве части своего идентификатора в атрибутах транзакции. Для устройств, работающих в Mode 1, для IDSEL используются линии AD[31:16], а для Mode 2 — только AD[23:16], так что максимальный номер устройства — 7. Это позволяет расширить конфигурационное пространство функции до 4 Кбайт: в качестве старших бит номера конфигурационного регистра UReg используются линии AD[27:24].

Для доступа к устройствам других шин используются конфигурационные транзакции типа 1. Здесь номер шины Bus, на котором расположено искомое устройство, определяется битами AD[23:16]; номер устройства Dev — битами AD[15:11], номер функции Fun — битами AD[10:8]; номер регистра Reg — битами AD[7:2]; при этом AD[1:0] = 01 является признаком типа 1. В PCI-X для Mode 2 по AD[27:24] передаются старшие биты номера регистра (UReg).

Поскольку биты AD[1:0] используются для идентификации типа транзакции, конфигурационные регистры адресуются только двойными словами. Различение двух типов конфигурационных транзакций используется для построения иерархической системы конфигурирования PCI. Мост, приведший конфигурационную транзакцию к шине, на которой расположено целевое устройство, преобразует транзакцию типа 1 в транзакцию типа 2. Заметим, что в отличие от транзакций по адресам памяти и ввода/вывода, которые от инициатора до адресованного целевого устройства доберутся при любом их взаимном расположении, конфигурационные транзакции распространяются по иерархии шин только «вниз» — от хоста (центрального процессора) через главную шину к подчиненным. Таким образом, только хост может выполнить конфигурирование всех устройств PCI (включая и мосты), и это его «почетная обязанность».

В широковещательной команде PCI, называемой специальным циклом, в фазе адреса информация по шине AD не передается. Любой агент шины PCI может вызвать специальный цикл на любой конкретно заданной шине, используя транзакцию конфигурационной записи типа 1, указав номер шины в битах AD[23:16]. При этом в полях номеров устройства и функции (в битах AD[15:8]) должны быть все единицы, в поле номера регистра — нули. Эта транзакция проходит между шинами независимо от взаимного расположения источника и целевой шины, и только самым последним мостом, приведшим ее к целевой шине, преобразуется в собственно специальный цикл.

Читайте также: