Управляющая память содержится в устройстве управления

Обновлено: 03.07.2024

Организация управления процессом обработки информации

Устройство управления выполняет две основные функции:

1. Управление выполнением операции

2. Выборка команд программы в нужной последовательности

Каждая команда представляет собой совокупность микроопераций, реализуется команда микропрограммой, выполняется за несколько тактов, причем в каждом такте может быть одна или несколько микрокоманд. Под рабочим тактом понимается интервал времени, отведенный на выполненные микрооперации.

Для реализации команды нужно подать на управляющие входы операционного блока соответствующие управляющие сигналы.

Существует 2 подхода организации управления выполнения операции:

1) Управляющий автомат с жесткой логикой или аппаратное управление.

2) Управляющий автомат с микропрограммной логикой или микропрограммное управление.

Для 1 каждой микрооперации строится набор комбинационных схем, которая формирует сигналы управления на определенных тактах.

Для 2 Каждой управляющей операции ставится в соответствие совокупность хранимых в памяти слов и микрокоманд, каждая микрокоманда содержит информацию, во-первых о тех микрооперациях которые нужно выполнить в течении 1 машинного такта, и во-вторых, указания на следующую микрокоманду.

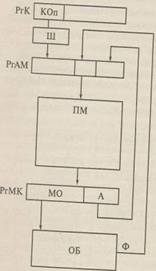

Общая схема организации , выглядит следующим образом:

В любом случае код операции, подлежащий выполнению, должен быть расшифрован.

- При аппаратном управлении код операции попадает в дешифратор.

- При микропрограммном управлении код операции попадает сначала в управляющую память

Управление с жесткой логикой

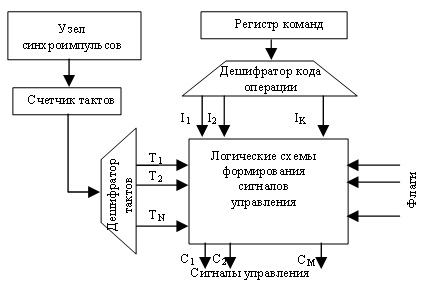

Управляющие автоматы с жесткой логикой представляют собой логические схемы, вырабатывающие собой управляющие сигналы. Типовая структурная схема управляющего автомата с жесткой логикой выглядит следующим образом:

Регистр кода операции является частью регистра кода команд и задает код исполняемой команды.

Дешифратор кода операции - вырабатывает единичный сигнал на j выходе, если выполняется j операция. Выборка алгоритма управления.

Счетчик тактов - с каждым тактом меняет свое состояние либо в сторону увеличения, либо в сторону уменьшения. Номера тактов от 1 до n.

Дешифратор тактов – активизирует выход, соответствующий номеру тактов.

Логические схемы – для каждой команды возбуждают формирователи управляющих сигналов, для выполнения требуемой в данном такте микрооперации.

Схема образования управляющих сигналов выглядит следующим образом:

Главным недостатком такой схемы является то, что

1) на выполнение различных команд отводится одинаковое количество тактов

2) Логику работы такого управляющего автомата , можно изменить только путем перестраивания схем, от сюда следует что система команд микропроцессором с аппаратным управлением – фиксировано.

Основным достоинством аппаратного управления является высокое быстродействие. Такие автоматы чаще всего используются в микропроцессорах типа RISC.

Для формализации работы управляющего автомата и синтеза оптимального варианта используется описание работы операционного блока в виде микропрограммы или графа, последующим построением соответствующего управляющего автомата.

Пример схемы управляющего автомата мили:

Управление с микропрограммной логикой.

В большинстве современных процессоров управляющие автоматы с микропрограммной логикой используются только совместно с аппаратным управлением. В отличие от аппаратного управления, где управляющие сигналы формируются логическими схемами в зависимости от входных сигналов и состояния автомата в микропрограммной управлении управляющие сигналы хранятся в запоминающем устройстве или памяти микрокоманд.

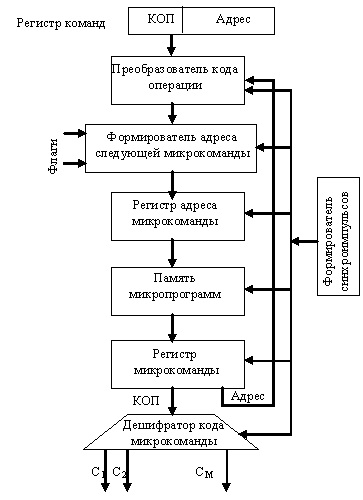

Схема автомата с микропрограммным управлением:

Набор входных значений U(t), Z(t), q(t) – можно отождествить с адресом управляющей памяти, в которой хранятся выходные сигнала управления V(t) и следующее состояние автомата q(t).

Работа автомата выглядит следующим образом: тактирование автомата осуществляется по синхросигналу

CLK=1 – такт CLK = 0 –пауза

Состояние автомата меняется в паузах и определяется набором значений переменных q(t).

Пусть в такте t регистр адреса микрокоманды РгМК записаны U(t), Z(t), q(t). В регистре микрокоманд находится управляющий сигнал V(t). В паузе перед тактом t+1 в регистре адреса микрокоманды эти значения сохраняются, а из управляющей памяти выбираются сигналы V(t+1). Значения сразу записываются в регистр РгМК при появлении такта CLK=1 , на выходе РгМК формируется сигнал V(t+1), которое инициирует выполнение операции в операционном блоке. И следующее состояние команды q(t+1). *** после этого рабочий цикл повторяется.

Тактовый сигнал CLK воздействует так же на операционный блок, обеспечивая восприятие сигналов управления только в момент такта. Управляющая память может быть как постоянным так и оперативным запоминающим устройством. Если память является оперативным запоминающим устройством, это позволяет загрузить в микропроцессор любую систему команд.

Схема формирования адреса следующей микрокоманды служит для устранения эффекта большой управляющей памяти, она переадресует повторяющиеся адреса микрокоманд в одну ячейку памяти, тем самым сокращая объем управляющей памяти и памяти микрокоманд. По скольжу регистр адреса микрокоманд имеет очень большую разрядность, то и управляющая память получается большой ёмкости. Большая часть микрокоманд исполняются, как правило, последовательно. Это приводит к тому, что группа адресов будет ссылаться на одну и ту же ячейку памяти следующей микрокоманды. Например необходимо проверить содержимое знака регистра

2 3 =8 – адресов ссылаются на 1 микрокоманду. При этом фактически в формировании адреса участвует только старший бит признака, а остальные могут принимать абсолютно произвольные значения. В этом случае для нашего примера получается, что 2 3 = 8 – адресов ссылаются на 1 микрокоманду.

Для устранения эффекта большой УП используют схему формирования адреса МК, которая переадресует повторяющиеся адреса МК в одну ячейку памяти, тем самым, сокращая необходимый объем памяти микрокоманд.

09. Классификация, структуры, функции устройств управления

Устройство управления (УУ) — важнейшая часть ВМ, организующая автоматическое выполнение программ (путем реализации функций управления) и обеспечивающая функционирование ВМ как единой системы. Для пояснения функций УУ ВМ следует рассматривать как совокупность элементов, между которыми происходит пересылка информации, в ходе которой эта информация может подвергаться определенным видам обработки. Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ), то есть управление вычислительным процессом сводится к выдаче нужного набора СУ в нужной временной последовательности. Основной функцией УУ является формирование управляющих сигналов, отвечающих за извлечение команд из памяти в порядке, определяемом программой, и последующее исполнение этих команд. Кроме того, УУ формирует СУ для синхронизации и координации внутренних и внешних устройств ВМ. Генерируемая управляющим устройством последовательность управляющих сигналов задается поступающими на входы устройства кодом операции, сигналами из операционного блока, несущими информацию об особенностях операндов, промежуточных и конечного результатов операции, а также синхросигналами, задающими границы тактов.

Классифицировать УУ можно по различным признакам: по уровню централизации, по типам длительности тактов в УУ, по реализации хранения алгоритмов микроопераций.

По уровню централизации:

· Централизованные (УУ – один в ВМ)

· Децентрализованные (в каждом блоке – свой УУ)

· Смешанные (1+2 – конвейеров лучше)

По типам длительности тактов:

· Синхронизованные. Длительность такта = const .

· Асинхронные. И длительность такта и цикла – переменные. Это обеспечивает самое высокое быстродействие, но возникают сложности в настройке.

Для организации:

· Используют признак завершения операции.

· Группируют микрооперации – по признаку длительности (в каждой группе – свое время выполнения).

· Синхронно – асинхронные. Длительность такта = const , длительность цикла – переменная (из-за разного количества тактов)

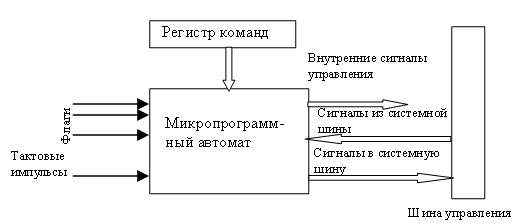

Помимо кода операции при работе БУ используются флаги, т. е. признаки, характеризующие результаты выполнения предшествующей операции. Они необходимы для организации выполнения команд условного перехода. Блок управления вырабатывает сигналы при поступлении на него тактовых импульсов. Кроме того, он получает сигналы от системной шины, например запросы прерывания, подтверждения приема информации и т. п.

Блок управления формирует управляющие сигналы, направляемые в различные устройства и блоки компьютера, прежде всего в процессор. Эти сигналы служат для управления перемещением данных между регистрами, работой устройств, инициирования тех или иных функций. Сигналы управления направляются также в шину для передачи в блоки памяти и на устройства ввода-вывода.

Действия в операционном блоке в течение одного такта называются микрооперациями (МО), а любая операция или команда, выполняемая за несколько тактов, описывается некоторой микропрограммой, определяющей последовательность действий при выполнении этой команды. Сигналы управления, формируемые БУ и поступающие на входы операционного устройства, вызывают в нем выполнение микрооперации. Поскольку блоки управления формируют сигналы для выполнения микроопераций, их часто называют микропрограммными автоматами.

В зависимости от способа формирования сигналов управления микрооперациями различают два типа микропрограммных автоматов: с «жесткой» и программируемой логикой.

Устройства управления с «жесткой» логикой. Код операции и номер такта в управляющем автомате с «жесткой» логикой (рис. 5.8) поступают на дешифраторы DC и затем на логические схемы формирования сигналов управления. На эти же схемы, представляющие собой наборы схем совпадения, поступают различные осведомительные сигналы, которые характеризуют результат выполнения: предыдущей операции или микрооперации.

Сигналы для каждой микрооперации в автомате с «жесткой» логикой формируются своим собственным набором логических схем, который невозможно изменить, не меняя всю систему управления компьютером, что и обусловливает название автомата. В состав его схемы входят счетчик и дешифратор тактов, дешифратор кода операции и логические схемы формирования сигналов управления. Время срабатывания этих логических схем мало, поэтому такие аппаратно реализованные микропрограммные автоматы обеспечивают наибольшее быстродействие. Однако их сложность возрастает с расширением системы команд, так как для каждой операции в них должен быть предусмотрен собственный набор схем.

Эти особенности автоматов с «жесткой» логикой привели к тому, что они находят применение в RISC-процессорах, а в компьютерах с расширенной системой команд обычно используют иной подход — микропрограмму, хранимую в специальной памяти.

Второй тип управляющего автомата — автомат с хранимой в памяти логикой. Управление каждой операцией, входящей в систему команд компьютера, осуществляется с помощью хранимых в памяти слов. Эти управляющие слова, или микрокоманды, содержат информацию о микрооперациях, выполняемых в течение одного машинного такта и осуществляющих элементарное преобразование над данными, и указание, где находится следующая микрокоманда. Такое управление получило название микропрограммного.

Микропрограммы для каждой команды компьютера можно разместить в специальной памяти микропрограмм. Таким образом, процесс командного управления становится двухступенчатым: сначала нужно извлечь из основной памяти компьютера команду, а затем для ее выполнения извлечь из памяти микропрограмм последовательность микрокоманд. Для реализации такого двухступенчатого процесса требуется быстрая постоянная память довольно большого объема.

Основное место в типичной структуре устройства управления с хранимой в памяти логикой (рис. 5.9) занимает память микропрограмм (ПМ), в которой находятся все выполняемые микрокоманды. Она является постоянной памятью; адрес очередной микрокоманды (РгАМ) определяется кодом текущей операции (КОп из регистра команд преобразуется шифратором Ш), флагами Ф, полученными при выполнении предыдущей операции (из регистра флагов), и адресной частью предыдущей микрокоманды (А).Очередная МК считывается из памяти и заносится в регистр RG мк, откуда СУ МО поступают в ОБ.

Обобщенная структура управления

В обобщенной структуре УУ (рис. 6.3) можно выделить две части: управляющую и адресную. Управляющая часть УУ предназначена для координирования работы операци онного блока ВМ, адресной части устройства управления, основной памяти и дру гих узлов ВМ. Адресная часть УУ обеспечивает формирование адресов команд и исполнитель ных адресов операндов в основной памяти.

В состав управляющей части УУ входят:

* регистр команды (РК), состоящий из адресной (Адрес) и операционной (КОп, СА) частей; *микропрограммный автомат (МПА); * узел прерываний и приоритетов (УПП)

Регистр команды РК предназначен для приема очередной команды из запоминающего устройства. Микропрограммный автомат на основании результатов расшифровки операционной части команды (КОп, СА) вырабатывает определенную последовательность микрокоманд, вызывающих выполнение всех целевых функций УУ.

Узел прерываний и приоритетов позволяет реагировать на различные ситуации, связанные как с выполнением рабочих программ, так и с состоянием ВМ.

Адресная часть УУ включает в себя:

*операционный узел устройства управления (ОПУУ); *регистр адреса (РгА); *счетчик команд (СК).

Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Содержимое РгА и СК посылается в регистр адреса основной памяти (ОП) для выборки операндов и команд соответственно.

ОПУУ, называемый иначе узлом индексной арифметики или узлом адресной арифметики, обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выпол

Устройство управления. Микропрограммный автомат

- тактовые импульсы — с каждым импульсом УУ выполняет одну или несколько микроопераций;

- код операции — поступает из регистра команды и используется, чтобы определить, какие микроопераций должны выполняться;

- флаги — требуются для оценки состояния процессора, что необходимо для выполнения команд условного перехода;

- сигналы из системной шины — обслуживание прерывания, прямого доступа в память. В свою очередь УУ, а точнее микропрограммный автомат, формирует следующую выходную информацию:

- внутренние сигналы управления — перемещают операнды из регистра в регистр и инициируют работу операционных устройств;

- сигналы в системную шину — управляющие сигналы в память или в устройства ввода-вывода.

Модель устройства управления

Как отмечалось, процесс функционирования ЭВМ состоит из последовательности элементарных действий в ее узлах. Такие элементарные действия, выполняемые в течение одного такта сигналовсинхронизации, называются микрооперациями. Совокупность одновременно выполняемых микроопераций образует микрокоманду.

Последовательность микрокоманд, определяющая порядок реализации машинного цикла, составляет микропрограмму. Микропрограммный автомат определяет микропрограмму как последовательность выполнения микроопераций. В общей структуре УУ можно выделить две части: управляющую и адресную. Управляющая часть предназначена для координирования работы операционного блока, адресной части, основной памяти и др. Адресная часть обеспечивает формирование адресов команд и адресов операндов в основной памяти. Состав управляющей части: регистр команды, микропрограммный автомат, узел прерываний и приоритетов. Микропрограммный автомат на основе декодирования команды вырабатывает определенную последовательность микрокоманд. В зависимости от способа формирования микрокоманд различают микропрограммные автоматы с жесткой и программируемой логикой. Адресная часть УУ включает в себя: операционный узел устройства управления (ОПУУ), регистр адреса, счетчик команд. Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Их содержимое посылаются в регистр адреса основной памяти. ОПУУ обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выполнении команд перехода. Иногда ОПУУ совмещают с основным операционным устройством. Ниже будет рассмотрена схема ОПУУ процессора i8086.

Микропрограммный автомат с жесткой логикой. Микропрограммный автомат с программируемой логикой

Микропрограммный автомат с жесткой логикой

Тип микропрограммного автомата определяет название всего УУ. В микропрограммном автомате с жесткой логикой (см. рисунок ниже) выходные сигналы управления реализуются за счет однажды соединенных логических схем. Микропрограммный автомат с жесткой логикой. Код операций (КОП), хранящийся в регистре команды, используется для определения того, какие сигналы управления и в какой последовательности должны формироваться. При этом, желательно иметь в УУ отдельный логический сигнал для каждого кода операции (IK). Это может быть реализовано с помощью дешифратора.

Микропрограммный автомат с жесткой логикой

Сигналы управления, по которым выполняется микрооперация, должны вырабатываться в строго определенные моменты времени, поэтому все сигналы управления "привязаны" к импульсам синхронизации. Счетчик тактов сбрасывается (устанавливается в состояние Т1) по окончании цикла очередной команды. Цикл команды может потребовать разного количества тактов. На каждом такте вырабатывается своя микрокоманда, состоящая из нескольких сигналов управления. Дополнительным фактором, влияющим на выработку сигналов управления, являются флаги.

Микропрограммный автомат с программируемой логикой

Отличительной особенностью микропрограммного автомата с программируемой логикой является наличие памяти микропрограмм. Каждой команде вычислительного устройства в этой памяти соответствует микропрограмма. Идею микропрограммирования сигналов управления предложил в 1951 г. Морис Уилкс (Кембриджский университет, Британия). ЭВМ стала иметь три уровня выполнения команд: между командами и сигналами управления появилась микропрограмма. Команда ЭВМ интерпретировалась в микропрограмму. Аппаратное обеспечение должно было выполнять только микропрограммы с ограниченным набором микрокоманд, отсюда существенно уменьшались аппаратные затраты. К 70-м годам идея о том, что написанная программа сначала должна интерпретироваться микропрограммами, а не выполняться непосредственно электроникой, стала преобладающей. Однако в современных процессорах, когда аппаратные затраты стали менее существенны, отказались от идеи микропрограммирования, так как она стала сдерживать рост производительности. Типичная схема микропрограммного автомата приведена на рисунке ниже.

Микропрограммный автомат с программируемой логикой

Запуск микропрограммы выполнения операции осуществляется путем передачи кода операции из регистра команды на вход преобразователя, в котором код операции (КОП) преобразуется в начальный адрес микропрограммы. Выбранная по этому адресу из памяти микропрограмм микрокоманда заносится в регистр. Микрокоманда содержит КОП и адресную часть. КОП поступает на дешифратор и формирует управляющие сигналы, адрес передается для формирования адреса следующей микрокоманды. Этот адрес может зависеть от флагов, КОП, внешних устройств.

Целью работы является проверка усвоения материалов по архитектуре операционного устройства центрального процессора ВМ и взаимодействия входящих в нее элементов.

Управляющее слово ЦП составляется из разрядов управления устройств, входящих в ОУ ЦП.

Для выполнения контрольной работы необходимо уяснить порядок функционирования составляющих операционное устройство элементов вычислительной техники: мультиплексоров, дешифратора, арифметико-логического устройства (АЛУ), регистров и оперативного запоминающего устройства.

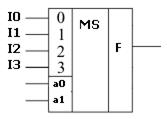

Из многих информационных входов I0…I3 мультиплексор подает на выход один, соответствующий коду, установленному на управляющих входах a1, a0. Структурная схема мультиплексора имеет вид:

Рис. 1. Схема мультиплексора.

| a1 | a0 | F |

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | I3 |

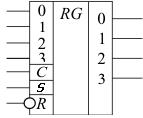

Это устройство, которое имеет единицу только на одном из выходов, соответствующему коду входных информационных сигналов.

Дешифратор на схемах обозначается следующим образом:

Рис. 2. Схема дешифратора.

Таблица соответствия для двухвходового дешифратора имеет вид:

| Е | Х2 | Х1 | L0 | L1 | L2 | L3 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | X | X | 0 | 0 | 0 | 0 |

Регистры обычно строятся на D триггерах. Обозначение регистра на схемах может иметь вид:

Рис. 3. Схема регистра.

АЛУ выполнено на основе комбинационных схем, выходные состояния которых полностью определяются входными информационными и управляющими сигналами.

Таблица микроопераций АЛУ

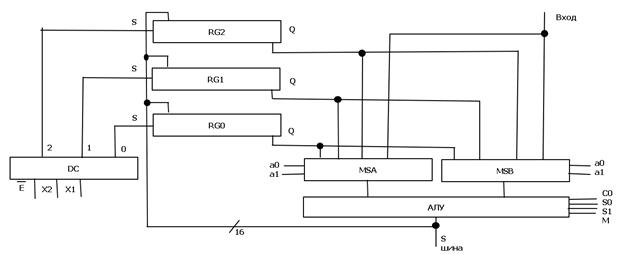

Операционное устройство (ОУ) осуществляет операции (арифметические и логические) над входными информационными сигналами. Характер операций, входные и выходные сигналы (регистры, вход, выход и оперативное запоминающее устройство) определяются управляющими сигналами устройств, входящих в состав ОУ.

Управляющее слово ВМ составляется из управляющих разрядов MSA, MSB, АЛУ, DS, MSM, WR.

Задача устройства управления – обеспечить выдачу управляющего слова ЦП. Иначе он называется микрокод, который управляет работой аппаратуры ЦП. Обычно он записывается в постоянное запоминающее устройство (ПЗУ) центрального процессора (прошивается).

Рис. 4. Схема операционного устройства.

Задача контрольной работы состоит в том, чтобы расписать управляющее слово ЦП для различных микроопераций.

| № №варианта | Записать управляющее слово |

| 1 | Sß INPR IR |

| 2 | INPRß IR MAR |

| 3 | IRß MAR OUTR |

| 4 | MARß OUTR – AC |

| 5 | OUTRßAC – MDR – 1 |

| 6 | ACß MDR + PC + 1 |

| 7 | MDRß PC + INPR |

| 8 | OUTRß |

| 9 | Sß INPR + 1 |

| 10 | INPRß IR + MAR |

| 11 | IRß MAR + OUTR + 1 |

| 12 | MARß OUTR – AC – 1 |

| 13 | OUTRß AC – MDR |

| 14 | ACß |

| 15 | MDRß |

| 16 | PCß |

| 17 | OUTRß IR – 1 |

| 18 | IRß |

| 19 | PCß |

| 20 | Sß |

| 21 | INPRß MAR + OUTR |

| 22 | MDRß OUTR + IR + 1 |

| 23 | ACß IR – PC – 1 |

| 24 | MARß INPR – AC |

| 25 | PCß |

| 26 | IRß OUTR + PC |

| 27 | OUTRß MDR + INPR + 1 |

| 28 | Sß INPR – AC – 1 |

| 29 | MDRß AC – MAR |

| 30 | INPRß |

| 31 | ACß |

| 32 | MARß |

| 33 | Sß OUTR |

| 34 | Sß AC+OUTR |

| 35 | Sß IR+INPR+1 |

| 36 | SßOUTR – MDR |

| 37 | SßINPR – MAR – 1 |

| 38 | SßIR+1 |

| 39 | SßOUTR – 1 |

| 40 | Sß AC PC |

Сделать выводы по проделанной работе.

ПАРА_АрхВМиС_Лекция_СМИРНОВ_Н_А_ИНБО-01,-02, -03,04,- 05, 06,18

1. Рассмотрим схему центрального процессора (операционное устройство) в 2 этапа. Сначала рассмотрим упрощенную схему. Затем усложним её.

Рис. 1 Схема вспомогательная

Подачей управляющих сигналов на дешифратор, мультиплексоры и АЛУ ведает устройство управления ЦП, которое выдает так называемое управляющее слово процессора. Оно состоит из разрядов управления этими устройствами. – по 2 разряда на мультиплексоры MSA и MSB, 3 разряда на дешифратор DС и 4 разряда на АЛУ.

1.Пусть надо в RG1 поместить сумму чисел из RG2 и RG0:

| 10 | 00 | 0010 | 001 |

| 11 | ХХ | 0000 | 010 |

| 10 | 00 | 110Х | 000 |

| 01 | ХХ | 1111 | 1ХХ |

Рассмотрим более полный вариант схемы ЦП.

Рис. 2. Схема ОУ ЦП

Управляющее слово ВМ будет составлено из управляющих разрядов MSA, MSB, АЛУ, DS, MSM, WR.

Рассмотрим примеры управляющего слова ЦП для некоторых операций:

| MSA | MSB | АЛУ | DC | MSM | WR |

| 001 | 100 | 0010 | 0001 | x | 0 |

| MSA | MSB | АЛУ | DC | MSM | WR |

| 000 | xxx | 0000 | 0011 | x | 0 |

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | xxx | xxxx | 0100 | 1 | 0 |

Пустой такт NOP

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | xxx | xxxx | 1xxx | x | 0 |

Таким образом, мы спроектировали схему операционного устройства центрального процессора учебной ВМ.

5.9. Устройство управления ЦП

Задача устройства управления – обеспечить выдачу управляющего слова ЦП. Иначе он называется микрокод, который управляет работой аппаратуры ЦП. Обычно он записывается в постоянное запоминающее устройство (ПЗУ) центрального процессора (прошивается).

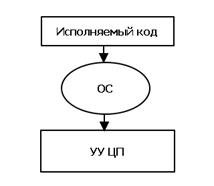

Что должно делать УУ? У нас есть исполняемый код программы. Дальше в ходе выполнения исполняемого кода на ВМ им занимается операционная система – программа, которая выдаёт команды для УУ ЦП.

Рис. 3 Алгоритм управления в ВМ

Последовательность работы устройства управления задается циклами.

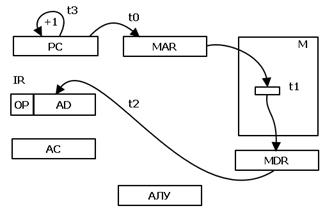

Для начала рассмотрим цикл выборки команды. Ведь прежде чем выполнить команду, надо выбрать её из памяти ВМ.

Рис. 4 Цикл выборки команды

Для выборки команды из памяти ВМ надо, во-первых, поместить адрес команды из регистра адреса команды в регистр адреса памяти, во-вторых, прочитать команду из ячейки памяти в регистр данных памяти, в-третьих. Переслать команду в регистр команды, в-четвертых, подготовить счетчик команд для выборки следующей команды – инкрементировать PC.

То есть, последовательно надо выполнить 4 действия, обозначенные на рис. 4 t0, t1, t2, t3. Следовательно, цикл выборки команды осуществляется за 4 такта.

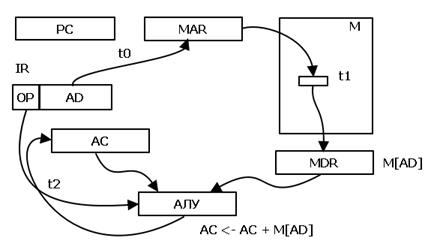

Само выполнение команды происходит следующим образом:

Рис. 5 Цикл выполнения команды

Рассмотрим цикл выполнения команды на примере операции сложения.

Нулевой такт – пересылка адреса операнда из регистра команды в регистр адреса памяти. Первый такт – выборка из памяти операнда и размещение его в регистре данных памяти. Второй такт – собственно выполнение сложения в АЛУ с размещением результата в аккумуляторе.

Здесь мы рассматриваем выполнение команды с прямой адресацией, когда в адресном поле команды находится адрес операнда.

Машину Фон Неймана стали совершенствовать, поскольку для выполнения некоторых команд более удобными являются другие методы адресации операндов. Всего способов адресации насчитывается около 20. Из них в каждой конкретной ВМ используется только часть, по выбору конструкторов ВМ и в соответствии с назначением ВМ (ориентированием ВМ на обработку определённых видов информации).

Допустим, что у нас в памяти содержится такая информация:

| Адрес | Содержание |

| 30 | 40 |

| 40 | 50 |

| 50 | 60 |

Рассмотрим выполнение команды LDA (загрузку аккумулятора) с помощью различных методов адресации.

Существуют и другие способы адресации, которые здесь мы не будем рассматривать.

В общем случае для указания способа адресации в команде выделяется отдельное поле, содержащее необходимое количество разрядов. Для декодирования способа адресации при этом необходим ещё один цикл – цикл дешифрации команды.

Таким образом, мы получили наличие в УУ ЦП следующих циклов:

1) Цикл выборки команды – С0;

2) Цикл дешифрации команды – С1;

3) Цикл выполнения команды – С2;

4) Цикл обработки прерывания – С3.

Рис.6. Алгоритм работы устройства управления ЦП ВМ

Последний цикл необходим для обработки требований прерывания, вырабатываемых внешними устройствами ВМ (например, клавиатурой, устройством ввода/вывода и т.д.) или при появлении нештатных ситуаций при выполнении команд (деление на ноль, переполнение разрядов и др.). Как происходит цикл обработки прерывания мы рассмотрим позднее – при изучении операционных систем.

На основании изложенного алгоритм работы УУ ЦП имеет вид, представленный на рис. 6.

Как видите, ВМ реагирует на прерывание только после окончания выполнения очередной команды программы. В противном случае очень трудно запомнить текущее состояние ЦП для возврата в программу после обработки прерывания.

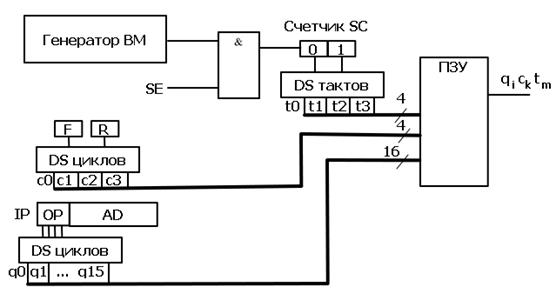

5.10. Структурная схема УУ ЦП

Структурная схема УУ ЦП изображена на рис. 7.

В основе УУ имеется ПЗУ; сигналы, вырабатываемые на его выходе, управляют работой ВМ. Генератор ВМ вырабатывает тактовую частоту. Сигнал SE представляет собой сигнал разрешения работы и останов. При SE=0 сигналы генератора ВМ не проходят через схему совпадения, и схема управления не работает – останов. При SE=1 сигналы генератора ВМ проходят через схему совпадения и поступают на вход двухразрядного счетчика, соединённого по выходу с дешифратором тактов. Логика работы последнего приведена на рис. 7.

Рис. 7. Структурная схема УУ ЦП

| ГИ |

| t0 |

| t1 |

| t2 |

| t3 |

Рис. 8. Временная диаграмма работы DС тактов

В ВМ такты не пересекаются по времени.

DС циклов работает по выходам двух триггеров F и R. В зависимости от состояния этих триггеров формируется сигнал на соответствующем его выходе.

| F | R | Цикл | Обозначение цикла |

| 0 | 0 | Выборки команды | С0 |

| 0 | 1 | Дешифрации команды | С1 |

| 1 | 0 | Выполнения команды | С2 |

| 1 | 1 | Прерывания | С3 |

DС команды работает по состоянию разрядов регистра команд, соответствующих полю кода операции. В нашем случае код имеет 4 разряда, что соответствует 16 выходам дешифратора команд.

Выходы всех трех дешифраторов составляют адрес ПЗУ, в котором записана (прошита) информация соответствующая содержимому управляющего слова процессора данного такта данного цикла данной команды.

Такова в общем виде структура УУ ЦП.

Таблица команд учебной ВМ представлена в таблице.

Обычно ВМ содержит команды различной длины – безадресные, одноадресные, двухадресные и др. В нашей учебной ВМ мы рассматриваем все команды единой длины равной 16 двоичным разрядам. Поэтому безадресные команды (с номерами от 12 до 15) содержат фиктивный адрес, равный FFF.

Рассмотрим для примера команду сложения ADD. Для неё в поле кода операции будет иметься значение 2 16-ричного кода. В адресном поле находится 12-разрядный адрес AD. Напишем микрокоманды циклов выборки и выполнения команды.

Так выполняются микрокоманды ВМ в циклах выборки и выполнения команды сложения. Аналогичным образом можно описать порядок выполнения любой команды из перечня команд ВМ.

ВМ фон Неймана первоначально была рассчитана, как и наша учебная ВМ, только для одного типа адресации – прямой адресации. Для других типов адресации, что задаётся обычно в специальном поле команды, требуется наличие цикла дешифрации команды и осуществление выборки операндов соответствующим образом. Мы цикл дешифрации команды не рассматриваем, поскольку считаем, что используется только прямая адресация операндов.

Следующая контрольная работа состоит в том, чтобы вы научились строить команды из микрокоманд подобно рассмотренному примеру. Объем работы в контрольной работе велик. Для оформления работы надо использовать по крайней мере один лист формата А4.

Рассмотрим типовую задачу и приведём пример её решения.

Задача. По адресу 5А8 записана команда сложения ADD с адресом F12. По этому адресу записан операнд 731F. В регистре АС находится операнд 8721. Определить информацию, которая будет иметься в регистрах ВМ PC, MAR, MDR, IR, AC после выполнения данной команды.

Читайте также: