Usb phy что это

Обновлено: 05.07.2024

Продолжим тему программирования обмена данными по шине USB.

Причём поработаем мы с аппаратной шиной USB HS контроллера, скорость которой в 40 раз больше, чем скорость шины USB FS, и составляет 480 мегабит в секунду.

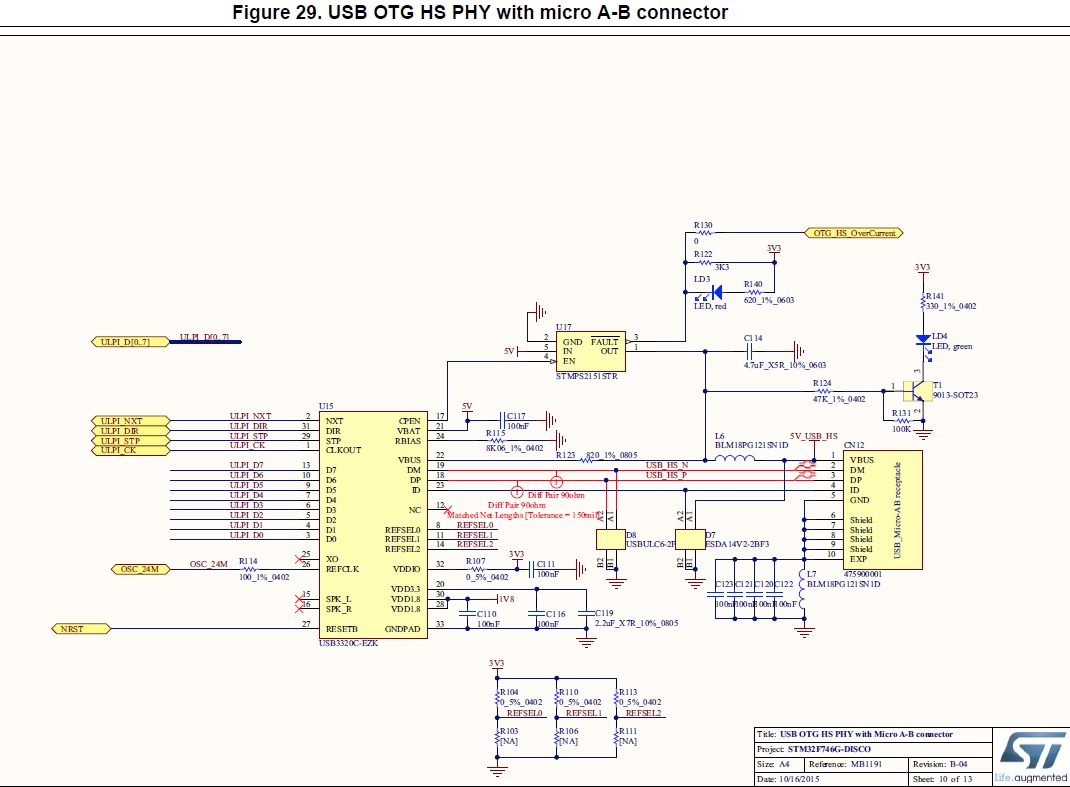

В качестве подопытной платы мы будем использовать полюбившуюся многим плату STM32F746G-DISCOVERY, с которой мы уже очень много времени успешно и плодотворно работаем, и, надеюсь, ещё много будем работать для того, чтобы средства её оплаты были потрачены недаром. Данная плата в нашем случае хороша не только тем, что на ней установлен мощный микроконтроллер STM32F746NG и удобный дисплей для вывода оперативной информации, но и тем, что на её борту также присутствует микросхема USB3320C-EZK, преобразующая параллельный интерфейс USB HS ULPI в последовательный USB HS PHY, очень хорошо понятный нашей повседневной шине USB, которую мы постоянно используем. А как мы знаем, контроллер не имеет аппаратной шины USB HS PHY ввиду того, что в силу своих аппаратных характеристик он не может разогнаться до скорости передачи данных 480 Mbps. Если вдруг у вас под рукой не окажется подобной платы, то есть и альтернативные способы использования данной шины путём подсоединения к отладочной плате, не имеющей микросхемы-преобразователя, модуля с подобной микросхемой. Для подключения можно воспользоваться схемой подключения данной микросхемы в плате STM32F746G-DISCOVERY

В качестве устройства, которое мы будем подключать по шине USB HS PHY мы возьмём обычный чистый отформатированный в системе FAT32 FLASH-накопитель USB на 8 гигабайт и подключим его с помощью OTG-кабеля USB следующим образом

Как и в предыдущих занятиях по шине USB, мы не будем вдаваться в её аппаратную организацию в контроллере, так как она отнюдь непростая, поэтому поручим эту прерогативу библиотеке HAL и будем пользоваться её функционалом. А если уж что-то не заладится, то тогда и посмотрим Reference Manual.

Поэтому сразу приступим к проекту.

Прежде чем открывать проект в Cube MX, удалим из папки Src все файлы, которые писали не мы, а именно bsp_driver_sd.c, fatfs.c, stm32f7xx_hal_msp.c, stm32f7xx_it.c и system_stm32f7xx.c.

Аналогичным образом из папки Inc удалим файлы main.h, bsp_driver_sd.h, fatfs.h, ffconf.h, stm32f7xx_hal_conf.h и stm32f7xx_it.h.

Делается это в целях избежания ошибок при генерации кода, так как со времён урока 70 прошло очень немало времени и все библиотеки изменились коренным образом.

Откроем проект в проектогенераторе Cube MX, согласимся с миграцией в новую версию и сначала отключим библиотеку FATFS

Затем отключим SDMMC

Отключим RNG

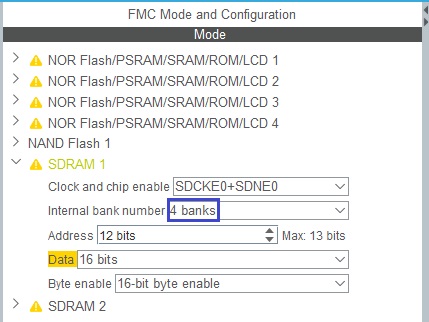

В настройках FMC добавим ещё 2 банка

Включим USB OTG HS

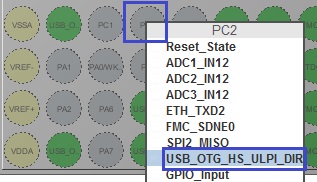

Контакт ULPI DIR переопределим на ножку PC2

Включим USART1, так как основную информацию о ходе нашей программы мы будем всё же получать через данную шину и отображать её в терминальной программе на ПК

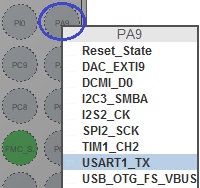

Здесь также переопределяем контакт TX на ножку PA9

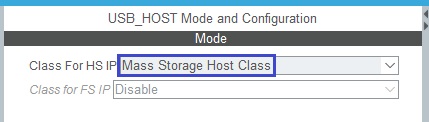

Включим также USB Host

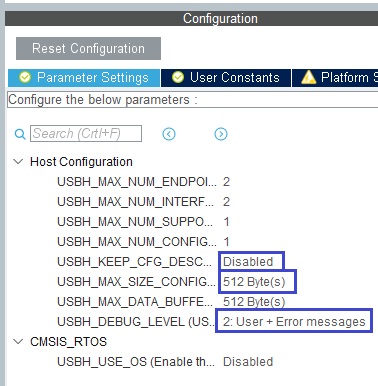

Также произведём его некоторые настройки

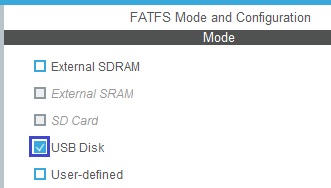

Включим FATFS

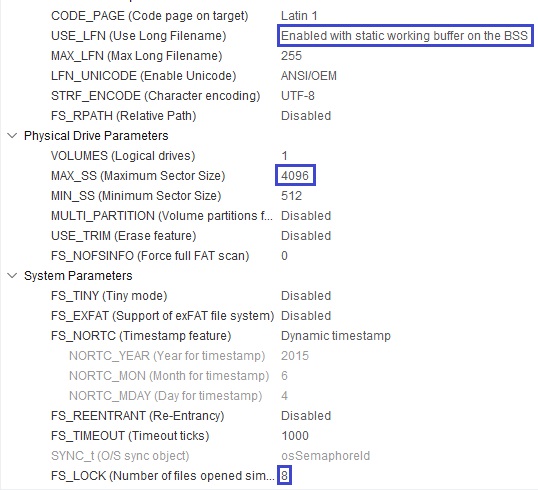

Изменим и здесь определённые настройки, так как мы будем работать с длинными именами

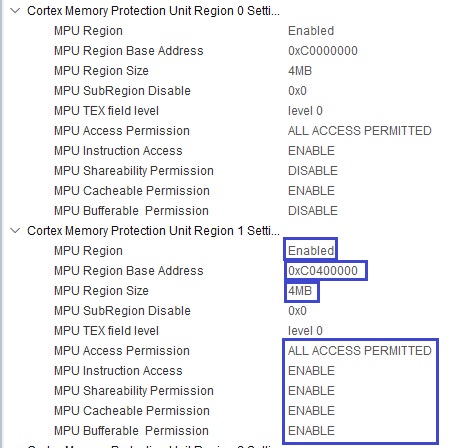

Ещё внесём некоторые изменения в настройки CORTEX_M7 в связи с тем, что мы добавили ещё 2 банка SDRAM

Сохраним настройки, сгенерируем проект для System Workbench, несмотря на предупреждение Cub MX по USB_HOST, и откроем его там. Установим уровень оптимизации в 1, а также уберём при наличии отладочные настройки.

Удалим весь код из пользовательской части бесконечного цикла функции main().

ULPI это интерфейс для организации высокоскоростных IP-систем USB 2.0. Он определяет взаимодействие между контроллерами USB и микросхемами PHY или трансиверами, которые соединяются с реальной физической шиной USB. Аббревиатура ULPI означает UTMI+ low pin interface (UTMI+ с уменьшенным количеством выводов), и он был специально разработан для уменьшения количества выводов корпусов микросхем high-speed USB PHY. Уменьшение количества выводов минимизирует стоимость и место на плате, необходимое для установки и разводки чипа PCB, и уменьшает количество выводов, назначенных для связи с высокоуровневым контроллером USB. В результате этих свойств ULPI быстро стал новым стандартом интерфейса среди разработчиков систем и чипов (SMSC, NXP Semiconductors, Mentor Graphics).

Стандарты UTMI+ и ULPI. ULPI это расширение стандарта UTMI+ PHY. Оба стандарта определяют интерфейсы между высокоуровневым контроллером USB и микросхемами PHY для организации физического соединения с шиной USB, однако ULPI специально предназначен для микросхем PHY. Стандарт UTMI (расшифровывается как USB transceiver macrocell interface) был разработан компанией Intel® для высокоскоростных периферийных устройств (USB v2.0). UTMI позволяет периферийным устройствам подключаться к компьютеру либо на высокой high-speed, либо на полной (full-speed) скорости (для совместимости со старыми PC). Стандарт UTMI+ это расширение оригинального UTMI, которое поддерживает контроллеры OTG и контроллеры хоста на всех скоростях.

Наподобие UTMI+ для встроенного в чип PHY, стандарт ULPI предоставляет основную выгоду для разработчиков решений USB при использовании отдельных микросхем PHY. Оба стандарта поддерживаются организацией ULPI Working Group. Хотя ULPI это не полностью открытая спецификация, любой может свободно присоединиться и стать пользователем ULPI. Зарегистрируйтесь на сайте ULPI Working Group, чтобы получить бесплатную копию документации стандарта.

PHY это очень распространенный термин, когда речь идет о сетей и действительно, даже если вы никогда не слышали этого раньше, это то, что ваш сетевая карта есть, даже тот, который интегрирован с материнская плата. Это довольно важный компонент, поэтому в этой статье мы собираемся объяснить, что это такое, что это такое. для и вообще все что ты должен знать об этом.

Обычно, когда речь идет о PHY, это обычно делается в сочетании с сетевым контроллером, который, конечно, является частью сетевой карты. Сегодня он есть у всех сетевых карт, в том числе на материнских платах. Итак, давайте посмотрим, что это такое и что он делает.

Что такое PHY?

PHY - это сокращение от ” Физический слой «Или« физический уровень »на испанском языке. Это электронная схема, обычно реализуемая в интегральная схема (в разговорной речи известный как «таракан») и является чем-то необходимым для точной реализации физических соединений сетевых карт. Поэтому является частью сетевой контроллер и служит для соединения канального уровня (называемого MAC-адресом от Media Control Access) с физическим уровнем соединения, таким как разъем RJ-45 сетевой карты.

Устройство PHY обычно включает в себя дополнительный уровень кодирования, называемый PCS (подуровень физического кодирования), и уровень, зависящий от физической среды (PDM), который кодирует и декодирует данные, которые передаются и принимаются.

Таким образом, PHY - это интегрированный чип, который соединяет сетевой контроллер и физический разъем сетевой карты.

Типы и примеры использования

В начале мы говорили вам, что все сетевые карты имеют PHY, но реальность такова, что это только в том случае, если у них есть физические разъемы (вы можете подумать, что было бы абсурдно не иметь их, но в профессиональной среде там есть). являются сетевыми контроллерами, которые не имеют PHY, потому что их функция заключается в управлении другими сетевыми картами, поэтому у вас нет своих собственных разъемов).

В этой заметке будет краткий обзор различных распространённых интерфейсов, которые используются в качестве канала обмена данными между персональным компьютером (ПК) и разрабатываемым\проектируемым устройством (или в пределах устройств только). Заметка, скорее, для начинающих схемотехников \ программистов, которая поможет определиться с начальным выбором, оценив возможности и ограничения описанных интерфейсов.

Краткое сравнение

Плюсы и минусы каждого интерфейса в виде таблицы для наглядности:

- Широкий выбор готовых решений

- Простота интеграции и взаимодействия с МК\ПЛИС

- Низкий входной порог

- Низкая стоимость

- Низкая скорость передачи данных

- Интерфейс наиболее ориентирован на отладочные цели, для передачи ASCII символов, чем для потоков данных

- Широкий выбор готовых решений

- Довольно низкая стоимость (есть МК со встроенным USB PHY)

- Возможность питания устройства

- Низкая\средняя скорость передачи данных

- Средний входной порог при написании custom-устройств

- Высокая скорость передачи данных

- Доступен встроенный интерфейс USB 2.0

- Относительно невысокая стоимость

- Доступны готовые решения

- Продвинутая система питания устройства

- Средний\высокий входной порог

- Повышенные требования к разводке ПП

- Требуется внешний PHY (в рядовых решениях встроенный PHY отсутствует)

- Очень высокая скорость передачи данных

- Возможность расширения пропускной способности путём добавления дополнительных линий

- Высокий входной порог

- Высокая стоимость

- Высокие требования к разводке ПП

- Не мобильное решение

- Очень высокая скорость передачи данных

- Продвинутая система питания устройства

- Высокий входной порог

- Высокая стоимость

- Высокие требования к разводке ПП

- Нет доступных готовых решений

- Широкий выбор готовых решений

- Есть решения с повышенными скоростями передачи данных

- Гальваническая изоляция

- Задержки

- Питание устройства возможно только с дополнительным оборудованием (PoE)

- Довольно габаритный согласующий трансформатор (даже встроенный в разъем)

- Много готовых решений

- Высокая скорость передачи данных

- Гальваническая изоляция

- Высокая дальность работы при сохранении высокой скорости передачи данных

- Горячая замена SFP модуля

- Низкие задержки

- Средний входной порог

- Повышенные требования к разводке ПП

- Нет возможности питания устройства

- Габаритное посадочное место под держатель SFP модуля

- Ощутимый нагрев SFP модуля, его критичность к охлаждению

- Беспроводное соединение

- Гальваническая изоляция

- Широкий выбор готовых решений

- Высокие задержки

- Лимитированная скорость передачи данных по наиболее низкоскоростному клиенту в сети

- Нет возможности питания устройства

- Беспроводное соединение

- Гальваническая изоляция

- Широкий выбор готовых решений

- Низкое потребление

- Высокие задержки

- Сильно лимитированная скорость передачи данных

- Ощутимая зависимость качества приёмного сигнала от помех или препятствий

- Нет возможности питания устройства

Чуть подробнее

Для первых двух зачастую не требуется никаких внешних микросхем, и USB PHY уже содержится в МК\SoC даже начального уровня (к примеру, в STM32F042F6P6 внутри есть даже точный тактовый генератор на 48 МГц, что освобождает от необходимости установки внешнего кварца и поддержка USB 2.0 Full-speed на борту!), чего хватит для большинства задач по управлению или для задач с небольшими потоками данных.

Для High-speed режима работы в большинстве случаев уже потребуется внешний PHY, с которым МК будет взаимодействовать по интерфейсу ULPI или UTMI. Возможные PHY с поддержкой High-speed:

Второй вариант, конечно, очень гибкий, но потребует ощутимых трудозатрат для реализации (особенно если не покупать готовое IP ядро), первый же подойдет для быстрого старта с хорошими примерами от производителей, в качестве примера самые распространённые МС:

А в качестве примера реализации схемотехники USB 3.1 Gen 2 советую посмотреть Intel Cyclone 10 GX FPGA Development Kit.

Более подробно можно почитать на Википедии. Если говорить о наиболее реализуемых вариантах на ПЛИС или ASIC, то вкратце это выглядит так:

В качестве примера реализации схемотехники PCI Express х4 советую посмотреть Intel Cyclone 10 GX FPGA Development Kit.

Варианты от разных компаний внешних PHY для реализации PCI Express с пометкой количества линий:

В навороченных SoC, МК бывает встроенный PHY, в случае создания устройства на средне-бюджетных МК или ПЛИС уже не обойтись без внешнего PHY. В качестве примера немного различных PHY с разными интерфейсами подключения и скоростями:

В качестве примера внешние PHY (так-то корзинку-держатель для оптического модуля можно подключить напрямую к ПЛИС, и из дополнительных элементов потребуются разве что 6 резисторов да фильтры по питанию и развязочные конденсаторы на дифференциальные линии LVDS):

В качестве примера различные WiFi SoC:

Вывод

В итоге можно сказать следующее. Стоит выбирать интерфейс исходя из 4-х основных факторов:

Отобрав большинство интерфейсов (и доступных PHY) по первым двум факторам, окончательный выбор будут определять оставшиеся два, они довольно тесно связаны как между собой, так и с вашими умениями и поставленной задачей: финальный выбор зачастую довольно сложен и зависит от совокупности вашего опыта, итоговой цели, доступного времени на изучение и разработку, доступных материалов и примеров, а также найденных проблем (что тоже немаловажно, т. к. лучше посмотреть заранее Errata и форумы хотя бы бегло, чем потом самому искать баги и почему оно не работает-то!) при работе с этим интерфейсом или даже конкретными PHY для него.

Также хочу отметить, что со многими указанными в статье МС \ SoC \ одноплатными ПК я имел дело и применял, но они могут не являются лучшим вариантом решения вашей задачи , а даны только как небольшой пример. Их выбор гораздо больше и придётся изучать информации очень и очень много для нахождения наиболее оптимального решения вашей задачи .

Читайте также: