Что такое триггер в компьютере

Обновлено: 07.07.2024

Базовым элементом памяти является триггер . Устройство, предназначенное для хранения одного бита информации.

Для более полного понимания вопроса рекомендуется посмотреть статью про элементы памяти . Если без подробностей, то у базового элемента памяти три рабочих режима. Хранение , установка и сброс . Возможность запоминания бита информации приходит при дополнении этой схемы несколькими элементами.

D-триггер это такая же ячейка памяти, но с дополнительной логикой. Она позволяет при высоком уровне сигнала C запоминать состояние линии D . При этом если D нулевая, то триггер сбрасывается, а если D единица, то триггер устанавливается. Таким образом, происходит как бы запоминание сигнала на входе. Единственный недостаток такой схемы это именно срабатывание по высокому уровню тактирующего сигнала.

Промышленные триггеры работают по фронту или спаду тактирующего сигнала.

Если собрать триггер из двух одинаковых половинок, то можно обеспечить тактирование по фронту.

При низком уровне тактового сигнала содержимое D записывается в зеленую половину, но как только низкий уровень тактирующего сигнала сменяется на высокий, содержимое зеленой половины записывается в красную. Состояние линии D записывается в триггер только по переднему фронту тактового сигнала. При этом записанный бит появляется на выходе Q .

Описание элемента памяти на языке Verilog

В языке Verilog для описания триггеров предусмотрена довольно простая конструкция. Это процедурный блок, где в списке чувствительности значится передний фронт тактового сигнала. Для переднего фронта предназначено слово posedge , для заднего фронта negedge .

Внутри процедурного блока присвоение выходу входного сигнала. Если бы в списке чувствительности не значился тактовый сигнал, то такое описание означало бы просто провод. Но тактовый сигнал означает действие только по переднему фронту. Все время между фронтами состояние выхода запоминается и запоминает его D-триггер .

Как мы помним , в состав логической ячейки ПЛИС кроме LUT таблицы входит еще элемент памяти. Это D-триггер с разрешением и асинхронным сбросом. Опишем такой элемент при помощи языка Verilog. Для того чтобы сбрасывать состояние триггера не зависимо от тактового сигнала, необходимо в списке чувствительности указать еще один сигнал, по фронту которого произойдет некоторое событие.

Описание D-триггера с асинхронным сбросом и разрешением Описание D-триггера с асинхронным сбросом и разрешениемНам нужен сброс. Внутри процедурного блока опишем действие, происходящее по высокому уровню сигнала сброса. На выход модуля отправляется ноль. Иначе если сброса нет, то будет происходить другая работа. В случае сигнала разрешения происходит запоминание входного сигнала. Соответственно, если разрешения не будет , то и запоминание не произойдет.

Промоделируем этот триггер. Для этого разработаем модуль теста.

Количество проводов соответствует количеству входов и выходов триггера. Вписываем триггер в состав теста. Соединяем его входы и выходы с проводами. Каждые 50 пикосекунд состояние тактовой линии будет меняться на противоположное. Чтобы это все заработало, нужно задать начальное состояние тактовой линии и сделать это можно в секции initial begin . В начальный момент времени среди всех входных сигналов и у тактовой линии есть какое-то состояние. Посмотрим результат моделирования.

Тактовый сигнал ( clk ) подается непрерывно. В какой-то момент времени сигнал сброса ( aclr ) привел триггер в состояние нуля из состояния неопределенности. Неопределенность это либо ноль либо единица. Это неизвестно, потому как начальное состояние триггера нигде не было указано. Поступление единицы на вход D ни к чему не приводит, потому, что сигнал разрешения нулевой.

Потом в тесте разрешим работу триггера ( en=1 ) и отправим на некоторое время единицу на вход D . Как раз, в момент прихода переднего фронта тактового сигнала бит единица записался в триггер и оказался на его выходе. Как только состояние входного бита изменилось, то запись не произошла сразу, для записи опять же необходим передний фронт тактового сигнала. На этом этапе нужно особенно внимательно подойти к пониманию этих процессов, иначе потом будет непросто.

Использование элементов памяти в модулях поведенческого стиля описания

Теперь посмотрим как ненавязчиво создавать элементы памяти и не перегружать схемы структурным стилем описания. При структурном стиле мы вынуждены описывать экземпляры триггеров и соединять их проводами. Но все можно делать более незаметно. Ниже описание триггера и конъюнкции, причем запоминание результата происходит по переднему фронту тактового сигнала.

Триггер – элемент цифровой техники, бистабильное устройство, которое переключается в одно из состояний и может находиться в нем бесконечно долго даже при снятии внешних сигналов. Он строится из логических элементов первого уровня (И-НЕ, ИЛИ-НЕ и т.д.) и относится к логическим устройствам второго уровня.

На практике триггеры выпускаются в виде микросхем в отдельном корпусе или входят в качестве элементов в состав больших интегральных схем (БИС) или программируемых логических матриц (ПЛМ).

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Типы триггеров и принцип их работы

Существует несколько основных типов триггеров. Перед тем, как разобраться в различиях, следует отметить общее свойство: при подаче питания выход любого устройства устанавливается в произвольное состояние. Если это критично для общей работы схемы, надо предусматривать цепи предустановки. В простейшем случае это RC-цепочка, которая формирует сигнал установки начального состояния.

RS-триггеры

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

D-триггеры

D-триггер («прозрачный триггер», «защелка», latch) относится к категории синхронных устройств, тактируемых по входу С. Также имеется вход для данных D (Data). По функциональным возможностям устройство относится к триггерам с приёмом информации по одному входу.

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

Прозрачность D-триггера не всегда является полезным свойством. Чтобы её избежать, применяются двойные элементы (flip-flop, «хлопающий» триггер), они обозначаются литерами TT. Первым триггером служит обычная защёлка, пропускающая входной сигнал на выход. Второй триггер служит элементом памяти. Тактируются оба устройства одним стробом.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

![Схема работы синхронного T-триггера.]()

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

Практическое использование

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Что такое компаратор напряжения и для чего он нужен

Режимы работы, описание характеристик и назначение выводов микросхемы NE555

Что такое операционный усилитель?

Что такое термистор, их разновидности, принцип работы и способы проверки на работоспособность

Электроника предполагает точное выполнение заданной программы с учетом текущего состояния всей логической схемы. За часть работы электронной цепи отвечают триггеры. Статья опишет — основные типы триггеров, их устройство и принцип работы, а так же расскажет зачем такие устройства используются в электронных схемах. Отдельно будет описан симметричный триггер.

Определение

Что такое триггер? Триггером называют электронное устройство, обладающее способностью довольно долгое время находиться в 1-ом из 2-х стабильных состояний, а так же чередовать их из-за воздействия какого-то внешнего сигнала. Триггер — это по сути простая электроника, от которой зависит работоспособность более сложных систем

Он способен хранить двоичную информацию (ноль или один) после того, как перестанут действовать входные импульсы. Основное назначение устройства, это переключение из одного состояния в другое. Хранит триггер в своей памяти 1 бит информации, которые и определяют его текущее состояние: логический «0» или логическая «1».

Какие входы есть у триггера? Любой триггер может иметь несколько входов, которые бывают:

- Информационными. Они отвечают за общее состояние устройства в момент работы всей цепи.

- Управляющими. Отвечают за установку триггера в предварительное положение и за его дальнейшую синхронизацию.

Работа устройства строится на 2 элементах «И-НЕ», 2 «ИЛИ-НЕ» и других, некоторые разновидности триггеров работают на логических элементах КМОП, ТТЛ, ЭСЛ. Принцип работы любого триггера зависит от количества входов/выходов, а также от типа самого устройства.

В электронике используются устройства на транзисторах или микросхемах. Транзисторные модели применяются при сложных интегральных схемах старого типа. Логическая микросхема обладает меньшими габаритами, хранит информацию без перегрева и перегрузок. Поэтому их используют в более миниатюрных и сложных цепях современной электроники.

Разновидности

Для того чтобы разобраться как работает триггер, необходимо понять к какому классу и типу он относится. Существуют 2 основных класса этих устройств:

- Синхронные с двумя основными классами: статическими и динамическими.

- Асинхронные.

Обе разновидности имеют схожий принцип работы. Отличие заключается только в процессе перехода сигнала из одного состояния в другое. Асинхронные делают это напрямую, а синхронные работают исходя из этого сигнала.

Асинхронные

Асинхронные RS-триггер имеет 2 основных входа «R» и «S». Также предусматриваются выходы «Q» и «Q−». Устройство RS триггера позволяет выполнять следующую последовательность:

Асинхронный RS-триггер условно работает следующим образом:

- При подаче напряжения на вход «S» устройство включается и хранит такое состояние даже при потере положительного сигнала.

- При подаче сигнала на вход «R» устройство отключается, при этом сохраняя логический 0 на выходах.

Схема RS-триггера асинхронного типа самая простая. Она работает без синхронизации с дополнительным входом. Используется RS компонент в простых элементах или как дополнение для более сложных триггеров.

Далее будет представлена УГО, таблица истинности и общая схема такого триггера.

Синхронные

Немного более сложное устройство. Работают с дополнительной синхронизацией сигналов. Эти RS-триггеры также имеют входы «R» и «S», а также выходы «Q» и «Q–». Отличие заключается в наличие синхронизирующего входа «С». Этот контакт нужен для синхронизации входящих сигналов. Называют этот вход «clock» или тактовый. Триггер имеет следующий принцип работы:

- Первоначально сигнал поступает к контакту входа «С» и проходит синхронизацию.

- С контакта «С» сигнал поступает на вход «S» в виде логической 1 или высокого напряжения.

- На «Q» устанавливается логическая 1, а сам цепь при этом включается.

Синхронизация используется для снижения части помех. Часто RS-триггеры этого типа используют для цепей с параллельным подключением, значительно снижая помехи от элементов с высокой магнитной индуктивностью.

Графическое обозначение, таблица истинности и диаграмма устойчивых состояний устройства представлена ниже.

Асинхронные и синхронные модели далеко не единственные, которые использует схемотехника для построения логических моделей работы. Далее будут представлены разновидности триггеров с иным принципом работы.

D-триггер

Эти виды простых триггеров так же используют для хранения информации о своем текущем состоянии один бит памяти. Используют его в простых электронных схемах вычислительных устройств и автоматики. Данная модель также относится к синхронному типу и имеет вход «С». Главное отличие заключается в замене 2 входов «R-S» на один контакт «D». Применение всего одного входа и наличие синхронизации позволяет значительно упростить работу устройства. Для работы D-триггера используется следующая схема:

- На контакт «С» поступает сигнал логической 1 или высокое напряжение.

- Сигнал проходит синхронизацию.

- Поступает на контакт входа D.

- Если выход «Q» находился в состоянии логической 1, то он включается.

- Если на выходе «Q» находился логический 0 или этот контакт находился в состоянии сброса, логическая 1 передается на выход «Q−».

Иными словами, состояние триггера на выходе зависит от его предыдущего положения. Если предыдущее положение было в состоянии высокого напряжения, то на этот выход поступит логическая 1. Если положение было в состоянии сброса, то логический 0.

Практически все D-триггеры являются динамическими. При динамическом управлении состоянием триггера используется понятие фронта. Фронтом называют переход от 1 к 0. Подразумевается 2 вида фронта:

- Передний. При этом положении осуществляется переход от 0-1.

- Задним фронтом является переход сигнала от 1 к 0.

Существуют разновидности D устройств с дополнительным входом V. Название этого входа расшифровывается как проверочный. Работает такой элемент с неким замедлением. Оно необходимо для предварительной синхронизации сигнала, с его последующим подтверждением. При этом не играет особой роли, сколько памяти занято в устройстве. Обычные и DV-триггеры предназначены для работы в сложных устройствах с множеством ячеек. Например, в электронных счетчиках эти устройства отвечают его за актуальное значение. При его смене состояние триггера изменяет свой фронт.

Далее приведена таблица истинности и УГО фронтов.

Т-триггер

Триггеры типа T на логических элементах включают в себя многие возможности ранее описанных устройств. Есть модели асинхронного и синхронного типа, динамические и с дополнительным подтверждающим входом.

Асинхронные

При получении положительного сигнала на вход, на выходе получается напряжение в 2 раза выше входного. Такой эффект возможен только при импульсном сигнале, поступающем на T вход. При этом частота поступления по временной шкале не имеет препятствий, а значит сигнал доходит гораздо быстрее. Асинхронные T устройства в состоянии логической 1 на выходе имеют противофазу инверсного выхода.

Синхронные

Эти T-триггеры подобны асинхронным. Исключение состоит в наличие тактового сигнала на входе. Также существует противофаза на инверсном выходе и появление удвоенного напряжения.

Устройство T элементов можно легко отнести к делителям импульсных сигналов. Эти элементы работают только при наличии переднего фронта. Иными словами, осуществляется переход от 0 к 1. Но разница заключается в учете временного интервала между импульсами.

Триггеры типа T часто используются в логических вычислительных процессах. Осуществляется это за счет функции увеличения или снижения напряжения:

- При увеличении частоты на выходе с логической 1, осуществляется запись положительного числа.

- При уменьшении частоты на инверсном выходе при логическом 0, осуществляется запись отрицательного числа.

При учете, сколько памяти необходимо для перехода и деления сигнала, элемент может быть дополнен входом подтверждения. Программирование с использованием T-триггера допускает использование устройства в различных электронных счетчиках без встроенной памяти. Далее дана диаграмма работы устройства.

JK-триггер

Является самым универсальным электронным элементом. В этих устройствах присутствуют:

JK устройство работает по принципу перехода из одного состояния в другое, но с учетом единицы времени. Также существует разность при подаче сигнала на вход синхронизации. Иными словами, если на оба входа JK подать логическую 1, то на его выходах появится прямо противоположное значение. Но при этом устройство не воспримет наличие двух 1 единиц как ошибку.

В зависимости от назначения, в данном триггере может использоваться так называемый фронт (передний или задний). В этом случае устройство считается синхронным, а его состояние определяется актуальным положением логических чисел. При расчете рабочего состояния элемента также учитывается возможность одновременного использования устройства в качестве T или D триггера. В этом случае учитывается параметр временного интервала поступления сигнала, какое напряжение будет получено при выходе и устойчивость состояния элемента. Информатика часто использует этот элемент в качестве универсального устройства контроля состояния устойчивой работы простых логических функций. Далее дана диаграмма работы устройства.

Симметричный

Симметричный триггер относится к особому виду элементов. Он создается на транзисторах и является усилителем постоянного тока двухкаскадного типа. Работает устройство за счет использования транзисторов с полностью идентичными параметрами.

Принцип работы следующий:

- При подаче напряжения на устройство, транзистор VT1 считается открытым. Напряжение его коллектора равняется 0.

- В этот момент транзистор VT2 закрыт. Его коллектор имеет положительное напряжение.

- Для осуществления перехода из одного состояния в другое используется импульс напряжение. Этот импульс создается конденсатором.

- При появлении импульса транзисторы меняют свое состояние.

При смене положения транзисторов создается перепад напряжения, и оно значительно снижается.

В схемах симметричных триггеров основным элементом является система запуска. Она может отличаться по способу управления и месту, с которого поступил пусковой импульс.

- Раздельное управление. Предполагает подачу напряжения на определенный вход триггера. При таком управлении элемент считается RS-триггером.

- Общее или счетное управление. Напряжение подается на общий входной контакт. При таком подключении, устройство схоже по параметрам с Т-триггером.

Место поступления импульса может быть от коллектора или базы транзистора. При таких схемах подключения существует вероятность появления ложного или вторичного сигнала. Он отсекается путем подключения диода.

Основным недостатком симметричных элементов является полная зависимость от времени поступления импульсного сигнала и его длительности. Если длительность недостаточная, импульс не успеет открыть транзистор, а значит не произойдет закрытие второго транзистора.

Такие устройства используются в устройствах учета импульсов, генераторах частоты, переключателях радиоэлектронных цепей.

Заключение

С триггерами в жизни мы сталкиваемся довольно часто, ведь они широко используются в различных сферах. В данной статье было приведено описание и области использования различных разновидностей данного устройства. При ремонте электронного оборудования важно знать: для чего нужен этот элемент, где он используется и по какому принципу работают такие устройства.

То, что компьютеры могут хранить информацию в памяти, мы давно принимаем за данность, но знаешь ли ты, как именно эта память работает? В этой статье мы поговорим о последовательностной логике, которая позволяет компьютерам хранить информацию. Какие возможности это открывает и реально ли узнать секретный ключ кодового замка, располагая только его схемой — самое время это выяснить!

В начале был Бит

Пару месяцев назад мы приступили к изучению цифровой схемотехники с базового блока NOT . Не будем изменять традиции и в этот раз, тем более, что блок на самом деле не так прост, как кажется на первый взгляд. Возьмем парочку и соединим их последовательно.

Кто-то может сказать, что это совершенно бессмысленная схема, ведь сигнал на выходе всегда равен входу. Действительно, применяя логическое отрицание дважды, мы получаем исходное утверждение. Если ты не «белый» хакер, ты «черный». Не «не белый» — по-прежнему «белый». Это выглядит как бесполезная словесная эквилибристика, но все меняется, если в схеме выше попробовать вход замкнуть на выход.

Теперь, если в правой половине у нас высокий логический уровень, в левой половине всегда будет низкий (и наоборот). Иначе говоря, схема приобретает свойство бистабильности и принимает лишь одно из двух возможных состояний. Совсем как бит памяти — или переменная bool в С/С++.

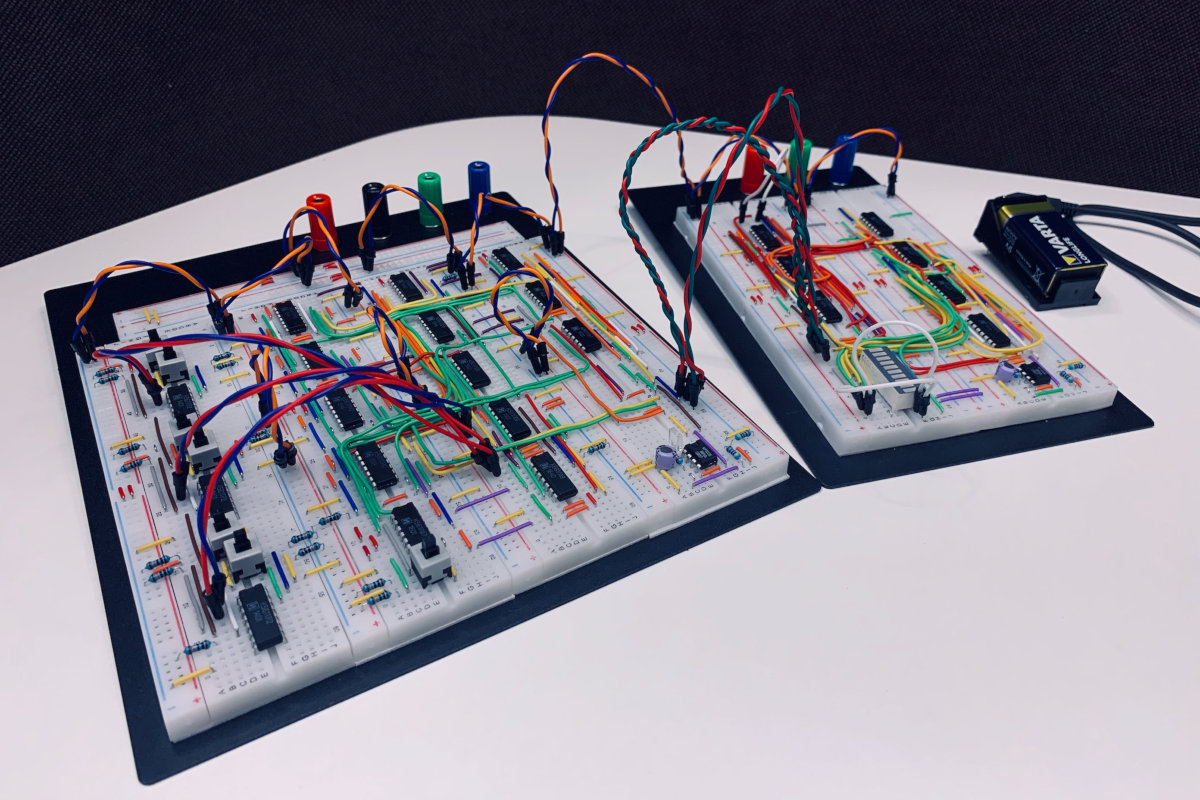

Для наглядности можно собрать схему на макетной плате. Здесь подойдет любой интвертор — например, 74HC04B. Это шесть логических вентилей NOT в корпусе DIP-14 (целых три бита информации, Карл!). Впрочем, как ты уже понимаешь, одну и ту же функцию можно реализовать несколькими способами, поэтому здесь наш выбор практически неограничен.

Тут стоит упомянуть, что с теми же целями мы можем использовать и 74HC00N (четыре элемента NAND ). Эта микросхема получила свой особый «нулевой» номер в серии 74хх не просто так — логическая операция ИЛИ-НЕ обладает замечательным свойством функциональной полноты. Иными словами, мы можем любой другой базовый блок ( AND , OR и остальные) разложить на комбинацию блоков NAND . Аналог в отечественной микроэлектронике — 155ЛА3 и это настолько популярная микросхема у радиолюбителей, что в ее честь даже называют сайты.

Простой пример (как на картинке выше) позволяет на практике убедиться, что микросхема работает, как мы предполагали. Для мигания светодиодами и переключения состояний в такой ячейке памяти достаточно прикасаться концами проводов (от земли или питания) к соответствующим выводам микросхемы. Возможно, само по себе это звучит и не очень увлекательно, но некоторое размышление в процессе должно навести на интересные идеи.

Некоторая неопределенность

В какой-то момент твой пытливый хакерский ум наверняка задался вопросом — а что если подать одно и то же напряжение на обе половинки одновременно? И в каком состоянии окажется наша схема после? В сущности, это сродни делению на ноль в математике (или программировании) — запрещенная операция, результат на выходе которой не определен. Парадоксально, но даже такое свойство может иметь практическое применение! Инженеры в Intel хорошо знают схемотехнику (кто бы сомневался) и встроенный в их процессоры генератор случайных чисел работает именно по такому принципу.

Сейчас процесс работы нашей схемы напоминает электромеханические компьютеры середины 40-х годов XX века, когда коммутация сигналов внутри устройства происходила с помощью реле и переключателей. Самое время добавить новые возможности и перейти от инверторов к элементам с несколькими входами.

Простой RS-триггер

Внесем минимальные изменения в нашу схему и воспользуемся дополнительными входами NAND . Назовем их nR и nS ( not RESET и not SET соответственно, их назначение прояснится в дальнейшем).

Оба входа могут принимать по два значения, итого предстоит разобрать четыре варианта. Начнем с базового случая nR = 1 и nS = 1 . При этом на выходах Q и nQ уже есть какие-то значения. Обрати внимание, что если Q = 1 , то при nS = 1 результатом операции NAND будет низкий уровень, то есть nQ = 0 . И наоборот, если Q = 0 , то nQ = 1 и оба выхода в нашей схеме действительно принимают противоположные значения. Другими словами, если один из входов вентиля NAND находится в состоянии логической единицы, то сигнал на выходе определяется как инверсия второго входа — в точности как с инверторами чуть ранее! Таким образом, при nR = 1 и nS = 1 схема сохраняет свое старое состояние и выходы не обновляются.

Теперь рассмотрим вариант с nR = 1 и nS = 0 . Так как на входе верхнего элемента NAND точно есть хотя бы один ноль, то его выход в любом случае будет равен логической единице. Значит, Q = 1 и, следовательно, nQ = 0 . Аналогично, при nR = 0 и nS = 1 мы можем схожим образом вывести, что состояние схемы будет полностью противоположным ( Q = 0 и nQ = 1 ).

Остается разобрать заключительный вариант, где оба входа равны нулю одновременно. На интуитивном уровне можно уже предполагать, что тут что-то не так. Действительно, при nR = nS = 0 результат элемента NAND не может быть положительным ни при каких возможных значениях дополнительного входа (рекомендую проверить по таблице истинности). Следовательно, Q = nQ = 0 и это единственный случай, когда наша схема «сбоит». В дальнейшим мы ее лучшим и обязательно избавимся от этого недостатка.

Но сейчас самое время остановиться и перевести дух. Выше были не самые тривиальные рассуждения и если ты чего-то не понял, то это совершенно нормально. Последовательностные схемы сложнее для восприятия и именно поэтому в предыдущей статье мы начали знакомство именно с комбинационной логики.

Поэтому советую перечитать несколько абзацев выше еще раз. Тем более, что это ключевая схема и далее в статье многие элементы будут основаны именно на ней. А вообще, самый правильный способ разобраться в любой схеме раз и навсегда — это взять ручку и листочек бумаги (или стилус и планшет) и последовательно рассмотреть каждый из возможных вариантов. Я сужу по личному опыту — в твоем случае может сработать что-то еще.

Практическое применение

Надеюсь, теперь принцип работы RS-триггера для тебя больше не секрет и тебе уже не терпится применить полученные знания на практике. Для этого понадобится микросхема IW4011, которая содержит четыре вентиля NAND (подойдет и любой зарубежный аналог).

Серия микросхем 4000 — это еще один прекрасный набор «строительных кирпичиков», которые раньше широко использовались при разработке устройств. В отличии от уже упоминавшегося семейства 7400, эти компоненты работают с расширенным диапазоном входных напряжений (до 15 Вольт). Следует помнить, что, хотя обе серии реализуют более-менее одинаковый набор логических схем, совместимость по выводам не гарантируется.

Наверняка ты уже знаком с таким неприятным явлением в электронике, как дребезг контактов. Он проявляется всякий раз, когда участки цепи коммутируются механически: при нажатии тактовой кнопки, переключении тумблера, реле и во многих других случаях. Как правило, с дребезгом предпочитают бороться программным способом: кратковременные изменения в сигнале (момент соприкосновения контактов) просто игнорируются устройством.

Это распространенный и достаточно эффективный способ: реализацию подобной функции можно найти и в Arduino (библиотека Bounce2). Однако у такого метода есть и свои минусы: обработку сигнала приходится задерживать на какое-то время (порядка нескольких десятков миллисекунд). Во многих случаях это не становится большой проблемой.

Но что, если нажатие на кнопку обрабатывается в прерывании? Или мы проектируем клавиатуру для геймеров и хотим получить минимальное время отклика? Да, «лишние» миллисекунды конечно не выведут тебя на первые строчки в ладдерах популярных игр, но некоторое преимущество точно обеспечат. Попробуем применить здесь RS-триггер и нарисуем такую схему.

Мы используем два вентиля NAND , то есть только «половину» микросхемы CD4011 (К561ЛА7). Обрати внимание, это не стандартная тактовая кнопка: тут работает перекидной контакт без фиксации, так что в каждый момент времени коммутируются ровно два вывода. Приятная особенность таких кнопок в том, что при нажатии они издают слабый щелчок, похожий на звук переключателей в механической клавиатуре.

Аппаратные решения хороши своей простотой и безотказностью — программа может зависнуть или исчерпать доступную память, тогда как с триггерами таких проблем нет.

Продвинутый D-триггер

Освоившись с установкой и сбросом внутреннего состояния в простой схеме, перейдем к более интересным вещам. Как и в программировании, теперь мы можем повторно использовать готовые логические блоки, чтобы эффективно абстрагироваться от возрастающей сложности устройств. Это примерно как с кодом — единожды реализовав нужную функцию или алгоритм, ты можешь добавлять их в необходимые места, не заботясь о стеке вызовов и конкретных адресах в памяти.

Как ты помнишь, ключевое неудобство в RS-триггере вызывал тот факт, что при nR = nS = 0 мы получали одинаковое состояние на прямом ( Q ) и, казалось бы, инверсном ( nQ ) выходе. Попробуем избавиться от этой проблемы. Для этого будем явно блокировать один из сигналов, если другой в этот момент активен.

Теперь состояние входа данных ( D ) через пару вентилей NAND подается на оба входа RS-триггера, а сигнал разрешения ( E ) контролирует момент времени, когда состояние правой половины схемы может меняться.

D-защелка — это почти как D-мейл, только защелка

Можно пойти еще дальше и объединить две защелки в один триггер, который будет срабатывать только по переднему фронту тактового сигнала (переход с низкого уровня в высокий). Это наиболее универсальная схема, так как позволяет мгновенно зафиксировать состояние всех сигналов на входных линиях, а уже потом приступить к формированию результата с помощью комбинационной логики.

Практическое применение

В 4000 серии пару D-триггеров реализует микросхема CD4013 (отечественный аналог — К561ТМ2). Назначение ее выводов ты можешь увидеть на схеме ниже. Обрати внимание, что, помимо входов данных и тактового сигнала, тут выведены контакты для асинхронного сброса и установки внутреннего состояния триггера.

Асинхронность означает, что событие происходит мгновенно, не дожидаясь следующего тактового сигнала. И наоборот, обновления с линии данных происходят синхронно с изменениями на линии CLK .

Таким образом, комбинируя микросхемы CD4011 (561ЛА7) и CD4013 (561ТМ2) можно собрать схему с тактовой кнопкой и светодиодом, которая будет помнить свое состояние. Первое нажатие заставит светодиод гореть, второе нажатие его погасит. При этом нам даже не потребуется микроконтроллер и мы не напишем ни строчки кода!

Кодовый замок на регистрах

Теперь пришло время для более серьезных вещей. Я собрал на макетной плате кодовый замок на микросхемах 561 серии. Часть из них ты уже знаешь, другую часть мы разберем в процессе.

Для удобства я сразу приведу принципиальную схему. Впрочем, ее всегда можно восстановить самостоятельно

Обрати внимание, что первая группа D-триггеров связана последовательно: инверсный выход через вентиль NAND блокирует тактовый сигнал следующего. Таким образом, пока не будет верно подобрана первая цифра ключа, остальная схема не будет реагировать на нажатия. Кроме того, на этот же вентиль подается инверсный выход самого триггера, так что как только нужная кнопка будет нажата в первый раз, блок отключается и далее внутреннее состояние D-триггера уже не меняется.

Отдельного рассмотрения заслуживает пара D-триггеров U3A и U6A . У них общий тактовый сигнал, а вход данных второго зависит от выхода первого. Так как изначально все триггеры сброшены в ноль, то даже после однократного нажатия нужной кнопки выход второго не изменится и последний из триггеров будет все также заблокирован (иными словами, ноль из U3A перекочует в U6A , но глобально это ничего не меняет).

Однако, первый регистр из пары все-таки поменяет свое состояние, так как по приходу тактового сигнала на его входе данных содержится логическая единица от инверсного выхода второго. Значит, на его выходе уже будет высокий уровень и нам потребуется еще один тактовый сигнал (нажатие на кнопку), чтобы протолкнуть «единичку» во второй регистр. Таким образом, можно сделать вывод, что одну из кнопок требуется нажать два раза подряд, после чего разблокируется последний D-триггер.

Кстати, трехвходовые вентили NAND для разрешения подачи тактового сигнала на D-триггер содержатся в микросхемах К561ЛА9 (по три штучки на корпус).

Разумеется, если взять такую схему отдельно, в ней будет существенный изъян: можно подобрать ключ, просто перебирая все кнопки одна за другой. В какой-то момент времени мы угадаем первую верную цифру, после чего перейдем ко второй, третьей и так далее.

Поэтому нам нужна возможность сброса состояния всех D-триггеров, как только превышено разрешенное количество попыток. Для этого требуется в первую очередь организовать подсчет, регистрируя нажатие любой цифры. Поэтому я взял парочку четырехвходовых вентилей NOR (К561ЛЕ6).

Логический ноль на их выходе образуется всякий раз, когда нажата какая-либо из подключенных кнопок. Объединим выходы вентилей с помощью операции И-НЕ. При этом сработает такое правило: инвертор на выходе логического элемента можно переместить на все его входы, но при этом поменяется и сам тип элемента ( NOR переходит в NAND и наоборот). Таким образом, NAND на выходе можно рассматривать как NOR , а инверторы на его входах оказываются рядом с инверторами на выходах блоков NOR и взаимно аннигилируют. В результате мы получаем один большой элемент OR , что и требовалось для нашего счетчика.

Кстати, схема самого счетчика выглядит так.

Он построен на базе трех D-триггеров, так что у нас три бита и восемь возможных состояний. Инверсный выход первого блока подается на вход, так что по восходящему фронту тактового сигнала BIT0 внутреннего состояния переходит из ноля в единичку (и наоборот). При этом выход соединен с CLK следующего и каждое второе переключение приводит к изменением для BIT1 .

Далее нам остается только отслеживать комбинацию 101 для пяти разрешенных попыток и подать сигнал сброса, если последний из D-триггеров, хранящих наш секретный код, все еще не оказался в состоянии логической единицы (случай правильной комбинации).

Работу всей схемы можно посмотреть на видео. Успешный код активирует таймер на микросхеме КР1006ВИ1, которая демонстрирует анимацию на светодиодной шкале.

Читайте также: