Что такое уу в компьютере

Обновлено: 04.07.2024

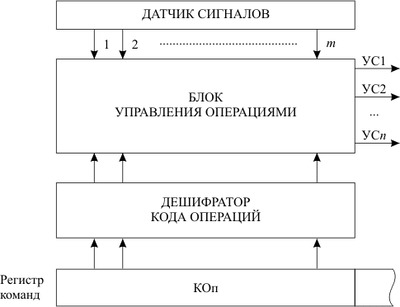

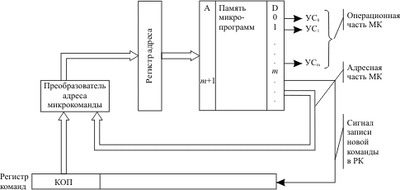

Устройство управления (УУ) предназначено для выработки управляющих сигналов, под воздействием которых происходит преобразование информации в арифметико-логическом устройстве, а также операции по записи и чтению информации в/из запоминающего устройства. Упрощенная структурная схема устройства управления (УУ) показана на рис.24.

Рис. 24 Структурная схема УУ

Основные функции УУ:

1. Формирование адреса инструкции.

2. Считывание инструкции из ОЗУ (ПЗУ) и ее хранение во время выполнения.

3. Дешифрация кода операции.

4. Формирование управляющих сигналов.

5. Считывание из регистра команд и регистров микропроцессорной памяти отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов.

6. Выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов.

7. Запись результатов операции в память.

8. Формирования адреса следующей команды программы.

По принципу формирования и развертывания временной последовательности управляющих сигналовразличают УУ:

- аппаратного (схемного) типа, выполненным в виде управляющего автомата с жесткой логикой, в котором функции переходов и выходов реализуются набором логических элементов, а требуемое количество состояний автомата задается множеством запоминающих элементов;

- микропрограммного типа, в которых блок управления реализован как блок микропрограммного управления.

По способу построения рабочего цикла различают УУ:

- с прямым циклом,

На первом этапе производится выборка из памяти команды, а затем следуют этапы выполнения машинной операции.

- с обращенным циклом,

В первую очередь выдаются управляющие сигналы для выполнения машинной операции по коду команды, поступившей в ЦУУ на предыдущем цикле (предвыборка команд), а затем из памяти выбирается код команды, которая будет исполняться в следующем цикле.

- с совмещением во времени циклов выполнения нескольких команд (конвейером команд).

По способу синхронизацииработы ЭВМ в зависимости от числа тактов в цикле выполнения команды различают УУ:

- с постоянным числом тактов;

- с переменным числом тактов.

В микропрограмме рабочего цикла выделяют общую и специальную части. К общей части относятся микрокоманды, исполняемые в цикле любой команды: выборка команды, анализ запросов на прерывание, формирование адреса следующей команды, анализ состояния процессора. Эти микрокоманды выполняются за постоянное число тактов.

К специальной части относятся микрокоманды, по которым вырабатываются управляющие сигналы в зависимости от содержания операционной части исполняемой команды. В этом случае количество тактов будет переменным для различных команд. В современных ЭВМ с различной структурой используемых команд, число тактов зависит от формата выбираемой команды, структуры ее адресной части и длины операндов.

По общей организацииуправление может быть:

- централизованным;

- Блок управления УУ вырабатывает все УС (управляющие сигналы) микроопераций для всех команд, выполняемых процессором;

- смешанным

По принципу организации цикловразличают УУ:

-синхронного типа, в которых время цикла может быть постоянным или переменным;

-асинхронного типа, в которых продолжительность цикла определяется фактическими затратами времени на выполнение каждой операции. В этом случае необходимо вырабатывать сигналы об окончании операции;

-смешанного типа, где частично реализуются оба предыдущих принципа организации циклов.

Тема 3.8. Назначение и классификация АЛУ

АЛУ – одна из основных функциональных частей процессора, осуществляющая непосредственное преобразование информации.

Все операции, выполняемые в АЛУ, можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики над числами, представленными в двоично-десятичном коде;

- операции адресной арифметики (при модификации адресов команд);

- операции специальной арифметики (нормализация, сдвиг);

- операции над алфавитно-цифровыми полями.

Для выполнения перечисленных операций в АЛУ включают следующие функциональные узлы:

- сумматор (для выполнения суммирования и других действий над кодами операндов);

- регистры (для хранения кодов операндов на время выполнения действия над ними);

- сдвигатели (для сдвига кода на один или несколько разрядов вправо или влево);

- преобразователи (для преобразования прямого кода числа в обратный или дополнительный);

- комбинационные схемы (для реализации логических операций, мультиплексирования данных, управляемой передачи информации, формирования признаков результата).

Регистры и в некоторых случаях сумматоры имеют цепи управления приемом, выдачей и сбросом кодов операндов. Логические операции, операции сдвига и преобразования кодов могут выполняться не только специальными устройствами, но и с помощью дополнительных связей регистров и сумматора.

Рис.25 Структурная схема АЛУ

Обобщенная структурная схема АЛУ (рис. 25) включает:

- блок регистров (БР) для приема и размещения операндов и результатов;

- операционный блок, в котором осуществляется преобразование операндов в соответствии с реализуемыми алгоритмами;

- схемы контроля, обеспечивающие непрерывный оперативный контроль и диагностирование ошибок;

- блок управления (БУ), в котором после приема кода операции (КОП) из центрального устройства управления формируются управляющие сигналы (УС), координирующие взаимодействие всех узлов АЛУ между собой и с другими блоками процессора.

Блок регистров (БР) связан с РОН центрального процессора и кэш-памятью данных.

Иногда АЛУ не содержит своего БР, в этом случае операционный блок непосредственно работает с регистрами общего назначения процессора. Для оперативного управления выполнением операции в ОБ на разных этапах анализируется преобразуемая информация и формируются сигналы признаков (флаги), которые используются в БУ для выработки и посылки в процессор сигнала признака результата (ПРез).

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

3–5 декабря, Онлайн, Беcплатно

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные: move , input , outptut , load и store .

- Команды перехода: goto , if . goto , call и return .

- Команда останова: halt .

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

- LOAD_A 8 . Это команда сохраняет в ОЗУ данные, скажем, <1100 1000> . Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкцию load_A — поместить данные 1000 (последние 4 бита команды) в регистр A .

- LOAD_B 2 . Ситуация, аналогичная прошлой. Здесь помещается число 2 ( 0010 ) в регистр B .

- ADD B A . Команда суммирует два числа (точнее прибавляет значение регистра B в регистр A ). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистр A .

- STORE_A 23 . Сохраняем значение регистра A в ячейку памяти с адресом 23 .

Вот такие операции нужны, чтобы сложить два числа.

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Одним из важнейших устройств компьютера является центральный процессор (CPU — англ, central processing unit, что переводится как «центральное вычислительное устройство»). Именно от типа процессора и его характеристик в первую очередь зависит производительность компьютерной системы в целом.

Центральный процессор — это устройство компьютера, предназначенное для выполнения арифметических и логических операций над данными, а также координации работы всех устройств компьютера.

Современные центральные процессоры для персональных компьютеров выполняются в виде отдельных микросхем и называются микропроцессорами. В дальнейшем будем считать понятия «микропроцессор» и «процессор» равнозначными.

Схема состава микропроцессора показана на рисунке 1.

Основным элементом микропроцессора является ядро, от которого зависит большинство характеристик самого процессора. Ядро представляет собой часть микропроцессора, содержащую его основные функциональные блоки и осуществляющую выполнение одного потока команд.

Современные процессоры могут иметь более одного ядра, т.е. могут быть многоядерными. Многоядерные процессоры способны выполнять одновременно несколько потоков команд. Основная причина перехода к многоядерным процессорам была вызвана тем, что повышение производительности микропроцессоров путем дальнейшего наращивания тактовой частоты достигло физического предела в связи с очень высоким уровнем тепловыделения и энергопотребления. Производительность многоядерного процессора увеличивается за счет распараллеливания обработки данных между несколькими ядрами. Визуальное представление процессора показано на рисунке 2.

Ядро процессора помещается в корпус (пластмассовый или керамический) и соединяется проводками с металлическими ножками (выводами), с помощью которых процессор присоединяется к системной плате компьютера. Количество выводов и их расположение определяют тип процессорного интерфейса (разъема). Каждая системная плата ориентирована на один определенный тип разъема

Арифметико-логическое устройство (АЛУ) выполняет все математические и логические операции.

Управляющее устройство (УУ) обеспечивает выполнение процессором последовательности команд программы.

Набор регистров — ячейки памяти внутри процессора, используемые для размещения команд программы и обрабатываемых данных.

Кэш-память (кэш) — сверхбыстрая память, хранящая содержимое наиболее часто используемых ячеек оперативной памяти, а также части программы, к которым процессор обратится с наибольшей долей вероятности. Процессор в первую очередь пытается найти нужные данные именно в кэш-памяти, а если их там не оказывается, обращается к более медленной оперативной памяти. Кэш-память делится на два или три уровня, которые обозначаются LI, L2 и L3 (чаще всего уровней два).

Сопроцессор — элемент процессора, выполняющий действия над числами с плавающей запятой.

Характеристики микропроцессора Тактовая частота. Для каждой выполняемой процессором команды требуется строго определенное количество единиц времени (тактов). Тактовые импульсы формируются генератором тактовой частоты, установленным на системной плате. Чем чаще они генерируются, тем больше команд процессор выполняет за единицу времени, т. е. тем выше его быстродействие. Тактовая частота обычно выражается в мегагерцах. 1 МГц равен 1 миллиону тактов в секунду. Первые модели процессоров Intel ( i 8008 x ) работали с тактовыми частотами, меньшими 5 МГц. Сегодня тактовая частота последних процессоров превышает 3 ГГц (1 ГГц = 1000 МГц). Внутренняя архитектура процессора, как и тактовая частота, также влияет на работу процессора, поэтому два CPU с одинаковой тактовой частотой не обязательно будут тратить одинаковое время на выполнение одной команды. Если, например, микропроцессору Intel 80286 требовалось 20 тактов, чтобы выполнить команду умножения двух чисел, то Intel 80486 или старше мог выполнить это же действие за один такт. Некоторые процессоры способны выполнять более одной команды за 1 такт. Их называют суперскалярными. Различают внутреннюю и внешнюю тактовую частоту. Внешняя тактовая частота — это частота, с которой процессор обменивается данными с оперативной памятью компьютера. Как уже было сказано выше, она формируется генератором тактовых импульсов (кварцевым резонатором).

Внутренняя тактовая частота — это частота, с которой происходит работа внутри процессора. Именно это значение указывается в прайс-листах фирм, продающих процессоры.

Компьютер условно можно разделить на два основных блока: операционный и управляющий. Для реализации любой команды необходимо на соответствующие управляющие входы любого устройства компьютера подать определенным образом распределенную во времени последовательность управляющих сигналов. Часть цифрового вычислительного устройства, предназначенная для выработки этой последовательности, называется устройством управления .

Любое действие, выполняемое в операционном блоке, описывается некоторой микропрограммой и реализуется за один или несколько тактов. Элементарная функциональная операция, выполняемая за один тактовый интервал и приводимая в действие управляющим сигналом, называется микрооперацией. Например, в спроектированном АЛУ для умножения чисел в первом такте выполняются следующие микрооперации: TX=0, TY=0, RGX=|X|, RGY=|Y|, RGZ=0. Совокупность микроопераций, выполняемых в одном такте, называется микрокомандой (МК). Если все такты должны иметь одну и ту же длину, а именно это имеет место при работе компьютера, то она устанавливается по самой продолжительной микрооперации. Микрокоманды, предназначенные для выполнения некоторой функционально законченной последовательности действий, образуют микропрограмму . Например, микропрограмму образует набор микрокоманд для выполнения команды умножения.

Устройство управления предназначено для выработки управляющих сигналов, под воздействием которых происходит преобразование информации в арифметико-логическом устройстве, а также операции по записи и чтению информации в/из запоминающего устройства.

Устройства управления делятся на:

- УУ с жесткой, или схемной логикой и

- УУ с программируемой логикой ( микропрограммные УУ ).

В устройствах управления первого типа для каждой команды, задаваемой кодом операции, строится набор комбинационных схем, которые в нужных тактах вырабатывают необходимые управляющие сигналы.

В микропрограммных УУ каждой команде ставится в соответствие совокупность хранимых в специальной памяти слов - микрокоманд. Каждая из микрокоманд содержит информацию о микрооперациях, подлежащих выполнению в данном такте, и указание, какое слово должно быть выбрано из памяти в следующем такте.

Схемное устройство управления

Устройство управления схемного типа (рис. 1) состоит из:

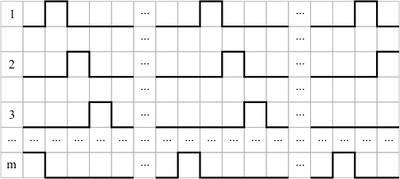

- датчика сигналов, вырабатывающего последовательность импульсов, равномерно распределенную во времени по своим шинам ( рис. 2) ( n - общее количество управляющих сигналов, необходимых для выполнения любой операции; m - количество тактов, за которое выполняется самая длинная операция);

- блока управления операциями, осуществляющего выработку управляющих сигналов, то есть коммутацию сигналов, поступающих с ДС, в соответствующем такте на нужную управляющую шину;

- дешифратора кода операций, который дешифрирует код операции команды, присутствующей в данный момент в регистре команд, и возбуждает одну шину, соответствующую данной операции; этот сигнал используется блоком управления операциями для выработки нужной последовательности управляющих сигналов.

Рис. 1. Функциональная схема схемного устройства управления

Рис. 2. Временная диаграмма работы датчика сигналов

Датчик сигналов обычно реализуется на основе счетчика с дешифратором или на сдвиговом регистре.

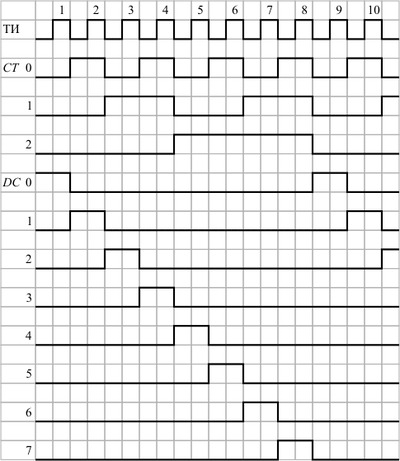

Датчик сигналов на основе счетчика с дешифратором

Реализация датчика сигналов на основе счетчика с дешифратором представлена на рис. 3. По заднему фронту каждого тактового импульса, поступающего на устройство управления с системного генератора импульсов, счетчик увеличивает свое состояние; выходы счетчика соединены со входами дешифратора, выходы которого и являются выходами датчика сигналов (рис. 4).

Рис. 3. Схема датчика сигналов на основе счетчика с дешифратором

Рис. 4. Временная диаграмма работы датчика сигналов на основе счетчика с дешифратором

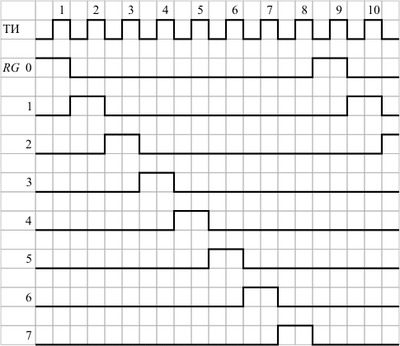

Датчик сигналов на сдвиговом регистре

Рис. 5. Схема датчика сигналов на основе регистра сдвига

Временная диаграмма работы этой схемы приведена на рис. 6.

Рис. 6. Временная диаграмма работы датчика сигналов на основе регистра сдвига

Наиболее сложной частью схемного устройства управления является блок управления операциями. Он представляет собой нерегулярную схему, структура которой определяется системой команд и составом оборудования процессора. Такое УУ может быть реализовано в виде специализированной интегральной схемы.

Структурная схема микропрограммного устройства управления

Микропрограммное устройство управления представлено на рис. 7. Преобразователь адреса микрокоманды преобразует код операции команды, присутствующей в данный момент в регистре команд, в начальный адрес микропрограммы, реализующей данную операцию, а также определяет адрес следующей микрокоманды выполняемой микропрограммы по значению адресной части текущей микрокоманды.

Рис. 7. Функциональная схема микропрограммного устройства управления (УСi - управляющие сигналы, вырабатываемые устройством управления)

На табл 1 приведен пример микропрограммы для выполнения операции умножения чисел в дополнительном коде. Предполагается, что начальный адрес микропрограммы равен 300, количество разрядов множителя равно 2, а адресная часть микрокоманды содержит адрес микрокоманды, которая должна быть выбрана в следующем такте. В последней микрокоманде в регистр команд загрузится очередная команда, код операции которой определит начальный адрес очередной микропрограммы. В реальных микропрограммных устройствах управления формирование адреса следующей микрокоманды проводится более сложным образом, учитывающим возможности ветвлений и циклического повторения отдельных фрагментов микропрограмм.

| Адрес МК | УС1 | УС2 | УС3 | УС4 | УС5 | УС6 | Сигнал записи в РК | Адрес следующей МК |

| 300 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 301 |

| 301 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 302 |

| 302 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 303 |

| 303 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 304 |

| 304 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | Х |

Из анализа структуры и принципов работы схемного и микропрограммного устройств управления видно, что УУ первого типа имеют сложную нерегулярную структуру, которая требует специальной разработки для каждой системы команд и должна практически полностью перерабатываться при любых модификациях системы команд. В то же время оно имеет достаточно высокое быстродействие, определяемое быстродействием используемого элементного базиса.

Устройство управления, реализованное по микропрограммному принципу, может легко настраиваться на возможные изменения в операционной части ЭВМ. При этом настройка во многом сводится лишь к замене микропрограммной памяти. Однако УУ этого типа обладают худшими временными показателями по сравнению с устройствами управления на жесткой логике.

Компьютер условно можно разделить на два основных блока: операционный и управляющий. Для реализации любой команды необходимо на соответствующие управляющие входы любого устройства компьютера подать определенным образом распределенную во времени последовательность управляющих сигналов. Часть цифрового вычислительного устройства, предназначенная для выработки этой последовательности, называется устройством управления .

Любое действие, выполняемое в операционном блоке, описывается некоторой микропрограммой и реализуется за один или несколько тактов. Элементарная функциональная операция, выполняемая за один тактовый интервал и приводимая в действие управляющим сигналом, называется микрооперацией [7]. Например, в спроектированном АЛУ для умножения чисел в первом такте выполняются следующие микрооперации : TX=0 , TY=0 , RGX=|X| , RGY=|Y| , RGZ=0 . Совокупность микроопераций , выполняемых в одном такте, называется микрокомандой (МК). Если все такты должны иметь одну и ту же длину, а именно это имеет место при работе компьютера, то она устанавливается по самой продолжительной микрооперации . Микрокоманды , предназначенные для выполнения некоторой функционально законченной последовательности действий, образуют микропрограмму . Например, микропрограмму образует набор микрокоманд для выполнения команды умножения.

Устройство управления предназначено для выработки управляющих сигналов, под воздействием которых происходит преобразование информации в арифметико-логическом устройстве, а также операции по записи и чтению информации в/из запоминающего устройства.

Устройства управления делятся на:

- УУ с жесткой, или схемной логикой и

- УУ с программируемой логикой ( микропрограммные УУ ).

В устройствах управления первого типа для каждой команды, задаваемой кодом операции , строится набор комбинационных схем , которые в нужных тактах вырабатывают необходимые управляющие сигналы.

В микропрограммных УУ каждой команде ставится в соответствие совокупность хранимых в специальной памяти слов - микрокоманд . Каждая из микрокоманд содержит информацию о микрооперациях , подлежащих выполнению в данном такте, и указание, какое слово должно быть выбрано из памяти в следующем такте.

Схемное устройство управления

Устройство управления схемного типа (рис. 4.1) состоит из:

- датчика сигналов , вырабатывающего последовательность импульсов, равномерно распределенную во времени по своим шинам ( рис. 4.2) ( n - общее количество управляющих сигналов, необходимых для выполнения любой операции; m - количество тактов, за которое выполняется самая длинная операция);

- блока управления операциями, осуществляющего выработку управляющих сигналов, то есть коммутацию сигналов, поступающих с ДС, в соответствующем такте на нужную управляющую шину;

- дешифратора кода операций, который дешифрирует код операции команды, присутствующей в данный момент в регистре команд , и возбуждает одну шину, соответствующую данной операции; этот сигнал используется блоком управления операциями для выработки нужной последовательности управляющих сигналов.

Рис. 4.1. Функциональная схема схемного устройства управления

Рис. 4.2. Временная диаграмма работы датчика сигналов

Датчик сигналов обычно реализуется на основе счетчика с дешифратором или на сдвиговом регистре .

Датчик сигналов на основе счетчика с дешифратором

Реализация датчика сигналов на основе счетчика с дешифратором представлена на рис. 4.3. По заднему фронту каждого тактового импульса, поступающего на устройство управления с системного генератора импульсов , счетчик увеличивает свое состояние; выходы счетчика соединены со входами дешифратора, выходы которого и являются выходами датчика сигналов (рис. 4.4).

Читайте также: