Что такое 5 нанометровый процессор

Обновлено: 04.07.2024

Несколько фабрик пытаются вывести на рынок техпроцессы на 5 нм, однако их клиентам предстоит решить – проектировать новые чипы на текущих транзисторах, или перейти на новые, созданные в техпроцессе 3 нм.

Для перехода нужно либо расширить текущие finFET на 3 нм, либо реализовать новую технологию кольцевого затвора [gate-all-around FET, GAA FET] на 3 нм или 2 нм. GAA FET – это следующий этап эволюции по сравнению с finFET, они быстрее работают, однако эти новые транзисторы сложнее и дороже в производстве, и переход на них может оказаться слишком болезненным. С другой стороны, индустрия разрабатывает новые технологии травления, структурирования и т.д., чтобы расчистить дорогу к этим новым техпроцессам.

Даты выпуска этих GAA FET разнятся от фабрики к фабрике. Samsung и TSMC делают finFET на 7 нм, и в этом году планируют переделать finFET на 5 нм, а также выпускать чипы в диапазоне полушага от 5 нм. Такие техпроцессы позволят улучшить как скорость работы, так и энергопотребление.

Что касается 3 нм, то тут Samsung через год-два планирует перепрыгнуть на нанолистовые FET – новый тип GAA-транзистора. TSMC же планирует впервые выпустить finFET на 3 нм. Следующим этапом TSMC выпустит GAA на 3 нм или 2 нм – так считают многие аналитики и поставщики оборудования.

«TSMC ускоряет разработку finFET на 3 нм, представляющих собой ужатые версии 5 нм, — Сказал Хэндел Джонс, директор IBS. – Производство первых пробных экземпляров finFET на 3 нм TSMC начнёт в 2020-м. Промышленные выпуски продукции запланированы на 3-й квартал 2021 года, что на квартал раньше запуска техпроцесса на 3 нм от Samsung. Разработка GAA в TSMC отстаёт от Samsung на 12-18 месяцев, но агрессивная стратегия по выпуску finFET на 3 нм может скомпенсировать это отставание».

TSMC продолжает оценивать свои варианты на 3 нм, и планы ещё могут поменяться. Пока компания не комментирует ситуацию, но обещает вскоре раскрыть свои планы на 3 нм. Тем не менее, переход TSMC на 3 нм finFET – логичный шаг. Переход к новым транзисторам может неблагоприятно повлиять на клиентов. Но в конечном итоге finFET исчерпает свои возможности, поэтому у TSMC нет другого выбора, кроме как переходить на GAA.

Другие компании тоже разрабатывают передовые процессы. Intel, эпизодически участвующая в коммерческом производстве, выпускает чипы на 10 нм, изучая 7 нм в лаборатории. Тем временем SMIC делает finFET на 16 нм/12 нм, исследуя при этом в лаборатории 10 нм/7 нм.

Все передовые процессы требуют значительных финансов, и не все чипы требуют использования 3 нм или других передовых технологий. Рост цен заставляет компании исследовать другие варианты развития. Ещё один способ получить преимущества масштабирования – новые виды корпусов передовых чипов. Несколько компаний разрабатывают такие корпуса.

Рабочее напряжение различных технологий

Пришёл ли конец масштабированию?

Чипы состоят из транзисторов, контактов и их соединений. Транзисторы играют роль переключателей. Передовые чипы могут содержать до 35 млрд транзисторов.

Соединения, находящиеся на верхней части транзистора, состоят из крохотных медных проводков, проводящих электрические сигналы между транзисторами. Транзисторы и проводки соединяются промежуточным слоем middle-of-line (MOL). MOL состоит из крохотных контактов.

Масштабирование интегральных схем (ИС), их традиционный способ развития, заключается в уменьшении размеров ИС с каждым новым техпроцессом и с упаковкой их на монолитном кристалле.

Для каждого следующего процесса производители масштабируют спецификации транзисторов в 0,7 раз, что позволяет индустрии увеличивать быстродействие на 40% при том же энергопотреблении и уменьшать размер на 50%. Масштабирование чипов позволяет выпускать новые, более функциональные электронные продукты.

Формула работала, и производители чипов постепенно меняли техпроцессы. Но на рубеже 20 нм произошло изменение – традиционные плоские транзисторы выбрали весь свой ресурс. С 2011 года производители перешли на finFET, что позволило масштабировать устройства далее.

Однако finFET дороже в производстве. В результате стоимость исследований и разработок взлетела до небес. Поэтому периоды перехода от одного техпроцесса к другому увеличились с 18 до 30 и более месяцев.

Компания Intel следовала общей тенденции масштабирования в 0,7 раз. Однако начиная с 16 нм/14 нм другие производители отошли этот этой формулы, что внесло некоторую неразбериху.

В этот момент нумерация техпроцессов начала размываться и потеряла связь со спецификациями транзисторов. Сегодня эти названия– всего лишь маркетинговые термины. «Обозначение техпроцессов становится всё менее осмысленным и понятным, — сказал Сэмюэл Вон, аналитик в Gartner. – К примеру, на 5 нм или 3 нм нет ни одного геометрического размера, равного 5 или 3 нм. Кроме того, у разных производителей процессы становятся всё более разными. Для одного и того же техпроцесса эффективность чипов отличается у TSMC, Samsung и, конечно же, Intel.

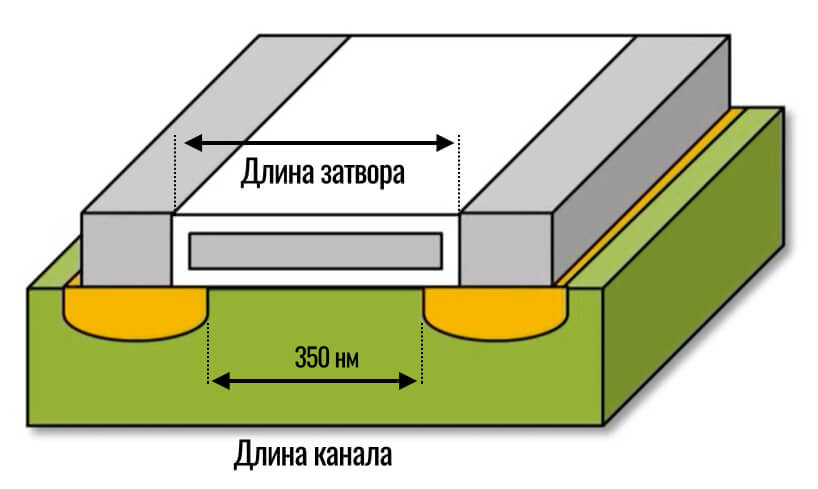

Масштабирование замедляется и у передовых техпроцессов. Для процесса на 7 нм шаг затвора транзистора [contacted poly pitch, CPP] равняется 56-57 нм с металлическим шагом в 40 нм, согласно информации компаний IC Knowledge и TEL. Для 5 нм CPP примерно равен 45-50 нм с металлическим шагом 26 нм. CPP, ключевая метрика транзисторов, обозначает расстояние между контактами истока и стока.

Кроме того, соотношение стоимости и быстродействия выглядит уже совсем не так, из-за чего многие считают, что закон Мура уже изжил себя.

»Закон Мура на самом деле лишь наблюдение, ставшее самоисполняющимся пророчеством, поддерживающим движение полупроводниковой промышленности вперёд. Экономический аспект закона Мура начал ухудшаться с ростом стоимости многократного структурирования [multiple patterning] и экстремальной ультрафиолетовой литографии (EUV), — сказал Даглас Гуереро, главный технолог из Brewer Science. – Новые архитектуры и дизайны обеспечат прирост вычислительной мощности, но это будет уже не масштабирование. Это означает, что в будущем чипы увеличат вычислительную мощность, но их стоимость не обязательно будет уменьшаться с той же скоростью, что и ранее".

Масштабирование не то, чтобы совсем прекращается. ИИ, сервера и смартфоны требуют всё более быстрых чипов и продвинутых техпроцессов. «Лет десять назад некоторые люди спрашивали: Да кому нужно ещё больше транзисторов? Некоторые считали, что в мире уже не осталось идей по поводу того, что делать с более быстрыми компьютерами, кроме совсем экзотических применений, — сказал Аки Фуджимура, директор D2S. – Сегодня для интернета вещей меньшая стоимость, достаточно хорошее быстродействие и возможности по интеграции выигрывают у простого увеличения плотности. Однако для изготовления более быстрых и экономных чипов, у которых стоимость транзисторов будет падать, требуются более быстрые транзисторы».

Очевидно, не для всего нужны передовые техпроцессы. На чипы, производимые по хорошо отлаженным техпроцессам, Есть высокий спрос. «Сюда входят ИС для работы с радиоволнами и OLED-дисплеями в смартфонах, а также ИС для управления питанием, которые используются в компьютерах и твердотельных накопителях», — сказал Джейсон Вон, один из президентов UMC.

Масштабирование finFET

В вопросе масштабирования чипов производители годами шли по одной и той же схеме, с идентичными типами транзисторов. В 2011 году Intel перешла на finFET на 22 нм, а затем на 16 нм/14 нм.

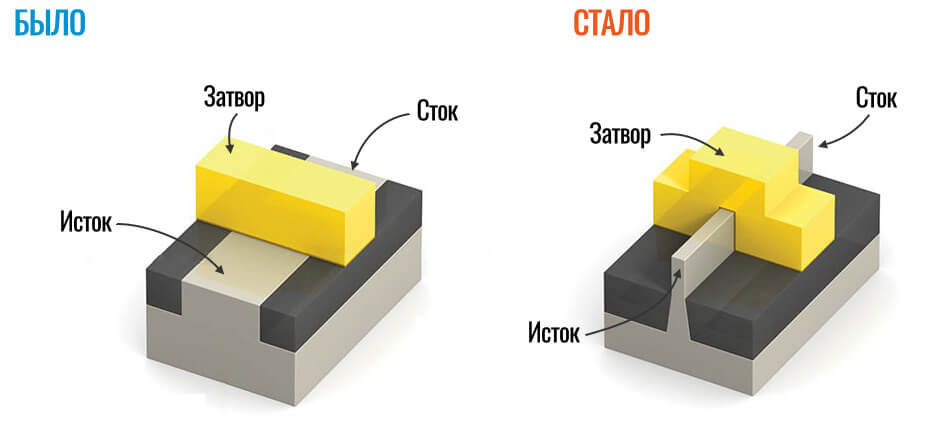

В finFET управление током осуществляется размещением вентилей на всех трёх сторонах плавника. У finFET бывает от 2 до 4 плавников. У каждого – своя определённая ширина, высота и форма.

У finFET первого поколения от Intel на 22 нм шаг плавника составлял 60 нм, а высота – 34 нм. Затем, на 14 нм шаг и высота были одинаковыми, 42 нм.

Intel сделала плавники выше и тоньше, чтобы масштабировать finFET. «Масштабирование finFET уменьшает поперечные размеры устройства, увеличивая плотность по площади, а увеличение высоты плавника улучшает быстродействие», — написала у себя в блоге Нерисса Дрэгер, директор по связи с университетами в компании Lam Research.

На техпроцессах 10 нм/7 нм изготовители чипов пошли по тому же пути масштабирования finFET. В 2018 году TSMC начала производство первых finFET на 7 нм, за ней последовала Samsung. Intel в прошлом году после нескольких задержек начала производство на 10 нм.

В 2020 году конкуренция фабрик увеличится. Samsung и TSMC подготавливают 5 нм и различные полуцелые техпроцессы. Ведутся исследования касательно 3 нм.

Все процессы стоят дорого. Стоимость проектирования чипа на 3 нм составляет $650 млн – сравните это с $436,3 млн для устройства на 5 нм и $222,3 млн для устройства на 7 нм. Это стоимость такой разработки, после которой через год технология уже уходит в производство.

По сравнению с 7 нм, finFET на 5 нм от Samsung дадут 25% увеличение логической площади, и 20% уменьшение потребления энергии или 10% увеличение скорости.

Для сравнения, finFET на 5 мм от TSMC предлагает «скорость на 15% больше при том же энергопотреблении или уменьшение энергопотребления на 30% при той же скорости, с увеличением логической плотности в 1,84 раза», — сказал Джоффри Йеп, главный директор по передовым технологиям в TSMC.

В техпроцессах на 7 нм и 5 нм производители чипов провели серьёзные изменения. Для изготовления критически важных функций в чипах, две компании перешли от традиционной литографии на 193 нм к экстремальной ультрафиолетовой литографии (EUV). EUV использует длины волн в 13,5 нм, что упрощает процесс.

Но EUV не решает всех проблем масштабирования чипов. «Решение этих задач требует множества технологий, не ограничивающихся масштабированием, включая использование новых материалов, новых типов встроенной энергонезависимой памяти и архитектур передовой логики, новых подходов к травлению, инноваций в производстве корпусов и дизайна чиплетов», — сказала Реджина Фрид, управляющий технологический директор в Applied Materials.

Тем временем, за кулисами Samsung и TSMC подготавливают свои варианты техпроцессов на 3 нм. В прошлом производители чипов шли по одному пути, но сегодня их пути расходятся.

«3 нм бывает в различных вариантах, таких, как finFET и GAA, — сказал Вон. – Это даёт возможность клиентам выбирать различные сочетания стоимости, плотности, энергопотребления и скорости, так, чтобы удовлетворить свои запросы».

Samsung обещает представить нанолистовую FET на 3 нм. TSMC тоже работает над ними, но планирует продлить использование finFET на следующее поколение. «У TSMC будет finFET на 3 нм в третьем квартале 2021 года, — сказал Джонс. – GAA от TSMC появятся в 2022-2023 годах».

Вот тут клиенты фабрик должны взвесить все за и против, касающиеся стоимости и технических компромиссов. Расширение finFET – безопасный путь. «Многие клиенты считают TSMC наименее рискованным производителем», — сказал Джонс.

Тем не менее, GAA обеспечивает некоторое увеличение быстродействия. «У GAA на 3 нм меньше пороговое напряжение, и потенциально на 15-20% меньше энергопотребление, по сравнению с finFET на 3 нм, — сказал Джонс. – Однако разница в быстродействии будет на уровне 8%, поскольку MOL и BEOL одинаковые».

Backend-of-the-line (BEOL) и MOL – узкие места в передовых чипах. Проблема MOL заключается в сопротивлении контактов.

BEOL – это этап производства, на котором происходит подсоединение проводков. Из-за их постепенного уменьшения возникают задержки, связанные с ёмкостным сопротивлением. В finFET и GAA используются разные транзисторы, но схемы их соединения в техпроцессе 3 нм, скорее всего, будут почти одинаковыми. Задержки, связанные с ёмкостным сопротивлением, будут вредить обоим типам транзисторов.

Есть и другие проблем. finFET исчерпают свои возможности, когда ширина плавника достигнет 5 нм. finFET на техпроцессах 5 нм/3 нм уже упираются в этот предел.

Кроме того, finFET на 3 нм могут состоять из одного плавника, по сравнению с двумя или большим числом плавников в других техпроцессах. «Чтобы продлить работу finFET на 3 нм, нам понадобятся особые технологии, увеличивающие мощность единственного плавника и уменьшающие паразитные явления», — сказал Наото Хоригучи, директор по КМОП в Imec.

Один из способов продлить работу finFET на 3 нм – перейти на германий для p-канала. finFET на 3 нм с каналами высокой пропускной способности помогут увеличить скорость работы чипов, однако столкнутся с определёнными проблемами с интеграцией.

Переход на нанолисты

В конечном счёте finFET перестанут масштабироваться, и производителям чипов придётся перейти на новые транзисторы, а именно на нанолистовые FET.

Нанолистовые FET начали набирать обороты в 2017-м, когда Samsung представила Multi Bridge Channel FET (MBCFET) на 3 нм. MBCFET – это нанолистовые FET. Пробные образцы начнут производить уже в этом году, а промышленный выпуск начнётся в 2022-м.

TSMC тоже работает с нанолистовыми FET, представляющими собой один из типов GAA-транзисторов. Нанолистовые FET обеспечивают небольшое преимущество для масштабирования finFET на 5 нм, но у них есть несколько преимуществ.

Нанолистовой FET – это, по сути, finFET, положенный набок, и обёрнутый затворами. Нанолист состоит из нескольких отдельных тонких горизонтальных листов, положенных друг на друга. Каждый лист – это отдельный канал.

Вокруг каждого листа находится затвор, и в результате получается кольцевой транзистор. Теоретически, нанолистовые FET дают большее быстродействие при меньших утечках, поскольку управление током осуществляется с четырёх сторон структуры.

Изначально в нанолистовых FET будет примерно по четыре листа. «Ширина типичного нанолиста составляет от 12 до 16 нм, а толщина – 5 нм», — сказал Хоригучи.

Этим нанолист отличается от finFET. Количество плавников у finFET ограничено, что стесняет работу дизайнеров. «Преимущество нанолиста в том, что у него можно менять ширину. Ширину можно подбирать по запросам дизайнера. Это даёт им некоторую свободу. Они могут обнаружить лучший вариант по соотношению энергопотребления и скорости», — сказал Хоригучи.

К примеру, у транзистора с более широким листом будет больше и ток возбуждения. Узкий лист позволяет сделать устройство меньше размером с меньшим током возбуждения.

Нанолисты связаны с технологией нанопроводов, в которой каналами служат провода. Ограничение ширины канала приводит к ограничению тока возбуждения.

Поэтому нанолистовые FET и набирают обороты. Однако у этой технологии и у finFET на 3 нм есть несколько проблем. «Проблемы finFET связаны с квантовым управлением ширины плавника и профиля плавника. Проблемы нанолистов связаны с дисбалансом p/n, эффективностью нижнего листа, прослоек между листами, управлением длиной вентиля», — сказал Джин Кай, заместитель директора TSMC, во время презентации на IEDM.

Учитывая все эти сложности, на ввод технологии нанолистовых FET уйдёт какое-то время. «У перехода на новые архитектуры транзисторов есть много препятствий, — сказал Герреро. – Определённо для этого потребуются новые материалы».

В простейшем варианте процесса изготовление нанолистового FET начинается с формирования сверхрешётки на подложке. Эпитаксиальный инструмент располагает на подложке перемежающиеся слои кремний-германиевого сплава (SiGe) и кремния. Стопка будет состоять как минимум из трёх слоёв SiGe и трёх слоёв кремния.

Затем в сверхрешётке при помощи структурирования и травления формируются вертикальные плавники, для чего требуется очень точное управление процессом.

Потом начинается один из самых сложных этапов – формирование внутренних прокладок. Во-первых, внешние части слоёв SiGe утапливаются в сверхрешётке заподлицо. Это создаёт небольшие углубления, заполняемые диэлектриком. «Внутренние прокладки нужны для уменьшения ёмкости вентиля, — сказал Кай. – Их изготовление – важнейшая часть процесса».

И такие технологии уже есть — IBM и TEL недавно описали новую технику травления, подходящую как для внутренних прокладок, так и для выпуска каналов. Для этого используется изотропное сухое травление SiGe с соотношением 150:1.

Такая технология позволяет получать очень точные внутренние прокладки. «Изготовление выемок в SiGe требует очень выборочного бокового „слепого“ травления слоёв», — сказал Николас Лубе, менеджер по R&D в IBM.

Затем формируются исток и сток. После этого слои SiGe удаляются из сверхрешётки при помощи травления. Остаются кремниевые слои, или листы, составляющие каналы.

В структуру помещаются High-k-материалы, и наконец, формируются соединения MOL, что и даёт нанолист.

Это упрощённое описание этого сложного процесса. Тем не менее, как и любые новые технологии, нанолисты могут быть подвержены появлению дефектов. Требуется дополнительное изучение и измерение всех шагов.

«Как и с предыдущими переходами между технологиями, мы видим проблемы, связанные с изучением и измерением нанолистов», — сказал Чет Ленокс, директор по решениям управлением процессами в KLA. «Может появиться много дефектных режимов как во внутренних прокладках, так и в нанолистах. Производителям ИС необходимы точные размеры отдельных нанолистов, а не просто средняя величина каждой стопки, чтобы уменьшить изменчивость своих производственных процессов».

Для этого тоже требуются новые технологии. К примеру, Imec и Applied Materials недавно представили работу по технологии «scalpel scanning spreading resistance microscopy» (s-SSRM) для создания кольцевых затворов. В технологии s-SSRM крохотный скальпель откалывает небольшую часть структуры, и в этот разрез можно добавлять легирующие примеси.

Другие варианты

В рамках R&D Imec разрабатывает более передовые виды GAA, такие, как CFET и вилочно-листовые FET (forksheet FET), нацеленные на 2 нм и меньше.

К тому времени для большинства производителей масштабирование ИС станет слишком дорогим, в особенности в свете уменьшения преимуществ по энергопотреблению и быстродействию. Поэтому всё большую популярность набирают передовые компоновки чипов. Вместо того, чтобы запихивать все функции на один кристалл, предполагается разбивать устройства на более мелкие кристаллы и интегрировать их в передовые корпуса.

«Это всё зависит от области применения, — сказал Рич Райс, старший вице-президент по бизнес-развитию ASE. – Мы определённо наблюдаем увеличение подобных попыток, даже в техпроцессах, ушедших глубоко в субмикронные размеры. Это развитие будет продолжаться и далее. Многие компании занимаются этим. Они решают, могут ли они интегрировать чипы на 5 нм, и хотят ли. Они активно ищут способы разбивания систем».

Это не так-то легко сделать. Плюс существует несколько вариантов корпусов с различными компромиссами — 2.5D, 3D-ICs, чиплеты и fan-out.

Заключение

Определённо не всем потребуются такие передовые техпроцессы. Однако Apple, HiSilicon, Intel, Samsung и Qualcomm не зря рассчитывают на передовые технологии.

Потребителям нужны самые новые и лучшие системы с увеличенным быстродействием. Вопрос лишь в том, дадут ли новые технологии какие-либо реальные преимущества по приемлемой цене.

При выборе смартфона мы все чаще обращаем внимание на такой параметр, как техпроцесс процессора. В характеристиках смартфона производитель гордо указывает величины: 8 нм, 7 нм и даже 5 нм. Но что скрывается за этими цифрами?

Что такое техпроцесс?

Apple A14 Bionic – самый мощный мобильный процессор 2020 года. Скрин: YouTube-канал Apple Apple A14 Bionic – самый мощный мобильный процессор 2020 года. Скрин: YouTube-канал AppleТехнологический процесс представляет собой широкое понятие, для определения которого необходимо разобраться с термином транзистор.

Транзистором в электронике называют минимальный компонент, который пропускает или не пропускает электрический ток. В структуре процессора транзистор играет роль своеобразного переключателя для выполнения операций в двоичной системе расчета.

Мобильный чипсет состоит из нескольких миллионов таких транзисторов, отличающихся габаритами. Размер одного элемента принято измерять в нанометрах, но величина 5 нм или 7 нм является не площадью, а шириной его канала, через который проходит ток.

Поскольку ширина канала напрямую связана с его габаритами, понятия технологического процесса и размера транзистора с натяжкой можно назвать тождественными.

В пресс-релизах техпроцессом сегодня называют размер минимального компонента процессора (транзистора).

На что влияет техпроцесс?

Транзисторы в структуре ядра процессора. Скрин: YouTube-канал stupidmadworld Транзисторы в структуре ядра процессора. Скрин: YouTube-канал stupidmadworldОт техпроцесса или, как мы уже поняли, размера транзистора зависит то, сколько таких элементов удастся расположить на чипе. Ведь площадь однокристальной системы ограничена.

Значит ли это, что чем меньше технологический процесс, тем мощнее процессор? Не совсем. На мощность процессора влияет другая характеристика – тактовая частота. Чем выше частота, тем сильнее нагревается чипсет.

Температура процессора напрямую влияет на автономность смартфона. Частично проблема «горячего» чипа решается нанесением термопасты и графитовой пленки на однокристальную систему. Но более действенным вариантом становится увеличение расстояния между транзисторами. А оно возможно только в том случае, если транзисторы обладают минимальным размером.

Таким образом, техпроцесс влияет на продолжительность работы смартфона от одного заряда наряду с таким фактором, как емкость аккумулятора.

Какой техпроцесс лучше?

Ежегодно производители однокристальных систем стараются уменьшить техпроцесс, чтобы разместить на чипе больше транзисторов и увеличить расстояние между ними.

То есть, чем меньше размер транзистора (технологический процесс), тем лучше.

В зависимости от класса устройства рекомендуется выбирать модели, чей техпроцесс соответствует следующим показателям*:

- флагман – 5-7 нм;

- средний класс – 7-8 нм;

- бюджетник – 10-12 нм.

* – информация актуальна на 2021 год.

Сегодня на российском рынке только две компании могут похвастать актуальным 5-нм техпроцессом чипсета (Samsung и Apple). К сожалению,

современный показатель все еще не доступен для моделей среднего класса и уж тем более для бюджетников. Но недавно мы делали обзор недорогого смартфона Redmi Note 9T , в котором использован чипсет с размером транзистора 7 нм. Это отличный вариант для устройства за 15000₽.

Даже в современных печатных книгах сплошь и рядом встречается распространенное заблуждение, будто эти цифры означают размеры транзисторов, из которых состоит процессор.

В общем, пришло время разобраться с этим вопросом!

Сразу предупреждаю, что статья рассчитана на самый широкий круг читателей, то есть, при желании все сказанное смогут понять даже дети.

Но прежде, чем говорить о нанометрах и техпроцессе, нужно разобраться с транзистором. Без понимания этого устройства весь наш дальнейший разговор будет лишен смысла.

Что такое транзистор в процессоре смартфона? Как он работает и зачем вообще нужен?

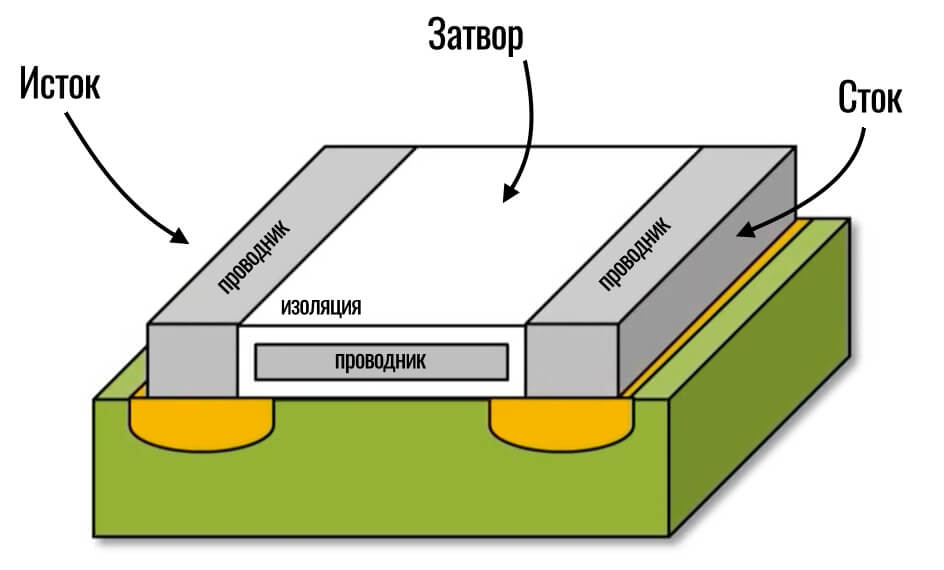

Итак, для создания транзистора мы берем немножко песка (условно какую-то часть одной песчинки) и делаем из него микроскопическую основу:

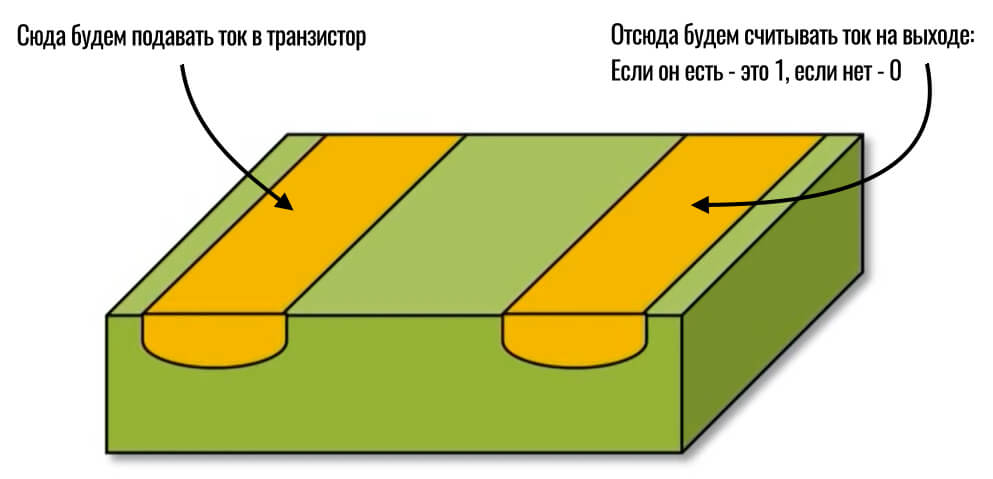

Это будет наша кремниевая подложка (кремний получают именно из песка). Теперь нужно на эту основу нанести две области. Я думал, стоит ли погружаться в физику этого процесса и объяснять, как эти области делаются и что там происходит на уровне электронов, но решил не перегружать статью излишней информацией. Поэтому будем немножко абстрагироваться.

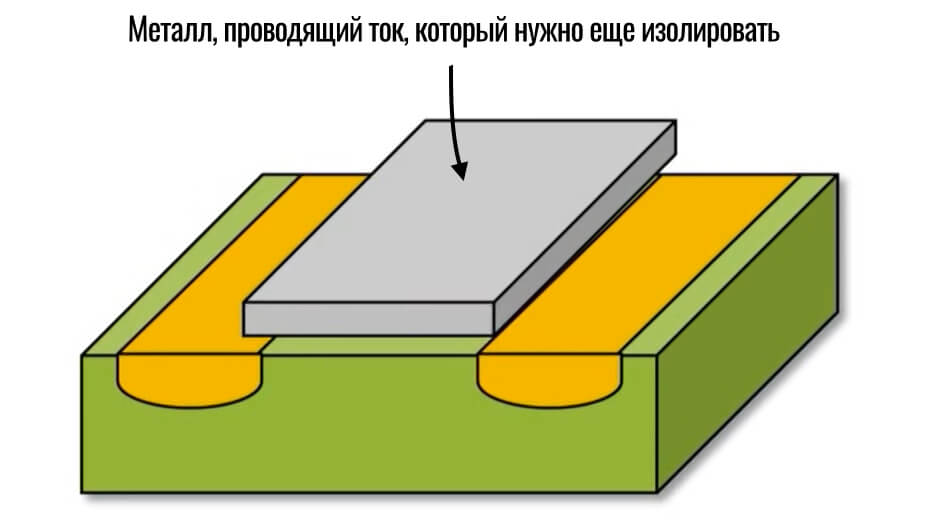

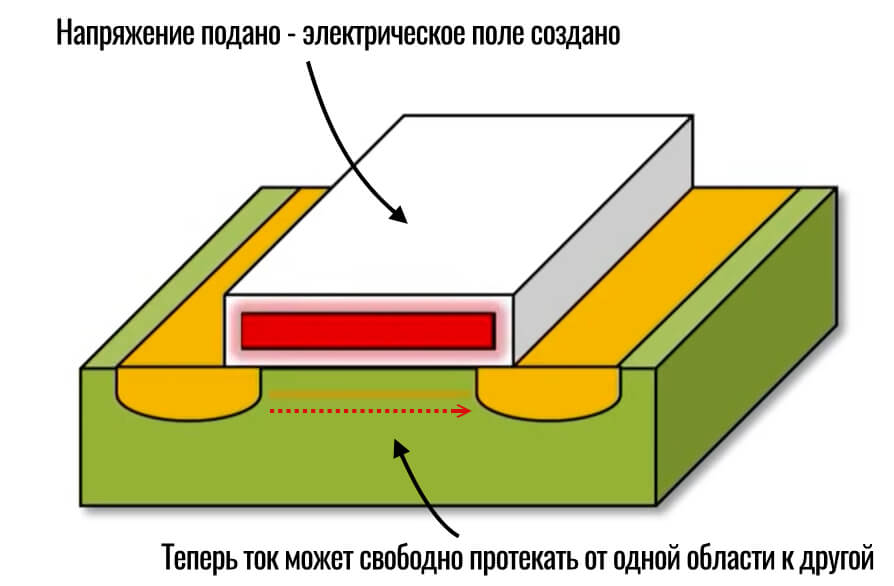

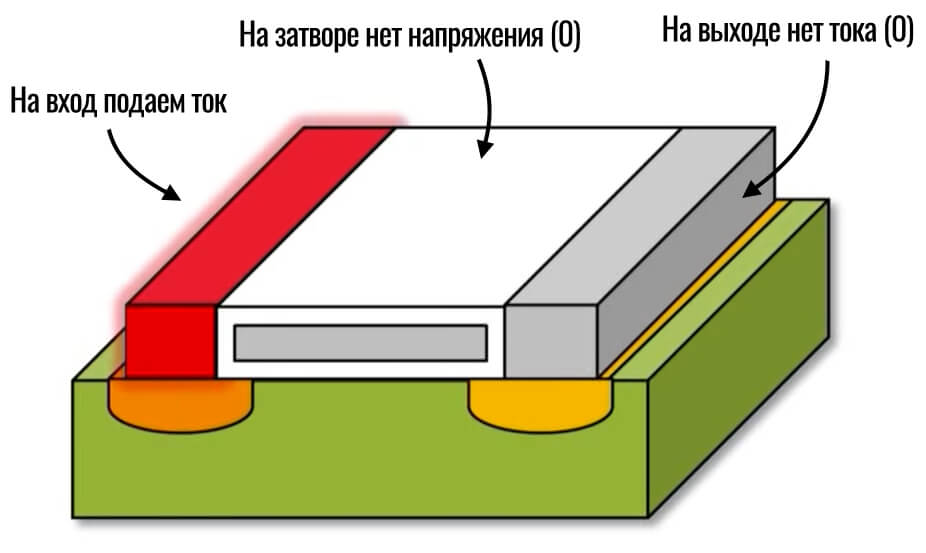

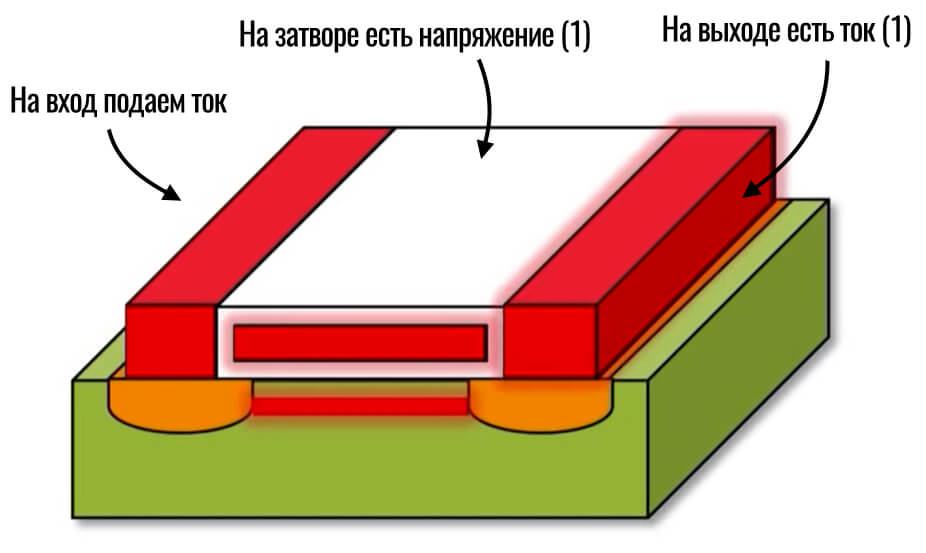

Мы сделали эти области внутри кремниевой подложки таким образом, чтобы ток не смог пройти от входа к выходу. Он будет останавливаться самим кремнием (показан зеленым цветом). Чтобы ток смог пройти от входа к выходу по поверхности кремниевой подложки, нужно сверху разместить проводящий материал (скажем, металл) и хорошенько его изолировать:

Для закрепления материала немножко поиграемся с этим транзистором.

Этого знания более, чем достаточно для того, чтобы ответить на все остальные вопросы, касательно нанометров и логики работы процессора.

О том, какие физические процессы стоят за таким нехитрым переключателем, то есть, что именно заставляет электроны проходить по кремнию, когда над ним появляется электрическое поле, я рассказывать не буду. Возможно, о легировании кремния фосфором и бором, p-n переходах и электрических полях мы поговорим как-нибудь в другой раз. А сейчас перейдем к основному вопросу.

Предположим, у нас есть современный смартфон, процессор которого выполнен по 7-нм техпроцессу. Что внутри такого процессора имеет размер 7 нанометров? Предлагаю вам выбрать правильный вариант ответа:

- Длина транзистора

- Ширина транзистора

- Расстояние между двумя транзисторами

- Длина затвора

- Ширина затвора

- Расстояние между затворами соседних транзисторов

Более того, уменьшая размер транзистора, автоматически снижается его энергопотребление (ток, проходящий через транзистор пропорционален отношению его ширины к длине). Также уменьшается размер затвора и его емкость, позволяя ему переключаться еще быстрее. В общем, одни плюсы!

Так вот, этот человек наблюдал за историей развития вычислительной техники и заметил, что количество транзисторов на кристалле удваивается примерно каждые 2 года. Соответственно, размеры транзисторов уменьшаются на корень из двух раз.

Другими словами, нужно умножать каждую сторону квадратного транзистора на 0.7, чтобы его площадь уменьшилась вдвое:

Повторюсь, до определенного момента эта цифра означала длину канала (или длину затвора), так как эти элементы уменьшались пропорционально размеру транзистора.

Но затем удалось сокращать длину затвора быстрее, чем другие части транзистора. С тех пор связывать размер затвора с техпроцессом стало не совсем корректно, так как это уже не отражало реального увеличения плотности размещения транзисторов на кристалле.

Например, в 250-нм техпроцессе длина затвора составляла 190 нанометров, но транзисторы не были упакованы настолько плотно по сравнению с предыдущим техпроцессом, чтобы называть его 190-нанометровым (по размеру затвора). Это не отражало бы реальную плотность.

Затем длина канала и вовсе перестала уменьшаться каждые два года, так как появилась новая проблема. При дальнейшем уменьшении длины канала, электроны могли обходить узкий затвор, так как блокирующий эффект был недостаточно сильным. Более того, такие утечки возникали постоянно, вызывая повышенное энергопотребление и нагрев транзистора (и, как следствие, всего процессора).

В общем, техпроцесс отвязали от длины затвора и взяли просто группу из нескольких транзисторов (так называемую ячейку) и площадь этой ячейки использовали для названия техпроцесса.

К примеру, в 100-нм техпроцессе ячейка из 6 транзисторов занимала, скажем, 100 000 нанометров (это условная цифра из головы). Компания упорно работала над уменьшением размеров транзисторов или увеличением плотности их размещения и через пару лет добилась того, что в новом процессоре эта же ячейка занимает уже 50 000 нм.

Не важно, уменьшился ли размер транзисторов или просто удалось упаковать их более плотно (за счет сокращения слоя металла и других ухищрений), можно смело говорить, что количество транзисторов на кристалле выросло в два раза. А значит мы умножаем предыдущий техпроцесс (100 нм) на 0.7 и получаем новенький процессор, выполненный по 70-нм техпроцессу.

Однако, когда мы дошли до 22-нанометрового техпроцесса, уменьшать длину затвора уже было нереально, так как электроны проходили бы сквозь этот затвор и транзисторы постоянно бы пропускали ток.

Теперь всё пространство, по которому идет ток, управляется затвором, так как полностью им окружено. А раньше, как мы видим, этот затвор находился сверху над каналом и создавал сравнительно слабый блокирующий эффект.

С новой технологией, получившей название FinFET, можно было продолжать уменьшать длину затвора и размещать еще больше транзисторов, так как они стали более узкими (сравните на картинке ширину канала). Но говорить о размерах транзистора стало вообще бессмысленно. Не совсем понятно даже, как эти размеры теперь высчитывать, когда транзистор из плоского превратился в трехмерный.

Другими словами, нанометровый техпроцесс не описывает размеры транзисторов. Сегодня это условная цифра, означающая плотность размещения транзисторов или увеличение количества транзисторов относительно предыдущего техпроцесса (что напрямую влияет на быстродействие процессора).

В любом случае, важно запомнить простое правило и пользоваться им при анализе характеристик смартфона:

Разница техпроцесса в 0.7 раз означает двукратное увеличение количества транзисторов

Продолжая аналогию, в 5-нм процессоре должно вмещаться в 2 раза больше транзисторов, чем в 7-нанометровом! Если вас не очень удивляет этот факт, обязательно почитайте на досуге мою заметку об экспоненциальном развитии технологий.

Сегодня лидерами полупроводниковой отрасли являются TSMC и Samsung. Обе компании способны выпускать чипы на основе 5-нм техпроцесса. Мало того, обе вкладывают десятки миллиардов долларов модернизацию, что позволит перейти на 3-нм нормы уже в 2022 году. Стоит учитывать, что это будет не экспериментальный подход, а массовый выпуск процессоров для Apple, которая обычно закупает продукцию десятками миллионов единиц. На этом фоне Intel может показаться ленивым разжиревшим котом, который греется в лучах собственной славы и никуда не торопиться. Однако это далеко не так, ведь уже в 2021 году состоится выпуск настольных процессоров на 10-нм техпроцессе, а далее нас ожидает резкое сокращение технологического отставания между лидерами и Intel.

реклама

Итак, уже сегодня Intel уверяет, что завершила один из ключевых этапов разработки 7-нм процессоров, получивших название Meteor Lake. В данном случае мы знаем, что они заявлены на 2023 год, а значит отставание между ключевыми игроками сохранится. На самом деле мы уже видели любопытную информацию о реальной плотности транзисторов в процессорах TSMC и Intel. Для сравнения, 7-нм чип Intel имеет плотность 250 миллионов транзисторов на мм 2 . Так вот, у ребят из TSMC – это скромные 91 миллион транзисторов на 1 мм 2 . Ясно, что 7-нм у тайванцев уже пройдённый этап, ведь в 2023 году они начнут предлагать улучшенный 3-нм техпроцесс с 290 миллионами транзисторов, но это всего лишь немногим больше, чем будет у Intel на тот момент.

Согласно последним слухам, Intel не просто настроена вернуть себе полупроводниковую корону, но и сделать это в ближайшие пять лет. Так, сегодня в прессу попали ожидаемые показатели для 5-нм техпроцесса Intel. Сообщается, что он достигнет невероятных 400 миллионов на 1 мм 2 , что почти в 3 раза лучше, чем предлагает TSMC на своих 5-нм. Точных сроков выхода подобных камушков производства Intel нет, но их ожидают к 2025 году. На тот момент в арсенале TSMC окажется 2-нм техпроцесс неизвестной плотности, но, с высокой долей вероятности, он не будет даже близко равен 400 миллионам транзисторов на 1 мм 2 .

Ключевым элементом практически каждой вычислительной схемы является транзистор. Это полупроводниковый элемент, который служит для управления токами. Из транзисторов собираются основные логические элементы, а на их основе создаются различные комбинационные схемы и уже непосредственно процессоры.

Чем больше транзисторов в процессоре — тем выше его производительность, ведь можно поместить на кристалл большее количество логических элементов для выполнения разных операций.

В 1971 году вышел первый микропроцессор — Intel 4004. В нем было всего 2250 транзисторов. В 1978 мир увидел Intel 8086 и в нем помещались целых 29 000 транзисторов. Легендарный Pentium 4 уже включал 42 миллиона. Сегодня эти числа дошли до миллиардов, например, в AMD Epyc Rome поместилось 39,54 миллиарда транзисторов.

| Модель | Год выпуска | Кол-во транзисторов |

| Xeon Broadwell-E5 | 2016 | 7 200 000 000 |

| Ryzen 5 1600 X | 2017 | 4 800 000 000 |

| Apple A12 Bionic (шестиядерный ARM64) | 2018 | 6 900 000 000 |

| Qualcomm Snapdragon 8cx | 2018 | 8 500 000 000 |

| AMD Ryzen 7 3700X | 2019 | 5 990 000 000 |

| AMD Ryzen 9 3900X | 2019 | 9 890 000 000 |

| Apple M1 ARM | 2020 | 16 000 000 000 |

Много это или мало? На 2020 год на нашей планете приблизительно 7,8 миллиардов человек. Если представить, что каждый из них это один транзистор, то полтора населения планеты

с легкостью поместилась бы в процессоре Apple A14 Bionic.

В 1975 году Гордон Мур, основатель Intel, вывел скорректированный закон, согласно которому число транзисторов на схеме удваивается каждые 24 месяца.

Нетрудно посчитать, что с момента выхода первого процессора до сего дня, а это всего-то 50 лет, число транзисторов увеличилось в 10 000 000 раз!

Казалось бы, поскольку транзисторов так много, то и схемы должны вырасти в размерах на несколько порядков. Площадь кристалла у первого процессора Intel 4004 — 12 мм², а у современных процессоров AMD Epyc — 717 мм² (33,5 млрд. транзисторов). Получается, по площади кристалла процессоры выросли всего в 60 раз.

Как же инженерам удается втискивать такое огромное количество транзисторов в столь маленькие площади? Ответ очевиден — размер транзисторов также уменьшается. Так

и появился термин, который дал обозначение размеру используемых

полупроводниковых элементов.

Упрощенно говоря, техпроцесс — это толщина транзисторного слоя, который применяется в процессорах.

Чем мельче транзисторы, тем меньше они потребляют энергии, но при этом сохраняют текущую производительность. Именно поэтому новые процессоры имеют большую вычислительную мощность, но при этом практически не увеличиваются в размерах

и не потребляют киловатты энергии.

Какие существуют техпроцессы: вчера и сегодня

Первые микросхемы до 1990-х выпускались по технологическому процессу 3,5 микрометра. Эти показатели означали непосредственно линейное разрешение литографического оборудования. Если вам трудно представить, насколько небольшая величина в 3 микрометра, то давайте узнаем, сколько транзисторов может поместиться в ширине человечного волоса.

Уже тогда транзисторы были настолько маленькими, что пару десятков с легкостью помещались в толщине человеческого волоса. Сейчас техпроцесс принято соотносить с длиной затвора транзисторов, которые используются в микросхеме. Нынешние транзисторы вышли на размеры в несколько нанометров.

Для Intel актуальный техпроцесс — 14 нм. Насколько это мало? Посмотрите в сравнении

с вирусом:

Однако по факту текущие числа — это частично коммерческие наименования. Это означает, что в продуктах по техпроцессу 5 нм на самом деле размер транзисторов не ровно столько, а лишь приближенно. Например, в недавнем исследовании эксперты сравнили транзисторы от Intel по усовершенствованному техпроцессу 14 нм и транзисторы от компании TSMC на 7 нм. Оказалось, что фактические размеры на самом деле отличаются не на много, поэтому величины на самом деле относительные.

Рекордсменом сегодня является компания Samsung, которая уже освоила техпроцесс 5 нм. По нему производятся чипы Apple A14 для мобильной техники. Одна из последних новинок Apple M1 — первый ARM процессор, который будет установлен в ноутбуках от Apple.

Продукцию по техпроцессу в 3 нм Samsung планирует выпускать уже к 2021 году. Если разработчикам действительно удастся приблизиться к таким размерам, то один транзистор можно будет сравнить уже с некоторыми молекулами.

Насколько маленьким может быть техпроцесс

Уменьшение размеров транзисторов позволяет делать более энергоэффективные и мощные процессоры, но какой предел? На самом деле ответа никто не знает.

Проблема кроется в самой конструкции транзистора. Уменьшение прослойки между эмиттером и коллектором приводит к тому, что электроны начинают самостоятельно просачиваться, а это делает транзистор неуправляемым. Ток утечки становится слишком большим, что также повышает потребление энергии.

Не стоит забывать, что каждый транзистор выделяет тепло. Уже сейчас процессоры Intel Core i9-10ХХХ нагреваются до 95 градусов Цельсия, и это вполне нормальный показатель. Однако при увеличении плотности транзисторов температуры дойдут до таких пределов, когда даже водяное охлаждение окажется полностью бесполезным.

Самые смелые предсказания — это техпроцесс в 1,4 нм к 2029 году. Разработка еще меньших транзисторов, по словам ученых, будет нерентабельной, поэтому инженерам придется искать другие способы решения проблемы. Среди возможных альтернатив — использование передовых материалов вместо кремния, например, графена.

Читайте также: