Данные в конденсаторе ячейки оперативной памяти хранятся до замены их на новые данные

Обновлено: 06.07.2024

ОЗУ – это наибольшая часть основной памяти. ОЗУ предназначено для хранения переменной (текущей, быстро изменяющейся) информации и допускает изменение своего содержимого в ходе выполнения процессором вычислений. Это означает, что процессор может выбрать (режим считывания) из ОЗУ команду или данные и после обработки поместить полученный результат (режим записи) в ОЗУ. Размещение новых данных возможно на тех же местах, где ранее находились исходные данные. Понятно, что прежние данные будут стерты. ОЗУ позволяет кратковременно (до выключения питания) хранить записанную информацию. Данные, адреса и команды, которыми процессор обменивается с памятью, часто называют операндами.

Выполняемая в данный момент компьютером программа (активная) чаще всего располагается в ОЗУ (и лишь иногда в ПЗУ).

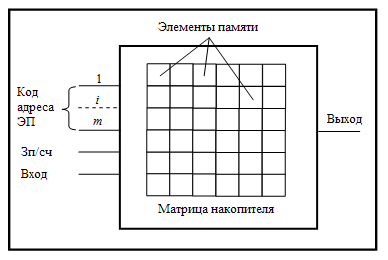

Основная составная часть ОЗУ – массив элементов памяти, объединенных в матрицу накопителя (рис. 9.1). Элемент памяти (ЭП) может хранить 1 бит информации (запоминать два состояния 0 или 1).

Рис. 9.1. Устройство ОЗУ

Каждый ЭП имеет свой адрес (по-другому можно сказать — порядковый номер). Для обращения к ЭП (с целью записи или считывания информации) его необходимо «выбрать» с помощью кода адреса. Оперативная память является электронной памятью, потому что она создается с помощью микросхем — изделий микроэлектроники.

Микросхемы памяти бывают одноразрядные и многоразрядные.

В одноразрядных микросхемах памяти код адреса (иногда говорят просто — адрес) выбирает один элемент памяти из множества элементов, расположенных в матрице накопителя. После выбора элемента в него можно записать информацию или, наоборот, считать из него 1 бит информации. Специальный управляющий сигнал Зп/сч (Write/Read) указывает микросхеме, что она должна делать: записывать или считывать информацию. Управляющие сигналы на этот вход поступают от процессора. В одноразрядных микросхемах памяти имеются один вход для записи информации и один выход для ее считывания.

Разрядность кода адреса m в одноразрядных микросхемах памяти определяет информационную емкость, т. е. число ЭП в матрице накопителя. Емкость такой микросхемы рассчитывается по формуле 2m. Например, если у одноразрядной микросхемы памяти имеется 10 адресных входов, то информационная емкость составит N = 210 = 1024 бита.

Некоторые микросхемы памяти имеют многоразрядную структуру, называемую также словарной. У таких микросхем памяти имеется несколько информационных входов и столько же выходов. Поэтому они допускают одновременную запись (или считывание) многоразрядного кода, который принято называть словом. Один адрес позволяет считать информацию сразу из нескольких ЭП. Группа элементов памяти, из которых одновременно считывается информация, называется ячейкой памяти. Таким образом, ячейка памяти — это несколько ЭП, имеющих общий адрес.

На английском языке оперативная память называется Random Access Memory (RAM) — память с произвольным доступом. Термин «произвольный доступ» означает, что можно считать (записать) информацию в любой момент времени из любого (в любой) ЭП. Заметим, что существует и другая организация памяти, при которой, прежде чем считать нужную информацию, нужно «вытолкнуть» ранее поступившие операнды.

Используется два основных типа оперативной памяти: статическая (SRAM — Static RAM) и динамическая (DRAM — Dynamic RAM).

Эти две разновидности памяти различаются быстродействием и удельной плотностью (емкостью) хранимой информации. Быстродействие памяти характеризуется двумя параметрами: временем доступа (access time) и длительностью (cycle time).

Эти величины, как правило, измеряются в наносекундах. Чем меньше эти величины, тем выше быстродействие памяти.

Время доступа представляет собой промежуток времени между формированием запроса на чтение информации из памяти и моментом поступления из памяти запрошенного машинного слова (операнда).

Длительность цикла определяется минимальным допустимым временем между двумя последовательными обращениями к памяти.

В статической памяти элементы построены на триггерах – схемах с двумя устойчивыми состояниями. Для построения одного триггера требуется 4 – 6 транзисторов. После записи информации в статический элемент памяти он может хранить информацию сколь угодно долго (пока подается электрическое питание).

Конструктивно микросхема памяти выполняется в виде прямоугольной матрицы, причем ЭП располагаются на пересечении строк и столбцов. При обращении к микросхеме статической памяти на нее подается полный адрес, который разбивается на две части. Одна часть адреса используется для выбора строк матрицы накопителя, а другая – для выбора столбцов.

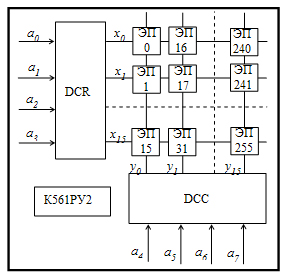

На рис. 9.2. приведена структурная схема микросхемы памяти К561РУ2, у которой 8 адресных входов: a7a6, …, a0. Это позволяет разместить в матрице 2 8 = 256 элементов памяти. Адресные входы разделены на две равные части (матрица квадратная). Младшая часть адреса a3a2a1a0позволяет выбрать одну из 16 строк x0, x1, x2, …, x15. При помощи старшей части адреса a7a6a5a4 происходит выбор одного из 16 столбцовy0, y1, …, y15.

Рис. 9.2. Структурная схема микросхемы памяти К561РУ2

Чтобы выбрать какой-либо ЭП, нужно активизировать строку и столбец, на пересечении которых располагается нужный ЭП.

Например, чтобы выбрать ЭП 0, нужно на все адресные входы микросхемы подать нули, тогда дешифратор строк DCR (Decoder Row) и дешифратор столбцов DCC (Decoder Column) активизируют соответственно строку x0 и столбец y0. На их пересечении располагается ЭП 0, в который, после его выбора, можно записать (или считать) информацию.

Аналогично выбираются другие ЭП. Так, для выбора ЭП 241 нужно активизировать строку x1 и столбец y15. Для этого на младшую группу адресов (a3, …, a0) нужно подать двоичный код 0001, а на старшую группу адресов (a7, …, a4) – все единицы.

Статическая память имеет высокое быстродействие и низкую удельную плотность размещения хранящихся данных. В динамической памяти ЭП построены на основе полупроводниковых конденсаторов, занимающих гораздо меньшую площадь, чем триггеры в статических ЭП. Для построения динамического элемента памяти требуется всего 1–2 транзистора.

Подключение и отключение конденсаторов в динамических ЭП осуществляется с помощью полупроводниковых транзисторов (ключей), которые в закрытом состоянии имеют сопротивление порядка 10 10 Ом. Несмотря на то, что сопротивление закрытого транзистора велико, оно все же конечно, и по этой причине через закрытый транзистор происходит разряд конденсатора. Самопроизвольный разряд конденсатора не позволяет без специальных мер долгое время хранить записанную информацию. Для устранения влияния нежелательного разряда конденсатора через так называемые паразитные цепи утечки приходится периодически подзаряжать конденсаторы. Этот процесс называется регенерацией заряда.

Регенерация заряда должна происходить достаточно часто. Подтверждением этого являются следующие рассуждения. Так как необходимо получить высокую удельную плотность хранения информации, емкость конденсатора не может быть большой (практически величина емкости запоминающих конденсаторов составляет порядка 0,1 пФ). Постоянная времени разряда определяется как произведение емкости конденсатора на сопротивление закрытого транзистора. Это произведение составляет величину порядка

Таким образом, постоянная времени разряда составляет 1 мс и, значит, регенерация заряда должна происходить примерно 1000 раз в 1 с.

Необходимость частой подзарядки запоминающих конденсаторов в матрице накопителя приводит к снижению быстродействия динамической памяти. Однако благодаря малым размерам конденсатора и малому числу дополнительных элементов удельная плотность хранения информации динамической памяти выше, чем у статической памяти.

Емкость микросхем динамической памяти составляет десятки мегабит на один корпус. Возможность размещения на одном кристалле большого числа ЭП вызывает другую конструкторскую проблему: необходимо использовать большое число адресных входов. Для снижения остроты этой проблемы используют мультиплексирование.

Мультиплексирование — это технический прием временного уплотнения информации, благодаря которому удается по одним и тем же электрическим цепям передать разную информацию для различных приемников (потребителей) информации. Так, конструкторы вдвое уменьшают число адресных входов у микросхем памяти. Адрес делят на две равные части и вводят его в микросхему поочередно: сначала младшую часть, а затем старшую часть адреса. При этом первая часть осуществляет выбор нужной строки в матрице накопителя, а вторая часть активизирует соответствующий столбец.

Для того чтобы микросхема памяти «знала», какая часть адреса вводится в данный момент времени, ввод каждой группы адреса сопровождается соответствующим управляющим сигналом.

Так, синхронно с вводом младшей части адреса на микросхему подается сигнал RAS (Row Address Strobe) – сигнал стробирования (сопровождения) адреса строки. Практически одновременно с вводом старшей части адреса на микросхему памяти подается сигнал CAS (Column Address Strobe) – стробирование адреса столбца.

После завершения выбора какого-либо ЭП требуется время, в течение которого происходит восстановление микросхемы в исходное состояние. Данная задержка связана с необходимостью перезарядки внутренних цепей микросхемы. Длительность этой задержки существенна и составляет до 90% от времени цикла.

Обходят это нежелательное явление различными конструктивными ухищрениями. Например, при записи нескольких следующих друг за другом операндов их располагают на одной строке матрицы, но в разных столбцах. Экономия времени достигается тем, что не нужно ожидать завершения переходных процессов при смене адреса строк.

Другой способ повышения быстродействия заключается в том, что память разбивают на блоки (банки), из которых процессор считывает данные попеременно. Таким образом, пока считываются данные из одной области памяти, другая получает время на завершение переходных процессов.

Разработаны различные модификации статической и динамической памяти.

FPM DRAM (Fast Page Mode DRAM) – динамическая память с быстрым странич-ным доступом. Память со страничным доступом отличается от обычной динамической памяти тем, что после выбора одной строки матрицы удерживается сигнал выбора строки RAS и производится многократное изменение адресов столбцов (с помощью сигнала CAS). В этом случае не тратится время на завершение переходных процессов при изменении адреса строки. Другими словами, адрес строки остается некоторое время постоянным, а изменяются адреса столбцов. В этом случае страницей называют элементы памяти, расположенные на одной строке матрицы.

EDO (Extended Data Out) – эти микросхемы характеризуются увеличенным временем удержания данных на выходе. Фактически представляют собой обычную память FPM DRAM, на выходе которой установлены регистры – защелки данных. Регистры – это цифровые устройства, построенные на триггерах и позволяющие хранить сразу несколько бит информации (слово). При страничном обмене такие микросхемы удерживают на выходах микросхемы содержимое последней выбранной ячейки памяти, в то время как на их входы уже подается адрес следующей выбираемой ячейки памяти. Это позволяет примерно на 15% по сравнению с FРM ускорить процесс считывания последовательно расположенных массивов данных.

SDRAM (Synchronous DRAM – синхронная динамическая память) – память с синхронным доступом, работающая быстрее обычной асинхронной памяти. Основу этого типа памяти составляет традиционная схема DRAM. Однако SDRAM отличается тем, что использует тактовый генератор для синхронизации всех сигналов, применяемых в микросхеме памяти. Помимо синхронного метода доступа, SDRAM использует внутреннее разделение массива памяти на два независимых банка, что позволяет совмещать по времени выборку из одного банка с установкой адреса в другом банке.

Оперативная память (ОЗУ, RAM), самая известная из всех рассмотренных ранее форм компьютерной памяти. Эту память называют памятью «произвольного доступа» («random access»), поскольку вы можете получить доступ к любой ее ячейке непосредственно. Для этого достаточно знать строку и столбец, на пересечении которых находится нужная ячейка. Известны два основных вида оперативной памяти: динамическая и статическая. Сегодня мы подробно рассмотрим принцип «дырявого ведра», на котором основана динамическая память. Некоторое внимание будет уделено и статической памяти, быстрой, но дорогой.

Ячейка памяти подобна дырявому ведру

Совсем иначе работает память с последовательным доступом (SAM). Как и следует из ее названия, доступ к ячейкам этой памяти осуществляется последовательно. Этим она напоминает пленку в магнитофонной кассете. Когда данные ищутся в такой памяти, проверяется каждая ячейка до тех пор, пока не будет найдена нужная информация. Память этого типа используется для реализации буферов, в частности буфера текстур видеокарт. То есть SAM имеет смысл применять в тех случаях, когда данные будут расположены в том порядке, в котором их предполагается использовать.

Подобно подробно рассмотренному ранее микропроцессору, чип памяти является интегральной микросхемой (ИС, IC), собранной из миллионов транзисторов и конденсаторов. Одним из наиболее распространенных видов памяти произвольного доступа является DRAM (динамическая память произвольного доступа, dynamic random access memory). В ней транзистор и конденсатор спарены и именно они образуют ячейку, содержащую один бит информации. Конденсатор содержит один бит информации, то есть «0» или «1». Транзистор же играет в этой паре роль переключателя (свитча), позволяющего управляющей схеме чипа памяти считывать или менять состояние конденсатора.

Конденсатор можно представить себе в виде небольшого дырявого «ведерка», которое при необходимости заполняется электронами. Если оно заполнено электронами, его состояние равно единице. Если опустошено, то нулю. Проблемой конденсатора является утечка. За считанные миллисекунды (тысячные доли секунды) полный конденсатор становится пустым. А это значит, что или центральный процессор, или контроллер памяти вынужден постоянно подзаряжать каждый из конденсаторов, поддерживая его в наполненном состоянии. Подзарядку следует осуществлять до того, как конденсатор разрядится. С этой целью контроллер памяти осуществляет чтение памяти, а затем вновь записывает в нее данные. Это действие обновления состояния памяти осуществляется автоматически тысячи раз за одну только секунду.

Конденсатор динамической оперативной памяти можно сравнить с протекающим ведром. Если его не заполнять электронами снова и снова, его состояние станет нулевым. Именно эта операция обновления и внесла в название данного вида памяти слово «динамическая». Такая память или обновляется динамически, или «забывает» все, что она «помнила». Есть у этой памяти существенный недостаток: необходимость постоянно обновлять ее требует времени и замедляет работу памяти.

Устройство ячейки динамической оперативной памяти (DRAM)

Структуру памяти можно представить себе в виде трехмерной сетки. Еще проще: в виде листка из школьной тетради в клеточку. Каждая клеточка содержит один бит данных. Сначала определяется столбец, затем данные записываются в определенные строки посредством передачи сигнала по данному столбцу.

Только вместо листа из тетради в оперативной памяти используется кремниевая пластина, в которую «впечатаны» столбцы (разрядные линии, bitlines) и строки (словарные шины, wordlines). Пересечение столбца и строки является адресом ячейки оперативной памяти.

Динамическая оперативная память передает заряд по определенному столбцу. Этот заряд называют стробом адреса столбца (CAS, Column Adress Strobe) или просто сигналом CAS. Этот сигнал может активировать транзистор любого бита столбца. Управляющий сигнал строки именуется стробом адреса строки (RAS, Row Adress Strobe). Для указания адреса ячейки следует задать оба управляющих сигнала. В процессе записи конденсатор готов принять в себя заряд. В процессе чтения усилитель считывания (sense-amplifier) определяет уровень заряда конденсатора. Если он выше 50 %, бит читается, как «1»; в остальных случаях, как «0».

Осуществляется также обновление заряда ячеек. За порядком обновления следит счетчик. Время, которое требуется на все эти операции, измеряется в наносекундах (миллиардных долях секунды). Если чип памяти 70-наносекундный, это значит, полное чтение и перезарядка всех его ячеек займет 70 наносекунд.

Сами по себе ячейки были бы бесполезны, если бы не существовало способа записать в них информацию и считать ее оттуда. Соответственно, помимо самих ячеек, чип памяти содержит целый набор дополнительных микросхем. Эти микросхемы выполняют следующие функции:

- Идентификации строк и столбцов (выбор адреса строки и адреса ячейки)

- Отслеживание порядка обновления (счетчик)

- Чтение и возобновление сигнала ячейки (усилитель)

- Донесение до ячейки сведений о том, следует ли ей удерживать заряд или нет (активация записи)

У контроллера памяти есть и другие функции. Он выполняет набор обслуживающих задач, среди которых следует отметить идентификацию типа, скорости и объема памяти, а также проверку ее на ошибки.

Статическая оперативная память

Хотя статическая оперативная память (подобно динамической) является памятью произвольного доступа, она основана на принципиально иной технологии. Триггерная схема этой памяти позволяет удерживать каждый бит сохраненной в ней информации. Триггер каждой ячейки памяти состоит из четырех или шести транзисторов и содержит тончайшие проводки. Эта память никогда не нуждается в обновлении заряда. По этой причине, статическая оперативная память работает существенно быстрее динамической. Но поскольку она содержит больше компонентов, ее ячейка намного крупнее ячейки динамической памяти. В итоге чип статической памяти будет менее емким, чем динамической.

Статическая оперативная память быстрее, но и стоит дороже. По этой причине статическая память используется в кэше центрального процессора, а динамическая в качестве системной оперативной памяти компьютера. Более подробно о статической памяти написано в разделе «Кэш-память и регистр процессора» материала, посвященного преодолению ограничений компьютерной памяти.

| Конфигурация компьютера | |

| Процессор: Intel Xeon E3-1245 V2 + Thermaltake Contact 29 | |

| Материнская плата: GA-H77-DS3H v.1.0 | |

| Память: Samsung M378B5773DH0-CK0 2 ГБ DDR3-1600 - 2шт. | |

| HDD: Kingchuxing 64 Gb mSATA + ST3320418AS + HD103UJ + WD10EADS | |

| Видеокарта: Intel HD Graphics Р4000 | |

| Звук: ASUS Xonar D1 PCI 7.1 Audio Card + Pioneer A505R + Pioneer CS701 | |

| Блок питания: Inwin IW-P350J2-0 | |

| CD/DVD: ASUS DRW-24B3ST | |

| Монитор: Samsung SyncMaster 940n | |

| ОС: Windows XP Professional SP3 | |

| Индекс производительности Windows: 25 | |

| Прочее: Тюнер AverTV USB 2.0 plus, корпус Ikonik zaria a20 |

есть то оно есть, вопрос только откуда оно взялось? Основной носитель это микросхема ПЗУ, полупроводник то бишь, насколько знаю у полупроводников не регламентируется количество открытий/закрытий p-n перехода, также нет и никаких механических трущихся, вращающихся и т.д. механических частей. На физическом уровне вроде не проглядывается факторов ограничения срока "жизни" ОЗУ, это кстати должно относиться и к процессору, он тоже полупроводник. Возможно что изготовитель может применить какой-нибудь подсчет срока эксплуатации собирая статистику типа средней наработки устройства на отказ, которая зависит и от других параметров и устройств, как-то качества питающего напряжения, температуры и т.д.

Зы. Специально этим вопросом не интересовался, не гуглил, изложил то что в голове "висело"

Обычно оперативная память является динамической (Dynamic RAM – DRAM), т.е. значение бита информации в элементе памяти определяется наличием или отсутствием заряда на миниатюрном конденсаторе, управляемом одним или двумя транзисторами. Из-за необходимости ожидания перезарядки конденсаторов (накопления или стекания заряда) быстродействие DRAM относительно не высокое (access time

70 нс). Кроме того, так как конденсаторы чрезвычайно малы, высока вероятность непроизвольного изменения их состояния из-за паразитных утечек и наводок (как ведро с водой, в дне которого есть маленькие дырки). Поэтому для исключения утраты данных периодически проводятся циклы регенерации (refresh rate), заключающиеся в последовательном считывании и повторной записи всей информации. Во время регенерации доступ к ячейкам памяти также невозможен. Времённой интервал между циклами регенерации составляет около 2 мс. Именно из-за необходимости этого регулярного обновления такая память называется динамической.

Для повышения быстродействия DRAM используются специальные методы управления памятью:

- чередование адресов (interleaving mode). Этот метод применяется для уменьшения задержки, связанной с перезарядкой конденсаторов. Для этого каждые последовательно выбираемые ячейки памяти должны относиться к разным блокам (банкам). Пока процессор считывает данные из одного блока, другой получает время для перезарядки. Банки (блоки) ячеек – это две независимые группы ячеек внутри микросхемы;

- страничная выборка (fast paging mode – FPM).

< p>Современные микросхемы памяти с прямым доступом имеют матричную структуру. Запоминающие элементы расположены на пересечении вертикальных и горизонтальных шин матрицы; запись и считывание информации осуществляются подачей электрических импульсов по тем шинам матрицы, которые соединены с элементами, принадлежащими выбранной ячейке памяти. Физический адрес ячейки состоит из адресов строки и столбца. Для считывания (записи) информации на микросхему сначала подается код адреса строки, а затем (одновременно или с небольшой задержкой) – сигнал RAS (Row Address Select) выбора адреса строки. Затем через нормируемое время задержки должен быть подан код адреса столбца, сопровождаемый сигналом CAS (Column Address Select) выбора адреса столбца. Под временем выборки (обращения) к памяти подразумевают именно сигнал RAS. После выборки данных нужной ячейки содержимое строки опять записывается на прежнее место в оперативной памяти. Такие переносы данных осуществляются путем изменения состояния конденсаторов, т.е. происходит процесс заряда (или разряда).

Следующее обращение к памяти возможно только через некоторое время, необходимое для восстановления внутренних цепей. Этот промежуток называют временем перезарядки (recharge time), причем оно составляет почти 90% от общего времени выборки. Использование микросхем со страничной организацией памяти позволяет избежать повторения сигнала RAS, если адреса строк выбираемых ячеек памяти лежат в пределах одной страницы (емкость страницы обычно 2 Кбайта). Время доступа может быть сокращено до 60 нс. Может работать без задержки с системными шинами на частоте 33 МГц.

- хранение (удержание) считанных данных в специальных регистрах в течение цикла следующего запроса (extended data output – EDO). Память EDO работает на 10-15% быстрее, чем FPM. Однако преимущество проявляется лишь при чтении данных. Может работать без задержки с системными шинами на частоте 50 МГц.

- чтение сразу четырех слов, расположенных рядом (burst mode – BEDO). Разновидность EDO. Однако эта более быстрая память так и не появилась на рынке, проиграв SDRAM памяти. Может работать без задержки с системными шинами на частоте 66 МГц;

- использование встроенной кэш-памяти на микросхемах SRAM (CDRAM– Cache DRAM и EDRAM – Enhanced (улучшенная) DRAM). Например, на одном кристалле могут находиться 4Мб DRAM и 16Кб SRAM;

В последние годы наиболее популярна разновидность динамической памяти – синхронная SDRAM (Synchronous DRAM), тактирующаяся теми же тактовыми сигналами, что и процессор. В результате чего системный таймер знает точный такт, на котором запрошенные данные могут быть получены и обработаны, что освобождает процессор от необходимости находиться в состоянии ожидания между моментами доступа к памяти. Таким образом, фактическое время выборки данных непосредственно не изменяется, однако увеличивается эффективность работы процессора.

В этой памяти реализованы наряду с синхронным функционированием, такие методы ускорения быстродействия как чередование адресов и работа в пакетно-конвейерном режиме. При пакетном режиме автоматически генерируется серия последовательных адресов (блок данных) в каждый момент, когда процессор запрашивает один адрес. При этом используется предположение о том, что адреса следующих данных, которые будут запрошены процессором, будут следующими по отношению к текущему запрошенному адресу. Такое же предсказание используется в алгоритме работы кэш-памяти. Пакетный режим применяется как при операциях чтения, так и записи. Конвейерная адресация позволяет осуществлять доступ к запрошенным вторыми данным, до завершения обработки запрошенных первыми данных.

SDRAM быстрее стандартной DRAM почти в 4 раза, по сравнению с памятью EDO обеспечивает прирост производительности на 50%. Имеет пропускную способность 100 Мбайт/с. Может работать без задержки с системными шинами на частоте 100 МГц.

В последнее время появились улучшенные варианты памяти с архитектурой SDRAM: DDR (Double Data Rate) SDRAM (или SDRAM II), работающие с удвоенной скоростью передачи данных даже на той же частоте и ESDRAM (Enhanced SDRAM), имеющие блок кэш-памяти и время доступа к самим ячейкам 22 нс, а к строке кэша 12 нс, и позволяющие работать на частоте 133 МГц.

Для работы с процессорами Intel Pentium-IV предназначен новый тип оперативной памяти с архитектурой RAMbus: RDRAM, позволяющие работать на частоте до 600 МГц со скоростью передачи данных 600 Мбайт/с и DRDRAM (Direct RAMbus DRAM), работающие на частоте 800 МГц и выше со скоростью передачи данных до 1,6 Гбайт/с.

У DIMM модулей в отличие от SIMM контакты на противоположных сторонах платы не связаны между собой, что позволило увеличить количество выводов более чем вдвое (с 72 до 168) и, следовательно, увеличить соотношение ширины системной шины (у Pentium 64-разрядная) к геометрическим размерам модуля. Модули DIMM иногда называют также двусторонними (double sided) SIMM. На DIMM-модули наряду с микросхемами SDRAM устанавливают микросхемы буфера ввода-вывода, в котором сохраняются поступившие данные, освобождая контроллер, и микросхема ПЗУ – SPD (Serial Presence Detect), в которой записана информация о модуле и производителе.

На материнскую плату можно установить несколько (два и более) модулей DIMM (или SIMM).

Постоянная память (Read-Only Memory – ROM) служит для хранения неизменяемой (постоянной) программной и справочной информации и позволяет только считывать хранящуюся в ней информацию.

ПЗУ выполняют на специальных электронных элементах, обеспечивающих долговременное, энергонезависимое (non volatile) хранение информации.

Содержимое постоянной памяти заполняется либо при изготовлении микросхем памяти и не может быть изменено (непрограммируемые ПЗУ – в настоящее время практически не применяются), либо с помощью специального ПЗУ-программатора (ПЗУ-прожигателя) и не может быть в дальнейшем отредактировано (PROM – Programmable ROM).

Современные ПЗУ, позволяют удалять хранимую в них информацию и заносить новую. Такое ПЗУ называется стираемым (EPROM – Erasable PROM). EPROM микросхему легко отличить от остальных. Она имеет прозрачное окошко на крышке корпуса. Обычно это окошко закрыто какой-либо наклейкой. И неспроста. Информация в микросхеме стирается ультрафиолетовыми лучами. Запись новой информации осуществляется электрически с помощью внешнего программатора, подключаемого к ЭВМ. Для перезаписи информации необходимо подать на специальный вход микросхемы памяти напряжение программирования (12В), что исключает возможность случайного стирания информации. Время доступа 50 нс, время стирания всей информации 300 с, время записи одного байта 10 мкс

В последнее время ПЗУ строятся на основе микросхем Flash ROM (или EEPROM – Electrically EPROM), содержание которых может перезаписываться при помощи специальной программы. Время стирания намного меньше 1-2 с, время записи 100 нс

FLASH-память может быть полезной как для замены программы BIOS, позволяя оперативно обновлять и заменять эти программы на более новые версии при модернизации ПК, так и для создания весьма быстродействующих компактных твердотельных дисков.

Статьи к прочтению:

Золото из микросхем памяти RAM

Похожие статьи:

Читайте также: