Насколько увеличить производительность кэш процессора

Обновлено: 06.07.2024

Современный процессор является сложным устройством, которое выполняет множество действий для решения поставленной задачи. И делает это всё современный процессор очень быстро. Настолько, что даже несмотря на название «оперативная память», память эта недостаточно оперативная. Если бы процессор всегда ждал данных из оперативной памяти, то ему приходилось бы простаивать по несколько десятков, а временами, и сотен тактов не делая ничего. Подобное поведение сделало бы любые улучшения внутри ядер процессора полностью бесполезными. И, если посмотреть в историю развития процессоров, проблема эта с ростом производительности процессоров становилась всё более острой. Вначале появлялись опциональные чипы кэша процессора, то есть места на плате куда можно установить чип памяти кеша L2. С ростом производительности такая «опция» уже перестала появляться, так как потери производительности без него становились слишком большими. Та же судьба была и у L3, который так же был вначале прерогативой серверных решений и располагался вне процессора и только с развитием полупроводникового производства на общем кристалле с ядрами стало достаточно места чтобы разместить ещё и кэш L3.

Кэши L2 и L3 позволяют получать процессору данные максимально быстро. В современных моделях задержки достигают единиц наносекунд. Что, в прочим, тоже для процессора довольно долго. Но современные архитектуры процессоров на подобные задержки и рассчитаны. Естественно процессор не будет пропускать по несколько тактов работы ожидая данные из кеша L3. Для того чтобы такое не случалось внутри процессорного конвейера организовываются очереди микроопераций, в которых они и выдерживаются до тех пор пока необходимые данные не будут доступны для использования уже в регистровой памяти процессора.

Схема процессорного конвейера ядра intel архитектуры Skylake с выделенными регистрами

Но если так случилось, что микрооперация попала в конвейер, а данные для её выполнения расположены не в каком-то из кэшей, а в оперативной памяти (или вообще в постоянной памяти), то процессору ничего не остаётся как пропустить эту микрооперацию, оставив её в очереди, и выполнять следующие за ней мирооперации. И называется это «мероприятие» промах в кэш (Cache Miss).

Проблема тут в том, что для следующих микроопераций могут быть нужны данные которые должны были быть получены в той, что «застряла» в очереди… И всё это нарастает как снежный ком, который в конечном итоге приводит к тому, что часть времени процессор будет простаивать, не развивая свою максимальную теоретическую производительность.

И естественно, что чем больше объём кэш памяти, тем реже будут происходить промахи в кэш, а значит реже будут простои, что в свою очередь приведёт к росту производительности в реальных задачах.

Насколько большая разница от изменения объёма?

И встаёт закономерный вопрос: «На сколько же велико влияние?».

Ответ на него, к сожалению, однозначным быть не может, так как всё зависит от конкретного приложения. Если его данные и все создаваемые им результаты помещаются в кэш, то последующее увеличение размера кэша вообще не приведёт к росту производительности. А если приложение постоянно обращается к совершенно разным участкам памяти, плохо оптимизировано под использование только что созданных процессором результатов, которые только-только были записаны в кэш, то разница от увеличения объёма может быть несколько крат.

Производители процессоров подбирают объёмы регистов и кэша исходя из экономической целесообразности, тратя транзисторный бюджет на то, что будет давать большую производительность при равной цене.

Для некой усреднённой задачи может получится зависимость производительности от цены при изменения объёма кэша примерно такая:

Как измерить разницу от объёма?

И перейдём уже к практической области решения данного вопроса.

Для того чтобы понять разницу необходима некая конфигурация систем в которых отличия ограничиваются только объёмом кэш памяти.

В нашем случае это процессоры i7 7700k и i9 9900k. В последнем отключено 4 ядра из восьми (кэш память при этом не отключается).

Про то как установить процессоры 8 и 9 поколений на платы для 6 и 7 поколений процессоров можете посмотреть тут.

Для игр так же стоит упомянуть о видеокарте: Gainward GeForce RTX 2070 Phoenix с небольшим заводским разгоном.

Обзор видеокарты можно посмотреть тут.

Важно чтобы в играх производительность ограничивалась именно процессором, а не видеокартой. Если у процессора будет возможность делать простои, то именно в них все проблемы по накапливанию невыполнимых операций и будут решаться без вреда для производительности игры. Так что в играх тесты сделаны на пресетах максимальных настроек, но без сглаживания и в сниженном разрешении (768р).

Результаты

Для начала проведём тест который покажет, что объём кэша действительно разный.

Тест задержек кэша и памяти позволяет увидеть переходы к разным уровням кэша и на оперативную память по увеличению задержек. График отлично показывает разницу в объёме кэша L3 по смещению долгих задержек от оперативной памяти (график логарифмический, поэтому двукратная разница в объёме выглядит не двукратной на глаз).

Теперь, убедившись в том, что всё идёт по плану можно перейти к бэнчмаркам, которые плохо реагируют на разгон памяти. Теоретически они должны слабо реагировать и на увеличение объёма кеша, так как отсутствие прироста от памяти говорит о малом числе промахов в кэш.

Все тесты проводились по 3 раза с усреднением результатов.

В Cinebench R15 разница 0,4% (незначительно превышает погрешности теста).

Тесты которые слабо реагируют на разгон памяти слабо реагируют и на увеличение объёма кэш памяти.

Далее рассмотрим блок тестов, в которых бенчмарки зависимые от частоты и задержек памяти.

7-Zip. Прирост 4,5%.

CPU тест 3D Mark Time Spy. Прирост 3,7%

Выводы по бэнчмаркам

В идеальных задачах максимально оптимизированных для процессора и работы с памятью прирост находится в пределах 0-2%.

Для задач имеющий меньшую оптимизацию или связанных с работой с данными прирост от увеличения объёма кэш памяти составил от 3,7 до 35%.

Far Cry 5

На графиках выше можно увидеть разницу и без цифр. На графиках изображены все удачные прогоны бенчмарка. Все они нанесены для оценки отличий результатов от погрешностей проведения тестов.

Результаты в цифрах:

| AVG | Low 0.1% | Low 1% | Low 5% | Медиана | |

| FC5 8МБ 3600 | 107.8 | 57.2 | 68.0 | 80.9 | 106.0 |

| FC5 16МБ 3600 | 123.0 | 73.2 | 82.1 | 92.7 | 118.0 |

| Прирост, % | 14.1 | 28.0 | 20.8 | 14.5 | 11.3 |

Медианный прирост: 11,3%

WatchDogs 2

Время кадра

Плотность вероятности

Распределение вероятности

| AVG | Low 0.1% | Low 1% | Low 5% | Медиана | |

| FC5 8МБ 3600 | 51.2 | 28.5 | 31.9 | 37.2 | 50.6 |

| FC5 16МБ 3600 | 58.7 | 34.7 | 39.1 | 44.3 | 58.0 |

| Прирост, % | 14.6 | 21.8 | 22.4 | 19.1 | 14.5 |

Медианный прирост: 14.5%

Выводы по играм

Прирост в играх превышает общие значения полученные в бенчмарках (кроме Win-rar) и составляют значения выше 10%, что является довольно значительным показателем.

Видео версия

Общие выводы

Видео на YouTube канале "Этот компьютер"

Кэш-память играет важную роль. Без нее от высокой тактовой частоты процессора не было бы никакого проку. Кэш позволяет использовать в компьютере любую, даже самую "медленную" оперативную память, без ощутимого ущерба для его производительности.

О том, что такое кэш-память процессора, как она работает и какое влияние оказывает на быстродействие компьютера, читатель узнает из этой статьи.

Содержание статьи

Что такое кэш-память процессора

Решая любую задачу, процессор компьютера получает из оперативной памяти необходимые блоки информации. Обработав их, он записывает в память результаты вычислений и получает для обработки следующие блоки. Это продолжается, пока задача не будет выполнена.

Все упомянутые операции производятся на очень высокой скорости. Однако, даже самая быстрая оперативная память работает медленнее любого "неторопливого" процессора. Каждое считывание из нее информации и обратная ее запись отнимают много времени. В среднем, скорость работы оперативной памяти в 16 – 17 раз ниже скорости процессора.

Не смотря на такой дисбаланс, процессор не простаивает и не ожидает каждый раз, когда оперативная память "выдает" или "принимает" данные. Он почти всегда работает на максимальной скорости. И все благодаря наличию у него кэш-памяти.

Кэш-память процессора – это небольшая, но очень быстрая память. Она встроена в процессор и является своеобразным буфером, сглаживающим перебои в обмене данными с более медленной оперативной памятью. Кэш-память часто называют сверхоперативной памятью.

Кэш нужен не только для выравнивания дисбаланса скорости. Процессор обрабатывает данные более мелкими порциями, чем те, в которых они хранятся в оперативной памяти. Поэтому кэш-память играет еще и роль своеобразного места для "перепаковки" и временного хранения информации перед ее передачей процессору, а также возвращением результатов обработки в оперативную память.

Устройство кэш-памяти процессора

Система кэш-памяти процессора состоит из двух блоков - контроллера кэш-памяти и собственно самой кэш-памяти.

Контроллер кэш памяти

Контроллер кэш памяти – это устройство, управляющее содержанием кэша, получением необходимой информации из оперативной памяти, передачей ее процессору, а также возвращением в оперативную память результатов вычислений.

Когда ядро процессора обращается к контроллеру за какими-то данными, тот проверяет, есть ли эти данные в кэш-памяти. Если это так, ядру моментально отдается информация из кэша (происходит так называемое кэш-попадание).

В противном случае ядру приходится ожидать поступления данных из медленной оперативной памяти. Ситуация, когда в кэше не оказывается нужных данных, называется кэш-промахом.

Задача контроллера – сделать так, чтобы кэш-промахи происходили как можно реже, а в идеале – чтобы их не было вообще.

Размер кэша процессора по сравнению с размером оперативной памяти несоизмеримо мал. В нем может находиться лишь копия крошечной части данных, хранимых в оперативной памяти. Но, не смотря на это, контроллер допускает кэш-промахи не часто. Эффективность его работы определяется несколькими факторами:

• размером и структурой кэш-памяти (чем больше ресурсов имеет в своем распоряжении контроллер, тем ниже вероятность кэш-промаха);

• эффективностью алгоритмов, по которым контроллер определяет, какая именно информация понадобится процессору в следующий момент времени;

• сложностью и количеством задач, одновременно решаемых процессором. Чем сложнее задачи и чем их больше, тем чаще "ошибается" контроллер.

Кэш-память процессора

Кэш-память процессора изготавливают в виде микросхем статической памяти (англ. Static Random Access Memory, сокращенно - SRAM). По сравнению с другими типами памяти, статическая память обладает очень высокой скоростью работы.

Впервые кэш размером 8 KB был встроен в процессор Intel i486 в 1989 г.

Однако, эта скорость зависит также от объема конкретной микросхемы. Чем значительней объем микросхемы, тем сложнее обеспечить высокую скорость ее работы.

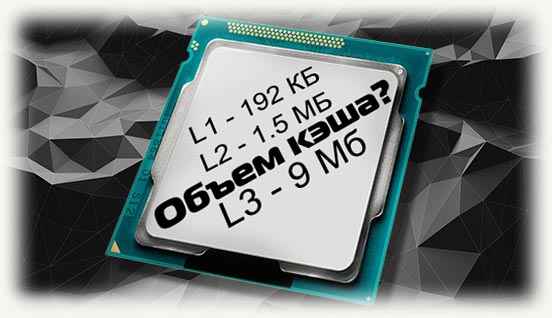

Учитывая указанную особенность, кэш-память процессора изготовляют в виде нескольких небольших блоков, называемых уровнями. В большинстве процессоров используется трехуровневая система кэша:

• Кэш-память первого уровня или L1 (от англ. Level - уровень) – очень маленькая, но самая быстрая и наиболее важная микросхема памяти. Ни в одном процессоре ее объем не превышает нескольких десятков килобайт. Работает она без каких-либо задержек. В ней содержатся данные, которые чаще всего используются процессором.

Количество микросхем памяти L1 в процессоре, как правило, равно количеству его ядер. Каждое ядро имеет доступ только к своей микросхеме L1.

• Кэш-память второго уровня (L2) немного медленнее кэш-памяти L1, но и объем ее более существенный (несколько сотен килобайт). Служит она для временного хранения важной информации, вероятность запроса которой ниже, чем у информации, находящейся в L1.

• Кэш-память третьего уровня (L3) – еще более объемная, но и более медленная схема памяти. Тем не менее, она значительно быстрее оперативной памяти. Ее размер может достигать нескольких десятков мегабайт. В отличие от L1 и L2, она является общей для всех ядер процессора.

Уровень L3 служит для временного хранения важных данных с относительно низкой вероятностью запроса, а также для обеспечения взаимодействия ядер процессора между собой.

Встречаются также процессоры с двухуровневой кэш-памятью. В них L2 совмещает в себе функции L2 и L3.

Влияние кэш-памяти процессора на быстродействие компьютера

При выполнении запроса на предоставление данных ядру, контроллер памяти ищет их сначала в кэше первого уровня, затем - в кэше второго и третьего уровней.

По статистике, кэш-память первого уровня любого современного процессора обеспечивает до 90 % кэш-попаданий. Второй и третий уровни - еще 90% от того, что осталось. И только около 1 % всех запросов процессора заканчиваются кэш-промахами.

Указанные показатели касаются простых задач. С повышением нагрузки на процессор число кэш-промахов увеличивается.

Эффективность кэш-памяти процессора сводит к минимуму влияние скорости оперативной памяти на быстродействие компьютера. Например, компьютер одинаково хорошо будет работать с оперативной памятью 1066 МГц и 2400 МГц. При прочих равных условиях разница производительности в большинстве приложений не превысит 5%.

Пытаясь оценить эффективность кэш-памяти, пользователи чаще всего ищут ответы на следующие вопросы:

Какая структура кэш-памяти лучше: двух- или трехуровневая?

Трехуровневая кэш-память более эффективна.

Чтобы определить, как сильно L3 влияет на работу процессора, сайтом Tom’s Hardware был проведен эксперимент. Заключался он в замере производительности процессоров Athlon II X4 и Phenom II X4. Оба процессора оснащены одинаковыми ядрами. Первый отличается от второго лишь отсутствием кэш-памяти L3 и более низкой тактовой частотой.

Приведя частоты обеих процессоров к одинаковому показателю, было установлено, что наличие кэш-памяти L3 повышает производительность процессора Phenom на 5,8 %. Но это средний показатель. В одних приложениях он был почти равен нулю (офисные программы), в других – достигал 8% и даже больше (компьютерные 3D игры, архиваторы и др.).

Как влияет размер кэша на производительность процессора?

Оценивая размер кэш-памяти, нужно учитывать характеристики процессора и круг решаемых им задач.

Кэш-память двуядерного процессора редко превышает 3 MB. Тем более, если его тактовая частота ниже 3 Ггц. Производители прекрасно понимают, что дальнейшее увеличение размера кэша такого процессора не принесет прироста производительности, зато существенно повысит его стоимость.

В процессорах Intel алгоритм наполнения кэш-памяти построен по так называемой инклюзивной схеме, когда содержимое кэшей верхнего уровня (L1, L2) полностью или частично дублируется в кэше нижнего уровня (L3). Это в определенной степени уменьшает полезный объем его пространства. С другой стороны, инклюзивная схема позитивно сказывается на взаимодействии ядер процессора между собой.

Объем внутренней кэш-памяти некоторых моделей серверных процессоров Intel Xeon

составляет 37,5 MB

В целом же, эксперименты свидетельствуют, что в среднестатистическом "домашнем" процессоре влияние размера кэша на производительность находится в пределах 10 %, и его вполне можно компенсировать, например, высокой частотой.

Эффект от большого кэша наиболее ощутим при использовании архиваторов, в 3D играх, во время кодирования видео. В "не тяжелых" же приложениях разница стремится к нулю (офисные программы, интернет-серфинг, работа с фотографиями, прослушивание музыки и др.).

Многоядерные процессоры с большим кэшем необходимы на компьютерах, предназначенных для выполнения многопоточных приложений, одновременного решения нескольких сложных задач.

Особенно актуально это для серверов с высокой посещаемостью. В некоторых высоконагружаемых серверах и суперкомпьютерах предусмотрена даже установка кэш-памяти четвертого уровня (L4). Изготавливается она в виде отдельных микросхем, подключаемых к материнской плате.

Как узнать размер кэш-памяти процессора?

Существуют специальные программы, предоставляющие подробную информацию о процессоре компьютера, в том числе и о его кэш-памяти. Одной из них является программа CPU-Z.

Программа не требует установки. После ее запуска нужно перейти на вкладку "Caches" (см. изображение).

На примере видно, что проверяемый процессор оснащен трехуровневой кэш-памятью. Размер кэша L3 у него составляет 3 MB, L2 – 512 KB (256x2), L1 – 128 KB (32x2+32x2).

Можно ли как-то увеличить кэш-память процессора?

Как уже было сказано в одном из предыдущих пунктов, возможность увеличения кэш-памяти процессора предусмотрена в некоторых серверах и суперкомпьютерах, путем ее подключения к материнской плате.

В домашних же или офисных компьютерах такая возможность отсутствует. Кэш-память является внутренней неотъемлемой частью процессора, имеет очень маленькие физические размеры и не подлежит замене. А на обычных материнских платах нет разъемов для подключения дополнительной кэш-памяти.

Разрыв между быстродействием процессоров в общем смысле и быстродействием основной памяти DRAM, также в общем смысле, был проблемой в последние 30 лет – в этот период разрыв начал по-настоящему расти. И стоит честно сказать, что инженеры, разрабатывавшие как оборудование, так и программы, создавшие иерархию кэшей и ПО, способное воспользоваться её преимуществами, поступили просто гениально. Это одна из труднейших в реализации архитектур, когда-либо задуманных человеком.

Однако теперь, когда мы находимся на пороге появления постоянно расширяющейся иерархии памяти, когда начинает появляться энергонезависимая память типа Optane 3D XPoint (вариант памяти с изменением фазового состояния) в формате DIMM и SSD, а также новые протоколы (CXL, OpenCAPI, CCIX, NVLink и Gen-Z), возникает вопрос: не пора ли добавить серверам кэш четвёртого уровня? Поскольку от комплекса CPU зависит работа такого количества устройств – некоторые из которых расположены ближе, другие же дальше – логично задуматься над тем, не нужен ли нам ещё один уровень кэша, маскирующий задержки этих других видов памяти и увеличивающий пропускную способность всей системы.

Чтобы представить открывающиеся возможности, мы покопались в своей собственной памяти, а заодно пообщались с разработчиками архитектуры чипов из IBM, Intel, AMD и Marvell, чтобы понять, что они думают об использовании кэша L4 в серверах. Кэш L4, конечно, не новое слово в быстродействии, однако он и не так уж часто встречается в системных архитектурах.

Однако прежде нам стоит пробежаться по истории вопроса.

Добавление кэша первого уровня к процессорам, у которых в то время было всего одно ядро, в 1980-х стало компромиссом, добавляющим задержки в подсистемы памяти, одновременно снижающим среднюю задержку запросов данных и инструкций процессорами. Кэши L1 изначально находились во внешней SRAM, находившейся на материнских платах и подключавшейся к комплексу CPU-память. Такой кэш L1 находился очень близко к процессору, как в смысле тактовой частоты, так и в смысле физического пространства на плате, и давал возможность повысить загрузку CPU. Потом эти кэши разделили, чтобы в одном блоке можно было хранить часто используемые данные, а во втором – популярные инструкции, и это немного увеличило быстродействие. В какой-то момент увеличения тактовой частоты процессоров и соответствующего разрыва в быстродействии CPU и DRAM, были добавлены более жирные, но и более медленные кэши L2 (зато более дешёвые в пересчёте на пропускную способность), опять-таки сначала находившиеся вне корпуса CPU, а потом интегрированные в него. А когда в CPU начали добавлять всё больше и больше ядер, а также всё больше контроллеров DRAM для их загрузки, к иерархии добавили ещё более крупные блоки кэшей L3.

По большей части такая система работала достаточно хорошо. В некоторых схемах CPU мы даже видим определённые практические правила, отражающие уровни иерархии кэшей, которые позволят нам прикинуть возможности, связанные с четвёртым уровнем.

Крис Джианос, инженер чипов и архитектор из Intel, руководившей разработкой многих прошлых поколений процессоров Xeon, объясняет это так: «С каждым уровнем кэша нам обычно нужно, чтобы они выросли достаточно сильно по сравнению с предыдущим уровнем, чтобы всё это имело смысл, поскольку чтобы достичь заметного прироста быстродействия системы, нужно достичь достаточно интересной частоты успешных обращений. Если вы „попадаете“ в кэшированные данные всего в нескольких процентах случаев, это будет сложно заметить. Всё остальное затормаживает ваше быстродействие, и этот прирост будет незаметным. Поэтому требуются относительно большие кэши, и когда речь идёт о более высоких уровнях, нужны реально огромные кэши. Сегодня L2 измеряются мегабайтами, L3 измеряются десятками или сотнями мегабайт. Так что понятно, что если вы начинаете думать о кэше L4, то речь пойдёт уже о сотнях мегабайт, если не о гигабайтах. А такой размер определённо приведёт к их высокой стоимости. Нужно, чтобы сложились определённые условия, чтобы этот вариант стал интересным, и дешёвым он определённо не будет».

Инженеры из компании AMD, с которыми мы беседовали, пожелали остаться неизвестными потому, что они не хотели создать впечатление, что компания собирается добавить кэш L4 в линейку процессоров Epyc – и, если быть точным, AMD ничего такого и не обещала. Однако компания всё же признаёт, что это следующий очевидный шаг для рассмотрения, и, точно так же, как Intel, считает, что все инженеры размышляют о реализации кэша L4. По сути, AMD говорит, что компромиссы, связанные с уровнями кэшей и задержками подробно изучены как в промышленности, так и в научных кругах, и что с каждым новым уровнем, который оказывается больше и медленнее предыдущего, возникает компромисс увеличения общего пути к DRAM. Об этом говорит и Джианос из Intel, рассказывая о необходимости поиска баланса между успешными запросами к КЭШу и его объёмом.

IBM, конечно, добавляла кэш L4 к некоторым своим чипсетам X86 в 2000-х, а в 2010-х добавила L4 к чипсетам NUMA (неравномерный доступ к памяти) на мейнфреймах System z11. У процессора z11 четыре ядра, 64 КБ L1 кэш для инструкций и 128 КБ L1 кэш для данных, плюс 1,5 МБ L2 кэш для каждого из ядер и 24 МБ L3 кэш общего доступа для всех ядер. У чипсета NUMA для z10 было два банка по 96 МБ L4 кэша, то есть, 192 МБ в сумме. Выпустив z12, IBM урезала размер кэша L1 до 98 КБ на ядро, однако увеличила L2 кэш до 2 МБ на ядро, разделив его при этом на две части, для инструкций и для данных, как в случае с L1. Также она удвоила размер кэша L3 до 48 МБ для шести ядер, а размер кэша L4 был увеличен до 384 МБ для пары чипов в чипсете. При смене поколений процессоров System z объёмы кэшей росли, и у процессоров z15, анонсированных в сентябре, пара кэшей L1 будет весить по 128 КБ, пара кэшей L2 – по 4 МБ, а общий кэш L3 будет для 12 ядер иметь объём 256 МБ. Объём кэша L4 в каждом отсеке мейнфрейма составляет 960 МБ, а его общий объём для всей системы, состоящей из пяти отсеков, равняется 4,68 ГБ.

Как мы уже указывали ранее, у процессоров Power8 и Power9 память буферизована, а IBM добавила 16 МБ L4 кэша к каждому буферу Centaur, что составляет 128 МБ L4 кэша на сокет для 32-х планок памяти. У самых дешёвых машин с Power9 нет буфера памяти, а, следовательно, и кэша L4. Архитекторы, разрабатывавшие схему Power10, были заняты разработкой схемы для Power11, и потому не смогли ответить на наши вопросы, но Уильям Старк, управлявший разработкой Power10, нашёл для нас немного времени, и заметил следующее:

«В целом мы пришли к выводу, что кэши последнего уровня большого размера полезны для увеличения быстродействия промышленных систем, — пояснил нам Старк по емейл. – Высокие задержки, связанные с энергонезависимой памятью, в частности, с памятью с изменением фазового состояния, порождают запрос на кэширование – возможно, на кэш типа L4 – в иерархии накопительной памяти».

Именно так мы и думали. И, кстати, мы не утверждаем, что кэш L4 обязательно будет находиться в непосредственной близости от буферизированной памяти будущего DDR5 DIMM. Возможно, его лучше расположить между PCI-Express и кэшем процессора L3, а ещё лучше, в буферах памяти и между PCI-Express и кэшем процессора L3. Возможно, его для этого придётся поместить наверху контроллера I/O и памяти в будущей серверной архитектуре, что немного напоминает технологию Foveros от Intel.

На это возможно взглянуть и с другой точки зрения – допустим, у IBM была возможность менять размеры кристалла, и инженеры решили добавить кэш L4 к шине System z NUMA или к чипу буферизации памяти Power8 и Power9 не ради его самого, а просто потому, что у них оставалась ещё возможность добавить транзисторов после того, как все необходимые функции были реализованы. Иногда нам кажется, что количество ядер в процессорах Intel X86 зависит от размера кэша L3, который они могут себе позволить. Иногда кажется, что Intel назначает максимальный размер кэша L3 на один кристалл, и после этого кристаллы Xeon трёх разных размеров просто изготавливают по этим спецификациям – в последних поколениях у них по 10, 18 или 28 ядер на техпроцессе в 14 нм.

Нет причин для того, чтобы делать кэш L4 исключительно на встроенной DRAM (как делает IBM со своими чипами) или на базе куда как более дорогой SRAM – об этом нам напоминает Рабин Сугумар, архитектор чипов из компаний Cray Research, Sun Microsystems, Oracle, Broadcom, Cavium и Marvell:

«Наши кэши L3 уже достаточно большие, — говорит Сугумар. – Так что L4 в интересующем вас случае нужно делать по другой технологии. Возможно, eDRAM или даже HBM или DRAM. В данном контексте интересным вариантом выглядит реализация кэша L4 на основе HBM, и этот кэш решает не столько проблему задержки, сколько пропускной способности. Поскольку ёмкость HBM ограничена, а пропускная способность велика, мы можем получить определённую прибавку к скорости – и в некоторых специальных случаях мы действительно видим значительное увеличение пропускной способности». Сугумар добавляет, что для довольно большого количества применений наблюдается относительно большое количество «промахов» кэша. Однако нужно подсчитать – будет ли добавление очередного уровня кэша стоить того.

Ещё один возможный вариант использования чего-то наподобие кэша L4, говорит Сугумар, это использовать локальную DRAM в качестве кэша. «У нас не ведётся никаких подобных исследований в лаборатории, но допустим, у нас на чипе есть интерфейс с высокой пропускной способностью, соединенный с общей распределённой памятью где-то на другом конце шлейфа, на расстоянии от 500 нс до 1 мкc. Тогда один из вариантов использования будет создать кэш, перемещающий эти данные из общей распределённой памяти в локальную DRAM. Можно представить работу конечного автомата, управляющего этой памятью, поэтому большую часть времени обращения будут идти к локальной DRAM, и вы сможете минимизировать количество обращений к общей распределённой DRAM».

Нам этот вариант кажется очень интересной разновидностью NUMA. Кстати, Сугумар работал над распределённой памятью для высокоскоростных параллельных систем в Sun Microsystems ещё до того, как появилась энергонезависимая память. И одна из проблем с этими различными вариантами иерархии памяти заключалась в том, что если одна из них потеряется из-за отказа сети или шины, то вся машина упадёт. «В системах с распределённой памятью приходится обрабатывать отказы сети более элегантно, и это порождает множество сложностей при проектировании».

Ещё один момент в том, что нам хочется, чтобы любой кэш высокого уровня, даже не L4, был реализован по максимуму при помощи железа и по минимуму при помощи софта. Ядрам операционок и другому ПО всегда нужно некоторое время, чтобы догнать железо, будь то добавление новых ядер, или кэшей L3 или L4, или адресуемой энергонезависимой памяти.

«В какой-то момент дополнительный уровень кэша станет неизбежностью, — говорит Джианос. – У нас появился первый уровень кэша, и в какой-то момент появился и второй. А потом мы, в конце концов, добавили третий. И когда-то у нас будет четвёртый. Вопрос только – когда и зачем. И мне кажется, что ваши наблюдения, касающиеся возможностей этого кэша, достаточно интересные. Но в Intel пока не решили, когда или зачем будут обнародовать такие вещи. Другие компании тоже изучают этот вопрос; было бы глупо не исследовать его. Рано или поздно это произойдёт, однако скоро это будет, или не очень – пока неясно».

Что это такое

При выполнении любых вычислений (даже в режиме простоя компьютера, когда работают только системные службы) данные для обработки ЦП получает из оперативной памяти. Информация поступает небольшими блоками, после чего записывается промежуточный результат.

По характеристикам, а точнее скорости работы, самый медленный процессор многократно превосходит ОЗУ. В среднем, он шустрее в 15 раз. Добавьте сюда системную шину, которая может еще больше замедлять обработку данных. Получается совсем некрасивая картина: в таком режиме КПД системы слишком низок.

Хотя назначение MB — связать между собой все компоненты компа, часто рациональнее использовать дополнительную «Приблуду», которая возьмет на себя часть несвойственных функций.

Именно к таким технологиям относится кэш, который еще называют сверхоперативной памятью. Реализован он в виде отдельных микросхем типа SRAM. Благодаря такой особенности все промежуточные данные перезаписываются максимально быстро. Это благоприятно влияет на производительность работы в целом.Главная задача кэша — выравнивание дисбаланса скорости передачи данных. Он имеет небольшой объем, так как промежуточные данные сами по себе в памяти много места не занимают.

Контроллер кэша

Это — один из логических блоков. Он отвечает за обмен данными сверх памяти с ядрами ЦП. При обращении одного из ядер контроллер проверяет, есть ли нужные данные в кэше. При положительной проверке происходит так называемое попадание, а необходимая информация «переваривается» внутри самого CPU.

Задача контроллера — сделать так, чтобы промахи происходили как можно реже, то есть чтобы в кэше всегда были необходимые промежуточные данные для обработки. Но это зависит уже не только от CPU, но и от того, как разработчики приложения оптимизировали код.

Последовательность работы следующая: проверка сверх памяти на наличие необходимых данных и их перемещение к одному из ядер, или же обращение к оперативке с аналогичным запросом.

Сверхпамять

В современных процессорах используется многоуровневый кэш. По сравнению с прочими типами ОЗУ SRAM имеет намного большую скорость работы. Однако этот параметр зависит и от объема памяти каждого из таких блоков. По этой причине используется кэш, собранный из нескольких модулей SRAM. Его разделяют на уровни.

- L1. Память первого уровня. Наименьшая по объему, но самая быстрая микросхема. Как правило, не более пары десятков килобайт. Работает почти без задержек. Используется для хранения наиболее часто используемых данных. Количество микросхем обычно равно количеству ядер, а каждое ядро имеет доступ только к своей микросхеме.

- L2. Память второго уровня. Чуть более медленный модуль, но больший по объему (несколько сотен килобайт). Хранит реже используемую информацию.

- L3. Память третьего уровня. Самая медленная, но самая объемная микросхема. Счет уже идет на десятки мегабайт. В отличие от предыдущих, эта память общая для всех ядер. Служит для хранения информации с низкой вероятностью запроса.

Влияние на производительность системы

В современных процессорах количество кэш-попаданий превышает 90%. Это справедливо по отношению к задачам, не требующих высокой производительности. При повышении нагрузки количество промахов увеличивается.

Практика показала, что повышение тактовой частоты влияет лучше на работу системы, чем увеличение кэша. Однако такое решение влечет за собой увеличение стоимости CPU. «Потолок» здесь — 4 ГГц. Дальше каждая десятая доля герца сопряжена с ростом цены в геометрической прогрессии.

Использование трехуровневого кэша увеличивает производительность CPU на 10%. Этот эффект больше всего ощущается при использовании архиваторов (в наше время не самый актуальный софт), при обработке видео и видеоиграх. В «легких» приложениях — например, офисном пакете или интернет-браузере, эффективность кеша чуть более нуля.

Как узнать объем кеша и как его увеличить

Самый простой способ — узнать модель процессора, нажав меню пуск и кликнув ПКМ по значку «Этот компьютер», а затем выбрав пункт «Свойства». Все характеристики «камня» можно найти на официальном сайте производителя.

Увы, но увеличить кеш процессора не получится. Девайс поставляется «как есть» и такому апгрейду не подвергается. Единственный приемлемый способ — купить CPU с большим объемом сверхпамяти.

Также советую почитать «Чем отличается процессор i3 от i5», «Серверный процессор в домашнем компьютере» и «Как устроен процессор внутри». Буду признателен, если вы поделитесь этой публикацией в социальных сетях. До завтра!

Читайте также: