Организация работы и функционирование процессора микропроцессоры типа cisc risc misc презентация

Обновлено: 03.07.2024

Понятие архитектуры процессора не имеет единого толкования, поскольку под ним понимаются две различные сущности. С программной позиции она представляет собой совместимость процессора с конкретным набором команд, его способность выполнять определённый набор кодов. То есть это способность программы, которая была собрана для архитектуры семейства x86, функционировать на всех x86-совместимых системах. На ARM системе такая программа работать не будет.

С аппаратной позиции архитектура процессора, называемая иногда микроархитектурой, является набором свойств, характерным для всего семейства процессоров и отражающим базовые особенности его внутренней организации. К примеру, микроархитектура процессоров Intel Pentium имела обозначение Р5, а процессоры Pentium 4 относились к NetBurst. После закрытия Intel микроархитектуры Р5 для производителей AMD разработала архитектуру К7 и К8 для процессоров Athlon, Athlon XP и Athlon 64 соответственно.

CISC

CISC-архитектура (Complex Instruction Set Computer) относится к процессорам с полным набором команд. Она имеет нефиксированную длину команд, отличается кодированием арифметических действий в единой команде и малым количеством регистров, большинство из которых выполняет только выделенную функцию.

CISC реализована во множестве типов микропроцессоров, таких как Pentium, которые выполняют большое количество разноформатных команд (порядка 200-300), применяя более десяти различных способов адресации. Командная система может включать несколько сотен команд различного уровня сложности или формата (от 1 до 15 байт).

Всё это делает возможным реализовывать эффективные алгоритмы для различных задач. В качестве примеров CISC-архитектуры, используемой преимущественно для десктопных версий, можно привести следующие процессоры:

- x86 (IA-32, сокращенное от "Intel Architecture, 32-bit") - ;

- x86_64 (AMD64);

- Motorola MC680x0;

- мейнфреймы zSeries.

В CISC-процессорах каждую из команд возможно заменить на аналогичную ей либо на группу выполняющих такую же функцию команд. Это формирует как достоинства, так и недостатки архитектуры: она обладает высокой производительностью благодаря возможности замены команд, но большей стоимостью в сравнении с RISC, что связано с усложнённой архитектурой, в которой существует множество сложных для раскодирования команд.

RISC-архитектура (Reduced Instruction Set Computer) относится к процессорам с сокращённым набором команд. В ней быстродействие увеличивается посредством упрощения инструкций: за счёт того, что их декодирование становится проще, уменьшается время исполнения. Изначально RISC-процессоры не обладали инструкциями деления и умножения и не могли работать с числами, имеющими плавающую запятую. Их появление связано с тем, что в CISC достаточно много способов адресации и команд использовались крайне редко.

Система команд в RISC состоит из малого числа часто применяемых команд одного формата, которые можно выполнить за единичный такт центрального процессора. Более сложные и редко применяемые команды выполняются на программном уровне. При этом, благодаря значительному увеличению скорости реализации команд, средняя производительность RISC-процессоров выше, чем у CISC.

Благодаря сокращению аппаратных средств, используемых для декодирования и реализации сложных команд, достигается значительное упрощение и снижение стоимости интегральных схем. В то же время возрастает производительность и снижается энергопотребление, что особенно актуально для мобильного сегмента. Эти же достоинства служат причиной использования во многих современных CISC-процессорах, например в последних моделях К7 и Pentium, RISC-ядра. Сложные CISC-команды заранее преобразуются в набор простых RISC-операций, которые оперативно выполняются RISC-ядром.

Характерными примерами RISC-архитектур являются:

- PowerPC;

- DEC Alpha;

- ARC;

- AMD Am29000;

- серия архитектур ARM;

- Atmel AVR;

- Intel i860 и i960;

- BlackFin;

- MIPS;

- PA-RISC;

- Motorola 88000;

- SuperH;

- RISC-V;

- SPARC.

RISC быстрее CISC, и даже при условии выполнения системой RISC четырёх или пяти команд вместо единственной, выполняемой CISC, RISC выигрывает в скорости, поскольку его команды выполняются в разы оперативнее. Однако CISC продолжает использоваться. Это связано с совместимостью: x86_64 продолжает лидировать в десктоп-сегменте, а поскольку старые программы могут функционировать только на x86, то и новые десктоп-системы должны быть x86(_64), чтобы дать возможность старым программам работать на новых устройствах.

Для Open Source это не проблема, ведь пользователь может найти в сети версию программы, подходящую для другой архитектуры. Однако создать версию проприетарной программы для другой архитектуры получится только у владельца исходного кода.

MISC

MISC-архитектура (Minimal Instruction Set Computer) является процессором с минимальным набором команд. Она отличается ещё большей простотой и используется для ещё большего снижения энергопотребления и итоговой стоимости процессора. MISC-архитектура применяется в IoT-сегменте и компьютерах малой стоимости вроде роутеров. Первой вариацией такого процессора стал MuP21.

В основе MISC-процессоров лежит укладка ряда команд в единое большое слово, что позволяет параллельно обрабатывать несколько потоков данных. MISC применяет стековую модель устройства и базовые слова языка Forth. Процессоры этой архитектуры отличаются малым числом наиболее востребованных команд и использованием длинных командных слов, что позволяет получить выполнение ряда непротиворечивых команд за единый цикл работы процессора. Порядок исполнения команд определяется так, чтобы максимально загрузить маршруты, пропускающие потоки данных.

Все вышеназванные архитектуры могут применять «спекулятивное исполнение команд», то есть исполнение команды заранее, когда ещё неизвестна её необходимость. Это позволяет увеличить производительность.

VLIW

VLIW-архитектура (Very Long Instruction Word) относится к микропроцессорам, применяющим очень длинные команды за счёт наличия нескольких вычислительных устройств. В отдельных полях команды присутствуют коды, которые обеспечивают реализацию различных операций. Одна команда в VLIW может исполнить одновременно несколько операций в разных узлах микропроцессора. Формированием таких длинных команд занимается соответствующий компилятор во время трансляции программ, которые написаны на высокоуровневом языке.

VLIW-архитектура, являясь достаточно перспективной для разработки нового поколения высокопроизводительных процессоров, реализована в некоторых современных микропроцессорах:

- Intel Itanium;

- AMD/ATI Radeon (с R600 до Northern Islands);

- серия «Эльбрус».

VLIW схожа с архитектурой CISC, имея собственный аналог спекулятивной реализации команд. Однако спекуляция выполняется не при работе программы, а при компиляции, что делает VLIW-процессоры устойчивыми к уязвимостям Spectre и Meltdown. Компиляторы в этой архитектуре привязаны к определённым процессорам. Так, в следующем поколении наибольшая длина одной команды может из 256 бит превратиться в 512 бит, и тогда придётся выбирать между обратной совместимостью со старым типом процессора и возрастанием производительности посредством компиляции под новый процессор. И в этом случае Open Sourсe даёт возможность получить программу под определённый процессор при помощи перекомпиляции.

Развитием указанных архитектур стали различные гибридные архитектуры. К примеру, современные x86_64 процессоры CISC-совместимы, однако имеют RISC-ядро. В этих CISC-процессорах CISC-инструкции переводятся в набор RISC-команд. Вероятно, в дальнейшем разнообразие гибридных архитектур только возрастёт.

Помогите другим пользователям — будьте первым, кто поделится своим мнением об этой презентации.

Аннотация к презентации

Содержание

ReducedInstructionSetComputers – компьютер с сокращенным набором команд. RISC-архитектура предполагает реализацию в ЭВМ сокращенного набора команд, что позволяет упростить аппаратуру процессора и повысить его производительность. Набор команд включает простейшие и наиболее часто употребляемые команды, на выполнение которых затрачивается меньше времени. Выполнение более сложных, но редко встречающихся операций обеспечивают подпрограммы. Большинство команд в RISC-процессорах являются быстрыми командами типа «Регистр-регистр», которые выполняются без обращения к ОЗУ. Такие процессоры имеют не более 100 команд, 2-3 простых способа адресации, что ведет к упрощению устройства управления, которое строится по схеме с жесткой логикой. При этом структура процессора настолько упрощается, что становится возможной его реализация на одном кристалле, с оставлением места для увеличения до нескольких сотен числа общих и специализированных регистров. Большое число регистров позволяет до предела сократить число обращений к ОЗУ, за счет: 1)сохранения в регистрах промежуточных результатов; 2)передачи через регистры операндов из одних программ в другие; 3)отказом от передач на сохранение в ОЗУ содержимого регистров при прерываниях программ.

Схема «идеального» RISC-процессора

Принципиально новое, что отличает RISC- от CISC-процессоров – это: отсутствие аппаратного стека – все операнды хранятся в регистрах общего назначения (РОН); отсутствие регистра – счетчика команд; наличие конвейера, позволяющего за один такт процессора осуществлять несколько вычислений; четкое разделение потоков команд (инструкций) и данных; полное равноправие РОН; Кроме этого, в RISC-процессорах имеется: шина операндов и шина результатов (вместо одной внутренней шины микропроцессора в CISC-процессорах 2-го поколения); наличие специального исполнительного устройства, загружающего данные из памяти в РОН (LSU); разделение АЛУ на однотактные (длительность операции в котором занимает один такт процессора) и многотактные (длительность операций в котором превышает один такт); наличие нескольких исполняющих устройств в микропроцессоре. К ним относятся: Однотактные целочисленные АЛУ (S-АЛУ). Многотактныецелочисленные АЛУ (M-АЛУ). Устройства (АЛУ) с плавающей точкой (F-АЛУ). наличие отдельной кэш памяти для инструкций и данных, а также инструментов сегментного/страничного разбиения памяти; общение микропроцессора с шиной только через кэш-память; усложнение УУ, которое, кроме классической предвыборки и дешифрации команд, выполняет и распараллеливание вычислений и направление инструкций на несколько исполняющих модулей; появление основного элемента конвейера – блока предсказания ветвлений (BPU), позволяющего осуществлять распараллеливание вычислений; наличие блока завершения, который подготавливает результаты к записи в оперативную память.

RISC-процессоры 3-го поколения Самыми крупными разработчиками RISC-процессоров считаются SunMicrosystems (архитектура SPARC - Ultra SPARC), IBM (многокристальные процессоры Power, однокристальные PowerPC - PowerPC 620), DigitalEquipment (Alpha - Alpha 21164), MipsTechnologies (семейство Rxx00 -- R 10000), а также Hewlett-Packard (архитектура PA-RISC - PA-8000). Все RISC-процессоры третьего поколения:1. Являются 64-х разрядными и суперскалярными (запускаются не менее 4-х команд за такт);2. Имеют встроенные конвейерные блоки арифметики с плавающей точкой;3. Имеют многоуровневую кэш-память. Большинство RISC-процессоров кэшируют предварительно дешифрованные команды;4. Изготавливаются по КМОП-технологии с 4 слоями металлизации.

Функциональная схема RISC-процессоров

RG является буферным сдвиговым регистром для ALU. Что означает буферный регистр? ALU является комбинационной схемой, поэтому результат, если будет снят операнд со входа, через некоторое время будет изменен, то есть не будет зафиксирован. Поэтому требуется его фиксировать в некотором регистре. мы обязательно должны зафиксировать этот результат в некотором буферном регистре, но попутно он еще выполняет роль сдвигателя. После этого мы подаем этот 32 разрядный результат опять в регистровый файл. То есть делаем так, что результат какой-то операции может быть записан только лишь в регистр. Но мы должны записывать в RF данные считываемые из внешней памяти. Для того чтобы из основной памяти переписать операнд хранящийся по какому-то адресу мы должны использовать тот же вход RF. Как следствие этого мы должны здесь поставить мультиплексор(Мх), который позволяет выбирать нам выход или с двигателя или же с основной памяти. Понятно что ALU формирует признаки результата и на вход его подается некие управляющие сигналы с блока управления. У нас 4 признака результата. Как правило ALU выполняет до 16 каких-то простых операций, поэтому в общем случае мы заведем 4 разряда которые будут определять ту операцию, которая будет выполняться ALU. Ясно,что регистр сдвига должен тоже управляться. Нам для этого потребуются 3 разряда. RF будет тоже управляться и на вход подаются два информационных сигнала: регистр входа А и регистр входа В или С.

Возможно формирование флагов в сдвиговом регистре, поэтому поставим мультиплексор который поможет получить нам как бы объединенные флаги. Получаем 4 разряда флагов, которые идут в УБ. Понятно, что этот мультиплексор управляется типом команды: командой сложения или сдвига. Если команда сложения, флаги идут с одного места, если команда сдвига, то с другого. На вход УБ с «жесткой» логикой работы подается КОП. Далее мы должны реализовать счетчик команд. Он будет реализован следующим образом: УБ будет модифицировать содержимое счетчика в зависимости от кода команды. Содержимое регистра счетчика команд – это РС считывается в УБ и он, в зависимости от того какая команда, или прибавляет 1 к РС или же заменяет его на содержимое регистра В. Поэтому впереди ставим мультиплексор на один из входов которого заводим выход регистрового файла В, а на другой вход выход устройства управления. Далее нам потребуется считывать текущую команду из памяти. Как только она появилась на выходе RF, мы должны ее подать на мультиплексор, образующий шину адреса процессора. Для того чтобы организовать двунаправленную передачу данных по одной и той же шине данных ставим шинный формирователь BD и замкнем эти 2 шины. После этих дополнений шина данных получилась двунаправленная. В итоге получилось необходимость в наличии управляющих сигналов на каждый из перечисленных функциональных блоков. Эти все управляющие сигналы(С1-С10) вырабатываются устройством управления. Также устройством управления вырабатывается шина управления процессором, которая сообщает внешним запоминающим устройствам чтение или запись(один разряд на ЗУК а другой на ЗУД).

Современные RISC-процессоры характеризуются следующим: - упрощенным набором команд; - используются команды фиксированной длины и фиксированного формата, простые способы адресации, что позволяет упростить логику декодирования команд; - большинство команд выполняются за один цикл процессора; - логика выполнения команд с целью повышения производительности ориентирована на аппаратную, а не на микропрограммную реализацию, отсутствуют макрокоманды, усложняющие структуру процессора и уменьшающие скорость его работы; - взаимодействие с оперативной памятью ограничивается операциями пересылки данных; - для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки; - создан конвейер команд, позволяющий обрабатывать несколько из них одновременно; - наличие большого количества регистров; - используется высокоскоростная память.

Области применения RISC-процессоров Современные RISC-процессоры находят применение как: рабочие станции высшего ценового класса (12-15 тысяч долларов). Работают под ОС VMS, Unix; персональные рабочие станции (3-7 тыс. $). ОС: Windows NT, Solaris; серверы; RISC ПК.

Презентация на тему:микропроцессоры Выполнили: Цвирко А.Г. Дыбач Д.Н. гр.106334 Руководитель: Бладыко Ю.В.

За время существования электронная промышленность пережила немало потрясений и революций. Коренной перелом - создание электронных микросхем на кремниевых кристаллах, которые заменили транзисторы и которые назвали интегральными схемами. Со времени своего появления интегральные схемы делились на: малые, средние, большие и ультрабольшие ( МИС, СИС, БИС и УБИС соответственно ). Все больше и больше транзисторов удавалось поместить на всё меньших и меньших по размерам кристаллах. Следовательно ультрабольшая интегральная схема оказывалась не такой уж большой по размеру и огромной по своим возможностям. Поэтому процессоры созданы именно на основе УБИС . Развитие микропроцессоров в электронной индустрии проходило настолько быстрыми темпами, что каждая модель микропроцессора становилась маломощной с момента появления новой модели, а ещё через 2-3 года считалась устаревшей и снималась с производства.

1. Основная часть1.1 Микропроцессор1.1.1 Про микропроцессор Самым главным элементом в компьютере, его "мозгом", является микропроцессор (рис. 1) - небольшая (в несколько сантиметров) электронная схема, выполняющая все вычисления и обработку информации. МП умеет производить сотни различных операций и делает это со скоростью в несколько десятков или даже сотен миллионов операций в секунду. В компьютерах типа IBM PC используются МП фирмы INTEL, а также совместимые с ними МП других фирм. Рис. 1 Микропроцессор

1.2 Функции и строение микропроцессора Функции процессора:обработка данных по заданной программе путем выполнения арифметических и логических операций; программное управление работой устройств компьютера.Рис.1.2 Структурная схема микропроцессора

Модели процессоров включают следующие совместно работающие устройства: Модели процессоров включают следующие совместно работающие устройства:Устройство управления (УУ). Осуществляет координацию работы всех остальных устройств, выполняет функции управления устройствами, управляет вычислениями в компьютере. Арифметико-логическое устройство (АЛУ). Так называется устройство для целочисленных операций. Арифметические операции обрабатываются при помощи АЛУ. Все операции в АЛУ производятся в регистрах - специально отведенных ячейках АЛУ. В процессоре может быть несколько АЛУ. Каждое способно исполнять арифметические или логические операции независимо от других, что позволяет выполнять несколько операций одновременно. Арифметико-логическое устройство выполняет арифметические и логические действия. Логические операции делятся на две простые операции: "Да" и "Нет" ("1" и "0").

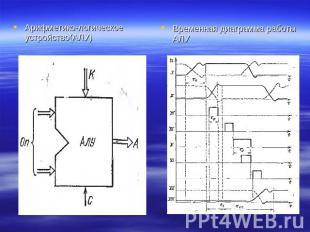

Арифметико-логическое устройство(АЛУ) Временная диаграмма работы АЛУ

Кэш-память. Особая высокоскоростная память процессора. Кэш используется в качестве буфера для ускорения обмена данными между процессором и оперативной памятью, а также для хранения копий инструкций и данных, которые недавно использовались процессором. Кэш первого уровня (L1 cache). Кэш-память, находящаяся внутри процессора. Кэш второго уровня (L2 cache). Также находится внутри процессора. Информация, хранящаяся в ней, но зато по объёму памяти он больше. Основная память. Намного больше по объёму, чем кэш-память, и значительно менее быстродействующая.Шина - это канал пересылки данных, используемый совместно различными блоками системы. Информация передается по шине в виде групп битов. Типы шин:Шина данных. Шина адресов. Шина управления. BTB (Branch Target Buffer) - буфер целей ветвления. В этой таблице находятся все адреса, куда будет или может быть сделан переход.

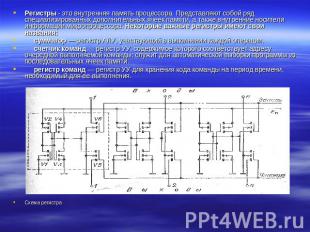

Регистры - это внутренняя память процессора. Представляют собой ряд специализированных дополнительных ячеек памяти, а также внутренние носители информации микропроцессора. Некоторые важные регистры имеют свои названия: сумматор — регистр АЛУ, участвующий в выполнении каждой операции. счетчик команд — регистр УУ, содержимое которого соответствует адресу очередной выполняемой команды; служит для автоматической выборки программы из последовательных ячеек памяти. регистр команд — регистр УУ для хранения кода команды на период времени, необходимый для ее выполнения. Схема регистра

МИКРОПРОЦЕССОР И ЕГО ХАРАКТЕРИСТИКИ.Микpопpоцессоp - это пpоцессоp, pеализованный на полупpоводниковом кpисталле.Основные хаpактеpистики микpопpоцессоpа. 1. Тип микpопpоцессоpа.В зависимости от типа используемого микpопpоцессоpа и опpеделенных им аpхитектуpных особенностей компьютеpа pазличают пять классов ПК: 1. Компьютеpы класса XT; 2. Компьютеpы класса AT; 3. Компьютеpы класса 386; 4. Компьютеpы класса 486; 5. Компьютеpы класса Pentium.2. Тактовая частота микpопpоцессоpа.Тактовая частота микpопpоцессоpа - количество импульсов, создаваемых генеpатоpом за 1 секунду.Влияет на скоpость pаботы микpопpоцессоpа. Чем выше тактовая частота, тем выше его быстpодействие.3. Быстpодействие микpопpоцессоpа.Быстpодействие микpопpоцессоpа - это число элементаpных опеpаций, выполняемых микpопpоцессоpом в единицу вpемени (опеpации/секунда).

4. Разpядность пpоцессоpа.Разpядность пpоцессоpа - максимальное количество pазpядов двоичного кода, котоpые могут обpабатываться или пеpедаваться одновpеменно.5. Аpхитектуpа микpопpоцессоpа. 1. Микpопpоцессоpы с CISC аpхитектуpой.CISC - Complex Instruction Set Computer - Компьютеp со сложной системой команд. Все микpопpоцессоpы фиpмы INTEL относятся к категоpии CISC. 2. Микpопpоцессоpы с RISC аpхитектуpой.RISC - Reduced Instruction Set Computer - Компьютеp с сокpащенной системой команд. 3. Микpопpоцессоpы с MISC аpхитектуpой.MISC - Minimum Instruction Set Computer - Компьютеp с минимальной системой команд. 6. Тип коpпуса микpопpоцессоpа.Микpосхемы совpеменных микpопpоцессоpов могут иметь пластмасовые или кеpамические коpпуса.PQFP - Plastic Quard FlatPack Package- микpопpоцессоpы в коpпусах этого типа впаиваются в системную плату, в pезультате чего замена микpопpоцессоpа становится невозможна.ZIF - Zerro Insertion Force - с нулевым усилием сочленения- такой тип коpпуса имеет специальный зажим, с помощью котоpого они легко изымаются из системной платы с небольшим усилием.PGA - Pin Grid Array- коpпус керамический и имеет позолоченные выводы, что и позволяет очень легко устанавливать его в специальное гнездо.

Наконец о микропроцессорах Познакомившись с конструкциями процессоров, мы снова приходим к выводу, что процессор есть не что иное, как универсальный элемент автоматики, который находит применение каждый раз, когда необходима реализовать алгоритм.

1. Организация работы и функционирование процессора. Микропроцессоры типа CISC, RISC, MISC. Характеристики микропроцессора. Устройство управления, арифметико-логическое устройство.

1. Организация работы и функционирование процессора. Микропроцессоры типа CISC, RISC, MISC. Характеристики микропроцессора. Устройство управления, арифметико-логическое устройство.

Организация работы процессора:

Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода — тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки аппаратного прерывания.

Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора.

В основу было положено понятие потока, под которым понимается последовательность элементов, команд или данных, обрабатываемая процессором. Соответствующая система классификации основана на рассмотрении числа потоков инструкций и потоков данных и описывает четыре архитектурных класса:

· SISD (single instruction stream / single data stream) - одиночный поток команд и одиночный поток данных

· MISD (multiple instruction stream / single data stream) - множественный поток команд и одиночный поток данных.

· SIMD (single instruction stream / multiple data stream) - одиночный поток команд и множественный поток данных.

· MIMD (multiple instruction stream / multiple data stream) - множественный поток команд и множественный поток данных

В основе параллельного компьютера лежит идея использования для решения одной задачи нескольких процессоров, работающих сообща, причем процессоры могут быть как скалярными, так и векторными.

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

· получение и декодирование инструкции (Fetch)

· адресация и выборка операнда из ОЗУ (Memory access)

· выполнение арифметических операций (Arithmetic Operation)

· сохранение результата операции (Store)

После освобождения k-й ступени конвейера она сразу приступает к работе над следующей командой. Если предположить, что каждая ступень конвейера тратит единицу времени на свою работу, то выполнение команды на конвейере длиной в n ступеней займёт n единиц времени, однако в самом оптимистичном случае результат выполнения каждой следующей команды будет получаться через каждую единицу времени

Способность выполнения нескольких машинных инструкций за один такт процессора. Появление этой технологии привело к существенному увеличению производительности.

Основными параметрами процессоров являются:

· коэффициент внутреннего умножения тактовой частоты,

· размер кэш памяти.

Тактовая частота определяет количество элементарных операций (тактов), выполняемые процессором за единицу времени. Тактовая частота современных процессоров измеряется в МГц (1 Гц соответствует выполнению одной операции за одну секунду, 1 МГц=106 Гц). Чем больше тактовая частота, тем больше команд может выполнить процессор, и тем больше его производительность. Первые процессоры, которые использовались в ПК работали на частоте 4,77 МГц, сегодня рабочие частоты современных процессоров достигают отметки в 2 ГГц (1 ГГц=103 МГц).

Разрядность процессора показывает, сколько бит данных он может принять и обработать в своих регистрах за один такт. Разрядность процессора определяется разрядностью командной шины, то есть количеством проводников в шине, по которой передаются команды. Современные процессоры семейства Intel являются 32-разрядными.

Рабочее напряжение процессора обеспечивается материнской платой, поэтому разным маркам процессоров отвечают разные материнские платы. Рабочее напряжение процессоров не превышает 3 В. Снижение рабочего напряжения разрешает уменьшить размеры процессоров, а также уменьшить тепловыделение в процессоре, что разрешает увеличить его производительность без угрозы перегрева.

Коэффициент внутреннего умножения тактовой частоты - это коэффициент, на который следует умножить тактовую частоту материнской платы, для достижения частоты процессора. Тактовые сигналы процессор получает от материнской платы, которая из чисто физических причин не может работать на таких высоких частотах, как процессор. Для получения более высоких частот в процессоре происходит внутреннее умножение на коэффициент 4, 4.5, 5 и больше.

В процессе работы процессор обрабатывает данные, находящиеся в его регистрах, оперативной памяти и внешних портах процессора. Часть данных интерпретируется как собственно данные, часть данных - как адресные данные, а часть - как команды. Совокупность разнообразных команд, которые может выполнить процессор над данными, образовывает систему команд процессора. Чем больше набор команд процессора, тем сложнее его архитектура, тем длиннее запись команд в байтах и тем дольше средняя продолжительность выполнения команд.

Весь ряд процессоров фирмы Intel, устанавливаемых в персональные компьютеры IBM, имеют архитектуруCISC, а процессоры Motorola, используемые фирмой Apple для своих персональных компьютеров, имеют архитектуру RISC. Обе архитектуры имеют свои преимущества и недостатки. Так CISC-процессоры имеют обширный набор команд (до 400), из которых программист может выбрать команду, наиболее подходящую ему в данном случае. Недостатком этой архитектуры является то, что большой набор команд усложняет внутреннее устройство управления процессором, увеличивает время исполнения команды на микропрограммном уровне. Команды имеют различную длину и время исполнения.

RISC-архитектура имеет ограниченный набор команд и каждая команда выполняется за один такт работы процессора. Небольшое число команд упрощает устройство управления процессора. К недостаткам RISC-архитектуры можно отнести то, что если требуемой команды в наборе нет, программист вынужден реализовать ее с помощью нескольких команд из имеющегося набора, увеличивая размер программного кода.

Упрощенная схема процессора, отражающая основные особенности архитектуры микроуровня, приведена на рис. 5. Наиболее сложным функциональным устройством процессора является устройство управления выполнением команд. Оно содержит:

· буфер команд, который хранит одну или несколько очередных команд программы; читает следующие команды из запоминающего устройства, пока выполняется очередная команда, уменьшая время ее выборки из памяти;

· дешифратор команд расшифровывает код операции очередной команды и преобразует его в адрес начала микропрограммы, которая реализует исполнение команды;

· управление выборкой очередной микрокоманды представляет собой небольшой процессор, работающий по принципу фон Неймана, имеет свой счетчик микрокоманд, который автоматически выбирает очередную микрокоманду из ПЗУ микрокоманд;

· постоянное запоминающее устройство (ПЗУ) микрокоманд - это запоминающее устройство, в которое информация записывается однократно и затем может только считываться; отличительной особенностью ПЗУ является то, что записанная в него информация сохраняется сколь угодно долго и не требует постоянного питающего напряжения.

Поступивший от дешифратора команд адрес записывается в счетчик микрокоманд устройства выборки, и начинается процесс обработки последовательности микрокоманд. Каждый разряд микрокоманды связан с одним управляющим входом какого-либо функционального устройства. Так, например, управляющие входы регистра хранения «Сброс», «Запись», «Чтение» соединены с соответствующими разрядами микрокоманды. Общее число разрядов микрокоманды может составлять от нескольких сотен до нескольких тысяч и равно общему числу управляющих входов всех функциональных устройств процессора. Часть разрядов микрокоманды подается на устройство управления выборкой очередной микрокоманды и используется для организации условных переходов и циклов, так как алгоритмы обработки команд могут быть достаточно сложными.

Выборка очередной микрокоманды осуществляется через определенный интервал времени, который, в свою очередь, зависит от времени выполнения предыдущей микрокоманды. Частота, с которой осуществляется выборка микрокоманд, называется тактовой частотой процессора. Тактовая частота является важной характеристикой процессора, так как определяет скорость выполнения процессором команд, и, в конечном итоге, быстродействие процессора. Другими словами тактовая частота показывает количество элементарных операций, выполняемых центральным процессором в секунду. Под элементарной операцией понимается любая простейшая операция типа сложения, пересылки, сравнения и т.д.

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. Функционально АЛУ состоит из нескольких специальных регистров, полноразрядного сумматора и схем местного управления.

Регистры общего назначения (РОН) используются для временного хранения операндов исполняемой команды и результатов вычислений, а также хранят адреса ячеек памяти или портов ввода-вывода для команд, обращающихся к памяти и внешним устройствам. Необходимо отметить, что если операнды команды хранятся в РОН, то время выполнения команды значительно сокращается. Одна из причин, почему программисты иногда обращаются к программированию на языке машинных команд, это наиболее полное использование РОН для получения максимального быстродействия при выполнении программ, критичных по времени.

Основными параметрами процессоров являются: рабочее напряжение, разрядность, рабочая тактовая частота, коэффициент внутреннего умножения тактовой частоты и размер кэш-памяти.

Рабочее напряжение процессора обеспечивает материнская плата, поэтому разным маркам процессоров соответствуют разные материнские платы (их надо выбирать совместно). Ранние модели процессоров x86 имели рабочее напряжение 5 В. С переходом к процессорам Intel Pentium оно понижено до 3,3 В, а в настоящее время составляет менее 3 В. Сверху микропроцессора всегда устанавливают вентилятор (куллер) для его охлаждения во время работы.

Разрядность процессора показывает, сколько бит данных он может принять и обработать в своих регистрах за одни раз (за одни такт) и определяется разрядностью этих регистров. Первые процессоры x86 были 16-разрядными. Начиная с процессора 80386, они имеют 32-разрядную архитектуру. Современные процессоры семейства Intel Pentium остаются 32 разрядными, хотя и работают с 64 разрядной шиной данных.

Обмен данными внутри процессора происходит в несколько раз быстрее, чем обмен с другими устройствами, например, с оперативной памятью. Для того чтобы уменьшить количество обращений к оперативной памяти, внутри процессора создают буферную область - так называемую кэш-память. Это как бы «сверхоперативная память». Когда процессору нужны данные, он сначала обращается в кэш-память, и только если там нужных данных нет, происходит его обращение в оперативную память. Принимая блок данных из оперативной памяти, процессор заносит его одновременно и в кэш-память. Высокопроизводительные процессоры имеют повышенный объем кэш-памяти.

Рассмотрим аппаратную архитектуру физической памяти и организацию управления ею на примере последних поколений процессоров Intel Pentium. Для управления памятью в процессор включен специальный модуль управления памятью, или, иначе, контроллер памяти (Memory Controller). В этом контексте схема обмена данными в компьютерной системе может быть представлена так, как показано на рис. 6. Данная схема отображает обмен данными в компьютерной системе, в которой используется процессор Intel Pentium 4. Все операции по обмену данными с устройствами со стороны процессора выполняет контроллер памяти.

Количество памяти, которая может быть использована программой, ограничено максимальным размером адресного пространства процессора. У процессора Intel Pentium 4, например, максимальное адресное пространство, включая физическую (оперативную) и виртуальную память, может достигать 64 Гбайт.

Процессор Intel Pentium 4 имеет два кэша данных, которые называются кэшем 1-го уровня (L1 Cache) и кэшем 2-го уровня (L2 Cache). Для серверных платформ разработаны модификации процессора, содержащие и кэш 3-го уровня, реализуется на отдельных быстродействующих микросхемах с расположением на материнской плате и имеют объем один и более Мб. Отметим важное обстоятельство - процессоры Intel Pentium 4 имеют также и кэш команд 1-го уровня (он называется Trace Cache), специфика работы которого отличается от особенностей работы кэшей данных.

Для сопоставления большого числа изготовленных и изготовляемых МП существует множество классификационных признаков. Ограничимся самыми главными:

по числу больших интегральных схем (БИС) в микропроцессорном комплекте различают микропроцессоры однокристальные, многокристальные и многокристальные секционные;

по технологии изготовления:

* рМОП - самая простая технология, но не обеспечивает высокого быстродействия МП (в настоящее время устарела);

* nМОП - более сложная технология, которая обеспечивает более высокое быстродействие МП, но не обеспечивает низкое энергопотребление;

* КМОП - самая сложная технология, которая обеспечивает низкое энергопотребление при достаточно высоком быстродействии МП (в настоящее время доминирует);

по ширине ШД (по длине обрабатываемых данных):

* 16-разрядные, применяемые для построения микро-ЭВМ (персональных микро-ЭВМ - ПЭВМ);

* 32-разрядные для построения ПЭВМ высокой производительности;

* секционные - для построения МПС с произвольной шириной ШД;

по виду синхронизации:

* синхронные, когда все процессы в МП и МПС синхронизированы сигналами тактового генератора (МП фирмы Intel);

* асинхронные, когда все процессы в МП и МПС протекают асинхронно (без участия сигналов тактового генератора, МП фирмы DEC);

по способу декодирования и выполнения команд: с использованием жесткой логики или микропрограммно.

Процессоры даже самых простых ЭВМ имеют сложную функциональную структуру, содержат большое количество электронных элементов и множество разветвленных связей. Изменять структуру процессора необходимо так, чтобы полная принципиальная схема или ее части имели количество элементов и связей, совместимое с возможностями БИС. При этом микропроцессоры приобретают внутреннюю магистральную архитектуру, т. е. в них к единой внутренней информационной магистрали подключаются все основные функциональные блоки (арифметико-логический, рабочих регистров, стека, прерываний, интерфейса, управления и синхронизации и др.).

Вырабатывает последовательность внутренних и внешних управляющих сигналов, обеспечивающих выборку и выполнение команд. Устройство управления интерпретирует команду выбранную из программной памяти, и формирует для АЛУ и других устройств требуемый набор команд низкого уровня – микрокоманд.

Микрокоманды задают последовательность элементарных низкоуровневых операций (микроопераций) (пересылка данных, сдвиг данных, установка и анализ признаков, запоминание результатов и т.д.)

Последовательность микрокоманд соответствующая оной команде называется микропрограммой.

В состав управляющего устройства входят три устройства:

1. Регистр команды – содержит код команды во время ее выполнения

2. Программный счетчик – в нем содержится адрес очередной подлежащей выполнению команды.

3. Регистр адреса – в нем вычисляются адреса операндов, находящихся в памяти.

4. Пульт управления – предусмотрен для связи пользователя с ЭВМ и позволяет производить сброс в начальное состояние, просматривать регистры и ячейки памяти, записывать адрес в программный счетчик, пошагово выполнять программу при ее отладке и т.д.

5. Память – устройство предназначено для запоминания, хранения и выборки программ и данных. Она состоит из конечного числа ячеек, каждая из которых имеет свой уникальный адрес (номер), доступ к ячейке осуществляется путем указания ее адреса.

Читайте также: