В формате команд фирмы intel имеется поле постбайт что задает это поле

Обновлено: 07.07.2024

Исходная система команд Intel по утверждению разработчиков использовала всего три формата команд:

Но это лишь лукавый поверхностный взгляд. В поле КОП «спрятались» адреса регистров СОЗУ и быстро выяснялось, что существовало семь «процессорных» форматов поля КОП:

В заштрихованных полях содержатся собственно коды операций АЛУ. Другие обозначения:

DDD – поле приемника результата;

SSS – поле источника операнда;

RP – код регистровой пары;

CCC – указатель условия перехода;

NNN – адрес вектора прерывания.

Далее системы команд Intel развивались очень уродливо: в дело вмешались деньги. Весьма большие: стоимость используемого ПО Intel 8080 уже исчислялась миллиардами долларов.

Большая часть форматов команд процессора приведена на рисунке:

Остановимся на описании полей в форматах команд, содержащих указатели длины операндов, указатели модификации, коды адресных регистров и т.п.

В первом байте команды всегда содержится код операции процессора (КОП), занимающий большее количество разрядов и указатели длины форматов. В отдельных случаях КОП может размещаться в постбайте в поле reg (характерно только для команд с одним операндом).

Функциональное назначение отдельных битов-указателей и битов-признаков таково:

w – признак длины формата данных; при w=0 длина операнда один байт, а при w=1 – машинное слово (два байта);

d - указатель одного из возможных мест запоминания результата операции (характерно только для команд с двумя адресами операндов);

s – признак длины непосредственного операнда в выполняемой команде; s=0 – «длинный» операнд, s=1 – «короткий».

v – указатель количества разрядов, на которое производится сдвиг в соответствующих командах; при v=0 сдвиг производится только на один разряд, а при v=1 – на количество разрядов, указанное в регистре CL (см. рис. 3.1.1.11).

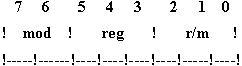

Среди изображенных на рисунке форматов специально обращаем внимание на «длинный» шестибайтовый формат (рис. с литерой (в)), на формат, содержащий шестнадцатиразрядный адрес для команд с прямой адресацией (рис. с литерой (г)), и на формат, используемый в командах условных переходов (рис. с литерой (е)). На том же рисунке показан также формат постбайта, используемого главным образом для задания способа адресации одного или двух операндов. Постбайт содержит поле режима адресации – mod, поле кода регистров – reg и поле регистр/память – r/m, указывающее место размещения второго операнда.

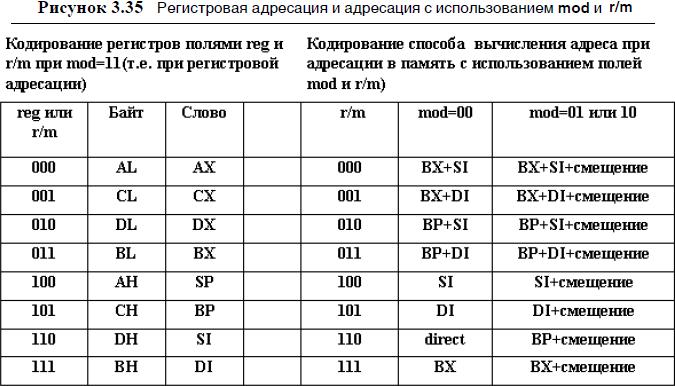

Правило формирования исполнительного адреса по коду в поле r/m показано в таблице 1, причем при (mod)=00 смещение принимается равным нулю (внимание! Имеется одно исключение: при (r/m)=110 исполнительный адрес равен шестнадцатиразрядному смещению, указанному в команде); при (mod)=01 восьмиразрядное смещение, указанное в команде путем расширения знака превращается в шестнадцатиразрядное; при (mod)=10 в команде указывается шестнадцатиразрядное смещение; наконец, при (mod)=11 вторым исполнительным адресом является адрес регистра, кодируемый также, как и первый исполнительный адрес регистра (поле reg), но в поле r/m . Коды регистров в постбайте, а также в поле reg в формате на рис. а, приведены в таблице:

Это необязательный элемент команды. Задает один (для одноадресной команды) или два адреса операндов, один из которых используется и как адрес результата.

| md | reg | r/m |

| Рис. 3.6. Структура постбайта |

Постбайт (рис. 3.6) содержит 3 поля:

· md – поле режима адресации,

· reg – поле адреса регистра,

· r/m – поле адреса второго регистра или кода, определяющего способ вычисления адреса ячейки памяти.

Поле md. Это поле режима адресации.

Задает тип команды:

Для команд типа регистр-память задает процедуру вычисления адреса операнда в памяти:

· md =00 – режим адресации r/m без использования смещения,

· md=01 – режим адресации r/m с использованием смещения 1 байт),

· md =10 – режим адресации r/m с использованием смещения 2 байт),

· md =11 – режим адресации r/r.

Задании md ¹ 11 определяет команду типа регистр-память. В этом случае поле r/r содержит номер РОНа, в котором находится один из операндов, а поле r/m, – номер алгоритма вычисления адреса памяти, по которому хранится адрес второго операнда.

Исключение:

Можно задавать адрес операнда в памяти прямым 16-ти разрядным адресом. Признаком прямой адресации является комбинация значений md=00 и r/m=110 (в табл.1 выделены жирным шрифтом).

Количество байтов смещения disp, расположенных после постбайта, определяется по полю md постбайта.

На рис. 3.7 представлена структура команд МП Intel в реальном режиме и схемы вычисления адресов операндов.

В табл.1. представлены все формулы для вычисления адресов РОНов и ячеек памяти в зависимости от значений полей постбайта: md, reg, r/m.

| Таблица 1.Постбайтовые режимы адресации МП IA-16 | ||||

| Поле r/m | Поле md | |||

| w=0 | w=1 | |||

| DS:[bx + si] | DS:[bx + si + disp(1 байт)] | DS:[bx + si + disp(2 байта)] | al | ax |

| DS:[bx + di] | DS:[bx + di + disp(1 байт)] | DS:[bx + di + disp(2 байта)] | cl | cx |

| SS:[bp + si] | SS:[bp + si + disp(1 байт)] | SS:[bp + si + disp(2 байта)] | dl | dx |

| SS:[bp + di] | SS:[bp + di + disp(1 байт)] | SS:[bp + di + disp(2 байта)] | bl | bx |

| DS:[si] | DS:[si + disp(1 байт)] | DS:[si + disp(2 байта)] | ah | si |

| DS:[di] | DS [di + disp(1 байт)] | DS [di + disp(2 байта)] | ch | di |

| DS:[disp-2 байта] | SS:[bp + disp(1 байт)] | SS:[bp + disp(2 байта)] | dh | bp |

| DS:[bx] | DS [bx + disp(1 байт)] | DS [bx + disp(2 байта)] | bh | bx |

Вопросы для самопроверки:

1. Структура команд в МП IA-16.

2. Назначение префикса в командах МП IA-16.

3. Назначение постбайта в командах МП IA-16.

4. Поля постбайта в командах МП IA-16.

5. Поля постбайта в командах МП IA-16.

6. Тип сегмента используемого по умолчанию при выборке команд в МП IA-16.

7. Тип сегмента используемого по умолчанию при выборке операнда в МП IA-16.

8. Тип сегмента используемого по умолчанию при работе со стеком в МП IA-16.

9. Тип сегмента используемого по умолчанию при работе с командами обработки строк в МП IA-1.

10. Способы замены сегментов, используемых по умолчанию.

11. Назначение постбайта в МП IA-16.

12. Основные поля постбайта в МП IA-16.

13. Назначение поля md постбайта в МП IA-16.

14. Назначение поля reg постбайта в МП IA-16.

Вы здесь: Главная Процессор Кодирование команд в процессоре х86 Кодирование двухоперандной командыАрхитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Кодирование двухоперандной команды

В этой сложной структуре КОП может занимать один или два байта. Адресная часть команды может либо вообще отсутствовать, либо включать в свой состав от одного (ModR/M) до 12 байтов.

Адресная информация, закодированная в такой сложной команде, может содержать следующие сведения:

- сколько операндов использует команда (два, один или ни одного);

- расположен ли операнд в регистре или в памяти;

- если в регистре, то в каком;

- если операнд в команде, сколько для него там отведено места (immеdiate);

- если операнд в памяти, то по какой схеме следует определять его адрес;

- при многокомпонентной адресации, в адресной части может находиться поле для части адреса (displacement);

- и др.

Префикс

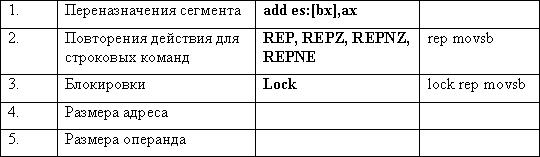

Длина префикса 1 байт. Имеется всего 5 префиксов для Х86

Код операции

КОП — код операции. Длина 1 байт. 0-й бит КОП во многих (но не во всех) командах показывает, производится ли операция со словом (=1) или с байтом (=0). 1-й бит КОП в двухадресных командах указывает, какой из операндов является приемником.

Постбайт адресации

Длина 1 байт. Постбайт адресации показывает, где находятся операнды. Один из операндов (первый) может быть расположен в регистре (регистровая адресация) или в произвольной ячейке ОЗУ (все способы адресации кроме непосредственной). Второй операнд может находиться в теле команды (непосредственная адресация) или в регистре (регистровая адресация). Каждый из операндов может быть как источником, так и приемником (за исключением непосредственной адресации: непосредственный операнд может быть только источником). Структура системы адресации несимметрична.

Поля mod и r/m задают место расположения первого операнда. Поле reg задает положение второго операнда.

Значения поля mod:

11 — операнд в регистре (при остальных mod операнд в ОЗУ, а регистры, на которые указывают поля mod и r/m, содержат компоненты адреса операнда);

10 — смещение два байта (без знака);

01 — смещение один байт (со знаком);

00 — смещение в команде отсутствует.

Смещение

Длина 1 байт (при mod-01) или 2 байта(при mod=10).

Непосредственный операнд

Длина 1 или 2 байта.

Рисунок иллюстрирует различные способы адресации.

В 32-х разрядных процессорах для кодирования расширенных регистров появился в формате после постбайта SIB-байт. Байт SIB включает в себя следующие поля:

Микропроцессор Intel-8086 (К1810ВМ80) имеет двухадресную систему команд [8,10]. Ее особенностью является отсутствие команд, использующих оба операнда из оперативной памяти. Исключение составляют лишь команды пересылки и сравнения цепочек байт или слов, которые в данном пособии рассматриваться не будут. Таким образом, в командах допустимы следующие сочетания операндов: RR , RS , RI , SI . Здесь R обозначает операнд , находящийся в одном из регистров регистровой памяти микропроцессора, S - операнд , находящийся в оперативной памяти, адрес которого формируется по одному из допустимых способов адресации , I - непосредственный операнд , закодированный в адресном поле самой команды. Формат команды во многом определяется способом адресации операнда, находящего в оперативной памяти, длиной используемого непосредственного операнда, а также наличием и длиной смещения, используемого при относительных режимах адресации.

Микропроцессор имеет все режимы адресации, общая схема которых была рассмотрена выше. Естественно, они имеют определенные особенности, присущие данному процессору.

Непосредственная адресация предполагает, что операнд занимает одно из полей команды и, следовательно, выбирается из оперативной памяти одновременно с ней. В зависимости от форматов обрабатываемых процессором данных непосредственный операнд может иметь длину 8 или 16 бит, что в дальнейшем будем обозначать data8 и data16 соответственно.

Адресация оперативной памяти имеет свои особенности, связанные с ее разбиением на сегменты и использованием сегментной группы регистров для указания начального адреса сегмента. 16-разрядный адрес, получаемый в блоке формирования адреса операнда на основе указанного режима адресации, называется эффективным адресом (ЭА). Иногда эффективный адрес обозначается как ЕА ( effective address ). 20-разрядный адрес, который получается сложением эффективного адреса и увеличенного в 16 раз значения соответствующего сегментного регистра , называется физическим адресом (ФА).

Именно физический адрес передается из микропроцессора по 20-ти адресным линиям, входящим в состав системной шины, в оперативную память и используется при обращении к ее ячейке на физическом уровне. При получении эффективного адреса могут использоваться все основные режимы адресации, рассмотренные выше, а также некоторые их комбинации.

Прямая адресация предполагает, что эффективный адрес является частью команды. Так как ЭА состоит из 16 разрядов, то и соответствующее поле команды должно иметь такую же длину.

При регистровой косвенной адресации эффективный адрес операнда находится в базовом регистре BX или одном из индексных регистров DI либо SI :

Обозначение имени регистра в квадратных скобках указывает на содержимое соответствующего регистра. Фигурные скобки - символ выбора одной из нескольких возможных альтернатив.

При регистровой относительной адресации эффективный адрес равен сумме содержимого базового или индексного регистра и смещения:

Эффективный адрес при базово-индексной адресации равен сумме содержимого базового и индексного регистров, определяемых командой:

Форматы двухоперандных команд представлены на рис.6.1. Пунктиром показаны поля, которые в зависимости от режима адресации могут отсутствовать в команде.

Рис. 6.1. Форматы двухоперандных команд микропроцессора I8086

Поле КОП содержит код выполняемой операции . Признак w указывает на длину операндов. При w = 1 операция проводится над словами, а при w = 0 - над байтами. Признак d указывает положение приемника результата. Признак d = 1 , если результат записывается на место операнда, закодированного в поле reg , и d = 0 , если результат записывается по адресу, закодированному полями ( md , r/m ).

Второй байт команды, называемый постбайтом , определяет операнды, участвующие в операции. Поле reg указывает регистр регистровой памяти согласно табл. 6.1

Поля md и r/m задают режим адресации второго операнда согласно табл. 6.2.

Корпорация Intel для использования в РС выпускала микропроцессоры различной разрядности. Наиболее известные из них:

шестнадцатиразрядные микропроцессоры (МП i8086),

двадцатичетырехразрядные микропроцессоры (МП i8286),

тридцатидвухразрядные микропроцессоры (от МП i8386 – до Pentium IV),

шестидесятичетырехразрядные микропроцессоры (Itanium.). Но это уже принципиально новая модель архитектуры EPIC (Explicitly Parallel Instruction Computing – вычисления с явным параллелизмом команд).

Имеется еще расширение архитектуры МП, совместимых c IBM PC, до 64 бит (модели МП Hammer (К-8) корпорации АМD), но это расширение коснулось только формата данных и РОН.

Первые МП корпорация Intel выпускала, находясь в составе корпорации IBM. Программное обеспечение для этих РС производила корпорация Microsoft, также входящая в состав корпорации IBM. По этой причине, когда говорят о МП, используют термин "МП Intel архитектуры (МП IА)" или «МП, совместимые с IBM PC».

В МП этих архитектур можно выделить по режимам работы четыре программные модели:

Реальный режим шестнадцатиразрядного микропроцессора МП i8086,

Защищенный режим работы,

Реальный режим тридцатидвухразрядного микропроцессора,

Виртуальный режим 86.

Реальный режим шестнадцатиразрядного микропроцессора МП i8086

Защищенный режим работы

Это основной 32-разрядный режим работы для 32-разрядных микропроцессоров МП IA (Intel архитектуры). В этом режиме доступны все команды и все архитектурные возможности. Используется механизм виртуальной памяти, все встроенные средства защиты, процедура переключения задач (режим МП IA-32). Дополнительными режимами для них являются реальный и виртуальный 86 (режим V86).

Реальный режим 32-разрядного микропроцессора

Это 16-разрядный режим адресации и обработки данных с прямым обращением к памяти. Режим эмулирует программную среду (модель) МП 8086 с некоторыми дополнительными возможностями, включая новые РОНы, часть новых команд и расширений как адресов, так и данных. Но в любом случае, 32-разрядное смещение в сегменте не должно превышать значения 65 535 (64 Кбайт).

При запуске или перезагрузке МП устанавливается именно реальный режим. Он используется для подготовки программной среды для работы в защищенном режиме.

Виртуальный режим 86

Это разновидность формы эмуляции модели 8086. Здесь нет прямой адресации памяти. В этом режиме применяются механизмы защиты и виртуальной памяти. Виртуальный режим 86 устанавливается из защищенного (для запуска программ, написанных для реального режима) с возможностью возврата в защищенный режим.

Вопросы для самопроверки:

1. Характеристики защищенного режима работы МП, возможности использования разрядности операндов и других средств архитектуры.

2. Характеристика реального режима работы МП, назначение режима, возможности использования разрядности операндов и других средств архитектуры.

3. Характеристика виртуального режима 86, назначение режима и возможности использования разрядности операндов и других средств архитектуры.

3.2. Программная модель 16-ти битового микропроцессора МП IA-16

3.2.1. Модель памяти

Одна из особенностей МП Intel – это использование сегментированной памяти. Полнокровное развитие персональных ЭВМ (PC) началось с появления 16-разрядных микропроцессоров. Изначально микропроцессоры предназначались для управляющих систем. Персональные ЭВМ проектировались для широкого круга пользователей как максимально дешевых индивидуальных (одна для одного) ЭВМ для эксплуатации без посредников (профессиональных программистов). Для этого они должны были быть снабжены определенными средствами программирования на основе простейших языков программирования (типа Бейсик), управляющей (операционной) программной системой и простейшими офисными системами: текстовыми редакторами, электронными таблицами и т.д.

16-разрядная адресация позволяла адресовать только 2 16 = 65 536 байт (64 Кбайт). Этого было достаточно для управляющих ЭВМ, но не для PC. Вероятно, по этой причине была выбрана модель структурированной математической памяти ( Рис. 3.1.), состоящая из 16 сегментов по 65 536 байт (64 Кбайт). Этот прием позволил увеличить адресное пространство математической памяти в реальном режиме до 2 20 = 1 048 576 (1 Мбайт).

При этом первые 10 сегментов определялись как память пользователей, а остальные 6 сегментов – как системные (для операционной системы). Кроме этого, вводился еще один дополнительный сегмент (64 Кбайт) для адресации портов. Порты – это программно-доступные (адресуемые) регистры контроллеров устройств ввода-вывода. Это отдельное (дополнительное) адресное пространство процессора.

Биты в памяти, как и в регистрах, нумеруются с младших разрядов. Многобайтные операнды адресуются по номеру младшего байта. Размещение программных объектов без соблюдения правил целочисленных границ не рекомендуется

Использование сегментированной математической памяти для расширения адресного пространства имеет и отрицательные стороны. Это несоответствие адресных структур математической и физической (линейной) памяти.

При каждом обращении к физической памяти необходима процедура преобразование адреса обращения из адреса сегментированной математической памяти в адрес линейной физической памяти. Это процедура трансляции сегмента.

Процедура трансляции сегментов заключается в вычислении адреса линейной, плоской физической оперативной памяти по адресу сегмента и смещению в сегменте.

Вопросы для самопроверки:

1. Понятие сегментированной памяти.

2. Размер сегмента в МП IA-16.

3. Максимальное число сегментов в МП IA-16.

4. Процедура трансляции сегментов в МП IA-16.

5. Место хранения базовых адресов сегментов.

3.2.2. Порты ввода/вывода

МП позволяет адресовать порты в адресном пространстве портов (64 Кб) и адресном пространстве оперативной памяти.

Для адресации портов используются команды IN, INS (для ввода) и OUT, OUTS (для вывода), а для адресации ячеек памяти – любые адресные команды.

Для доступа к порту ввода/вывода, расположенному в адресном пространстве памяти могут использоваться любые работающие с памятью команды. Это дает некоторую гибкость работы с портами. Например, команда MOV позволяет пересылать данные между портом и любым регистром. Команды AND, OR, и TEST позволяют манипулировать с отдельными битами управляющих регистров портов при программировании процедур ввода/вывода. Сегменты логической памяти, порты ввода/вывода и их отображение (возможное размещение) в памяти представлены на рис. 3.1.

Если при отображении портов на адресное пространство памяти используется сегментация, то поля AVL в дескрипторах сегментов позволяют отметить сегменты как неперемещаемые и не подлежащие подкачке.

Все сегменты (включая сегменты портов) в плоской памяти задаются двумя независимыми параметрами: сегментом (базовый адрес сегмента) и адресом объекта в сегменте (смещением в сегменте).

Адресное пространство портов:

2 16 = 65 536 однобайтных портов с нумерацией от 0 до 65 535 или

2 15 = 32 768 двухбайтных портов с нумерацией от 0 до 65 534 или

2 14 = 16 384 четырехбайтовых портов с нумерацией от 0 до 65 532.

В командах ввода/вывода адреса портов от 1 до 255 могут задаваться прямыми адресами:

IN al, 24 – ввод байта из 24-го порта в регистр al,

IN ax, 24 – ввод слова из 24-го порта в регистр ax,

IN eax, 24 – ввод двойного слова из 24-го порта в регистр eax,

Задание в командах портов с адресами больших 255 производится с использованием регистра dx:

MOV dx, 1024 ;засылка адреса порта в dx

IN al, dx ;ввод байта из 1024-го порта в регистр al,

IN ax, 24 ;ввод слова из 1024-го порта в регистр ax,

Вопросы для самопроверки:

1. Понятие портов.

2. Методы адресации портов.

3. Адресация портов в МП IA.

4. Команды обращения к портам в МП IA-16.

2.2.3. Регистровый файл

Регистровый файл МП IA-16 содержит 14 пользовательских регистров:

регистры общего назначения (РОНы) – 8 регистров,

сегментные регистры – 4 регистра,

указатель команд – 1 регистр,

регистр состояния (флагов) – 1 регистр.

Все эти регистры в той или иной степени доступны программам пользователей.

Регистры общего назначения

РОНы МП Intel (Рис.3.2) не являются классическими регистрами общего назначения. Они могут задаваться и явными адресами, и по умолчанию (кодом операции, постбайтом и т.д.).

C точки зрения использования регистров по умолчанию, они делятся на две группы:

регистры данных – ax, cx, dx и bx (по возрастанию адресов),

регистры адресов – sp, bp, si и di (по возрастанию адресов).

Регистр bx, хоть его и относят к группе регистров данных, является и одним из регистров адреса базы данных (для сегмента DS).

Регистр dx может использоваться в качестве адресного регистра портов в командах ввода/вывода.

Регистры cx, si и di по умолчанию используются при обработке строк.

При работе с 16-разрядными операндами и компонентами адреса используются 16-разрядные РОНы – ax, cx, dx, bx, sp, bp, si и di (по возрастанию адресов).

При использовании сегментированной математической памяти необходима процедура преобразования адреса сегментированной (математической) памяти в адреса линейной физической памяти при каждом обращении к памяти.

Адрес объекта в сегментированной памяти задается двумя компонентами: базовым адресом сегмента и смещением в сегменте. В команде задается только смещение в сегменте. Базовый адрес сегмента задается содержимым одного из четырех сегментных регистров (рис. 3.3).

МП IA-16 содержали четыре 16-разрядных сегментных регистра:

ES – регистр дополнительного сегмента данных,

CS – регистр сегмента кода,

SS – регистр сегмента стека,

DS – регистр сегмента данных,

Емкость физической памяти в МП IA-16 позволяет разместить одновременно до 16 полных сегментов по 64 Кбайт (2 16 байт). Но одновременно, без изменения содержимого сегментных регистров, в реальном режиме IA-16 можно обращаться только к четырем сегментам, по числу сегментных регистров.

Обращатся к другим сегментам (кроме кодовых сегментов), размещенным в оперативной памяти можно:

при помощи загрузки базовых адресов в соответствующие сегментные регистры командами пересылки (mov ),

при помощи команд загрузки сегментных регистров (LES, LDS и LSS).

Все операции со стеком ориентированы на словарную организацию стека. По этой причине адрес указателя стека и базовый адрес сегментного регистра SS должны быть четными.

Переходы на новые кодовые сегменты производятся командами межсегментных передач управления.

Преобразование адреса сегментированной памяти в адрес линейной (плоской) памяти производится процедурой трансляции сегмента: сложением базового адреса сегмента с адресом операнда в сегменте .

Но сегментные регистры - 16-битные, а базовые адреса должны быть 20- битными. Поэтому при использовании сегментных регистров их содержимое умножается на 16 добавлением четырех нулей после младшего разряда

Таким образом, адрес в сегменте математической памяти МП IA-16 задается тремя компонентами: B (база), X (индекс) и disp (смещение).

Для вычисления адреса обращения к физической памяти (при сегментированной структуре математической памяти) требуются, по крайней мере, две процедуры:

вычисление прямого адреса в сегменте по компонентам (В), (Х) и disp,

преобразование адреса в сегменте сегментированной памяти в адрес линейной физической памяти .

Результатом первого преобразования адреса является получение одной компоненты логического адреса – смещения в сегменте, результатом второго преобразования – получение смещения в линейной памяти .

Для уменьшения неопределенности при использовании вышеописанных смещений используют термины:

disp – для обозначения смещения в кадре сегмента,

offset – для обозначения смещения в сегменте,

линейный адрес – для обозначения адреса (смещения) в линейной (не сегментированной) памяти.

Схема вычисления смещения в сегменте (offset) по компонентам адреса, включая смещение в кадре сегмента (disp) и трансляцию сегмента (вычисление линейного адреса в несегментированной памяти) представлена на рис.3.4.

Трансляция сегментов связана с проблемой 20-й адресной шины оперативной памяти. Эта проблема заключается в следующем.

Максимальный адрес сегмента, который может быть записан с сегментный регистр (с учетом четырех нулей в младших разрядах) составляет А max = 2 20 -2 4 –1. При использовании этого адреса как базового адреса сегмента, в оставшиеся ячейки памяти можно будет записать только 16 слов. В МП с 20-разрядной адресной шиной остальные данные сегмента запишутся в ячейки оперативной памяти, начиная с нулевого адреса.

В МП IA-32 при работе в реальном режиме (эмуляции МП IA-16) приходится учитывать это явление, используя прием (заворота) 20-й шины адреса

В защищенном режиме, если включен механизм виртуальной памяти, происходит еще одно преобразование адреса – трансляция страниц.

В (МП IA-16 ) – трансляция страниц (виртуальная память) не реализована.

Указатель команд IP.

Это 16-ти битный регистр – счетчик, вычисляющий адрес следующей команды (в кодовом сегменте) по числу байт в текущей команде. Программе указатель команд доступен только частично по командам передачи управления. В начальное состояние IP устанавливается автоматически при включении процессора. Прямой доступ к IP по записи или чтению не предусмотрен (но возможен доступ к содержимому IP после его копирование в стеке).

Регистр состояния (флагов).

Это 16-разрядный регистр, в котором сгруппированы управляющие сигналы режимов работы основных систем процессора и флаги кодов условий для условных команд передач управления.

Флаги кодов условий передач управления:

CF – арифметический перенос в старшие разряды,

PF – четность (наличие четности кода результата),

AF – дополнительный (десятичный) перенос из младшей тетрады,

ZF – нулевой результат,

SF – знак результата (для дополнительного кода),

TF – трассировка (прерывание после выполнения каждой команды для работы в режиме отладки программы),

IF – разрешение прерывания,

DF – направление обработки строк.

Вопросы для самопроверки:

1. Основные группы пользовательских регистров.

2. Группа регистров данных в составе РОН МП IA-16.

3. Группа регистров адресов в составе РОН МП IA-16.

4. Предназначение регистра IP в МП IA-16.

5. Предназначение регистра F (флагов) в МП IA-16.

6. Основные биты кода условий передачи управления в регистра F (флагов).

7. Назначение сегментных регистров в МП IA-16.

8. Число сегментных регистров в МП IA-16.

9. Спецификации сегментных регистров в МП IA-16.

10. Команды загрузки сегментных регистров в МП IA-16.

11. Причины использования задания адреса в сегменте тремя компонентам.

12. Компоненты адреса, используемые при задании адресов объектов в сегменте памяти.

13. Компонента disp при задании адреса в МП IA.

14. Компонента offset при задании адреса в МП IA.

15. Термин "линейный адрес" при задании адреса в МП IA.

16. Процедура трансляции сегмента при обращении к памяти в МП IA-16.

3.2.4. Структура команд.

Имеется две формы представления машинных команд:

на языке программирования машинного уровня (ассемблере),

на аппаратном уровне с использованием битовых кодов. Перекодировку команд производит ассемблер совместно с рядом программ операционной системы.

Команды на языке ассемблера .

На языке ассемблера команды содержат символьный код операции и один или два адреса. Команды могут быть одноадресными или двухадресными. Первый адрес в команде – адрес приемника, второй – источника. Оба адреса могут быть адресами РОНов, Адресом оперативной памяти может быть только один.

команды обработки строк (адреса приемника и источника задаются парами регистров – сегментный регистр:индексный регистр)

команды работы со стеком, которые перемещают данные из памяти в стек, который также находится в памяти.

Адрес оперативной памяти может задаваться прямым адресом (offset) или компонентами (D, X, disp).

Примеры команд на языке ассемблера:

;копирование в ax содержимого ячейки памяти в сегменте CS по адресу, равному сумме содержимого регистра bx и смещения – 356,

4.mov ax, [bp +si+356]

;копирование в ax содержимого ячейки памяти по адресу, равному сумме содержимого регистров bp, si и смещения 356,

5.mov ax, byte ptr z

; копирование в ax содержимого ячейки памяти по адресу z (конструкция byte ptr z уточняет, что адрес z является адресом одного байта, а не слова).

Машинная кодировка команд IA – 16.

МП IA-16 используют команды переменного формата от 1 до 7 байт. Кодировка команд производилась с учетом частоты использования команды в типовых программах.

Читайте также: