Как обозначается линии прерывания персонального компьютера

Обновлено: 07.07.2024

Прерывание - это прекращение выполнения текущей команды или текущей последовательности команд для обработки некоторого события специальной программой - обработчиком прерывания , с последующим возвратом к выполнению прерванной программы. Событие может быть вызвано особой ситуацией, сложившейся при выполнении программы, или сигналом от внешнего устройства. Прерывание используется для быстрой реакции процессора на особые ситуации, возникающие при выполнении программы и взаимодействии с внешними устройствами.

Механизм прерывания обеспечивается соответствующими аппаратно-программными средствами компьютера.

Любая особая ситуация, вызывающая прерывание , сопровождается сигналом, называемым запросом прерывания (ЗП). Запросы прерываний от внешних устройств поступают в процессор по специальным линиям, а запросы , возникающие в процессе выполнения программы, поступают непосредственно изнутри микропроцессора. Механизмы обработки прерываний обоих типов схожи. Рассмотрим функционирование компьютера при появлении сигнала запроса прерывания , опираясь в основном на обработку аппаратных прерываний (рис. 14.1).

Рис. 14.1. Выполнение прерывания в компьютере: tр - время реакции процессора на запрос прерывания; tс - время сохранения состояния прерываемой программы и вызова обработчика прерывания; tв - время восстановления прерванной программы

После появления сигнала запроса прерывания ЭВМ переходит к выполнению программы - обработчика прерывания . Обработчик выполняет те действия, которые необходимы в связи с возникшей особой ситуацией. Например, такой ситуацией может быть нажатие клавиши на клавиатуре компьютера. Тогда обработчик должен передать код нажатой клавиши из контроллера клавиатуры в процессор и, возможно, проанализировать этот код. По окончании работы обработчика управление передается прерванной программе.

Время реакции - это время между появлением сигнала запроса прерывания и началом выполнения прерывающей программы (обработчика прерывания ) в том случае, если данное прерывание разрешено к обслуживанию.

Время реакции зависит от момента, когда процессор определяет факт наличия запроса прерывания . Опрос запросов прерываний может проводиться либо по окончании выполнения очередного этапа команды (например, считывание команды, считывание первого операнда и т.д.), либо после завершения каждой команды программы.

Первый подход обеспечивает более быструю реакцию, но при этом необходимо при переходе к обработчику прерывания сохранять большой объем информации о прерываемой программе, включающей состояние буферных регистров процессора, номера завершившегося этапа и т.д. При возврате из обработчика также необходимо выполнить большой объем работы по восстановлению состояния процессора.

Во втором случае время реакции может быть достаточно большим. Однако при переходе к обработчику прерывания требуется запоминание минимального контекста прерываемой программы (обычно это счетчик команд и регистр флагов). В настоящее время в компьютерах чаще используется распознавание запроса прерывания после завершения очередной команды.

Время реакции определяется для запроса с наивысшим приоритетом .

Глубина прерывания - максимальное число программ, которые могут прерывать друг друга. Глубина прерывания обычно совпадает с числом уровней приоритетов , распознаваемых системой прерываний . Работа системы прерываний при различной глубине прерываний ( n ) представлена на рис. 14.2. Здесь предполагается, что с увеличением номера запроса прерывания увеличивается его приоритет .

Рис. 14.2. Работа системы прерываний при различной глубине прерываний

Без учета времени реакции , а также времени запоминания и времени восстановления:

Сегодня мы поговорим о прерываниях процессоров семейства x86 (-64). Подробнее под катом.

Прерывания — это как бы сигнал процессору, что надо прервать выполнение (их поэтому и назвали прерываниями) текущего кода и срочно сделать то, что указано в обработчике.

- 0b0101: 32-битный гейт задачи, при появлении такого прерывания происходит хардверное переключение задачи (да-да, есть и такое, но его уже давно не используют)

- 0b0110: 16-битный гейт прерывания

- 0b0111: 16-битный гейт trap'a (я не знаю, как это перевести на русский язык, извините)

- 0b1110: 32-битный гейт прерывания

- 0b1111: 32-битный гейт trap'a

- Поиск вектора №0 в IDT.

- Сравнение уровня привилегий дескриптора и текущего уровня привилегий процессора.

- Если текущий уровень привилегий процессора меньше уровня привилегий дескриптора, то просто вызвать генеральную ошибку защиты и не вызывать прерывание.

- Происходит сохранение адреса возвращения, регистра (E)FLAGS и другой информации.

- Происходит переход на адрес, указанный в векторе №0 IDT.

- После выполнения обработчика инструкция iret возвращает управление прерванному коду.

Существует особый тип прерываний — IRQ (Interrupt ReQuest), или же аппаратные прерывания, но я буду их для краткости называть просто IRQ. Технически они почти не отличаются от любых других прерываний, но генерируются не процессором или самим кодом, а устройствами, подключенными к компьютеру. К примеру, IRQ №0 генерируется PIT (таймер с программируемым интервалом), IRQ 1 генерируется при нажатии клавиши на клавиатуре, а IRQ 12 — при действии с PS/2-мышью.

Еще есть так называемые программные прерывания. Их, как понятно из названия, программа должна вызывать сама — никто их за нее не вызывает. Таковыми являются, например, системные вызовы в некоторых системах. В Linux, например, они висят на векторе 0x80. Во многих хобби-ОС они тоже висят на векторе 0x80. Теперь немного отсебятины — я думаю, что сисвызовы сделаны в виде прерываний из-за того, что 1) их так очень легко вызывать, 2) их можно вызвать из любого кода, работающего в ОС — IDT-то одна на всю систему.

Информация взята с OSDev Wiki.

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

- Арифметико логическое устройство (АЛУ)

- Страничный механизм в процессорах 386+. Механизм трансляции страниц

- Организация разделов на диске

- Диск Picture CD

- White Book/Super Video CD

- Прямой доступ к памяти, эмуляция ISA DMA (PC/PCI, DDMA)

- Карты PCMCIA: интерфейсы PC Card, CardBus

- Таблица дескрипторов прерываний

- Разъемы процессоров

- Интерфейс Slot A

Аппаратные прерывания в PC-совместимых компьютерах

Устройства PCI имеют возможность сигнализации об асинхронных событиях с помощью прерываний. На шине PCI возможны четыре типа сигнализации прерываний:

В данной главе рассматриваются все эти типы сигнализации, а также общая картина поддержки аппаратных прерываний в PC-совместимых компьютерах.

Аппаратные прерывания в PC-совместимых компьютерах

Аппаратные прерывания обеспечивают реакцию процессора на события, происходящие асинхронно по отношению к исполняемому программному коду. Напомним, что аппаратные прерывания делятся на маскируемые и немаскируемые. Процессор x86 по сигналу прерывания приостанавливает выполнение текущего потока инструкций, сохраняя в стеке состояние (флаги и адрес возврата), и выполняет процедуру обработки прерывания. Конкретная процедура обработки выбирается из таблицы прерываний по вектору прерывания — однобайтному номеру элемента в данной таблице. Вектор прерывания доводится до процессора разными способами: для немаскируемого прерывания он фиксирован, для маскируемых прерываний его сообщает специальный контроллер прерываний. Кроме аппаратных прерываний у процессоров x86 имеются также внутренние прерывания — исключения (exceptions), связанные с особыми случаями выполнения инструкций, и программные прерывания. Для исключений вектор определяется самим особым условием, и под исключения фирмой Intel зарезервированы первые 32 вектора (0–31 или 00–1Fh). В программных прерываниях номер вектора содержится в самой инструкции (программные прерывания — это лишь специфический способ вызова процедур по номеру, с предварительным сохранением в стеке регистра флагов). Все эти прерывания используют один и тот же набор из 256 возможных векторов. Исторически сложилось так, что векторы, используемые для аппаратных прерываний, пересекаются с векторами исключений и векторами для программных прерываний, используемых для вызовов сервисов BIOS и DOS. Таким образом, для ряда номеров векторов процедура, на которую ссылается таблица прерываний, должна в начале содержать программный код, определяющий, по какому поводу она вызвана: из-за исключения, аппаратного прерывания или же для вызова какого-то системного сервиса. Таким образом, процедура, собственно и обеспечивающая реакцию процессора на то самое асинхронное событие, будет вызвана только после ряда действий по идентификации источника прерываний. Здесь еще заметим, что один и тот же вектор прерывания может использоваться и несколькими периферийными устройствами — это так называемое разделяемое использование прерываний, которое подробно обсуждается ниже.

Вызов процедуры обслуживания прерываний в реальном и защищенном режимах процессора существенно различается:

Номера векторов, используемых для аппаратных прерываний в операционных системах защищенного режима, отличаются от номеров, используемых в ОС реального режима, чтобы исключить их конфликты с векторами, используемыми для исключений процессора.

Реакция процессора на маскируемые прерывания может быть задержана сбросом его внутреннего флага IF (инструкция CLI запрещает прерывания, STI — разрешает). Маскируемые прерывания используются для сигнализации о событиях в устройствах. По возникновении события, требующего реакции, адаптер (контроллер) устройства формирует запрос прерывания, который поступает на вход контроллера прерываний. Задача контроллера прерываний — довести до процессора запрос прерывания и сообщить вектор, по которому выбирается программная процедура обработки прерываний.

Процедура обработки прерывания от устройства должна выполнить действия по обслуживанию данного устройства, включая сброс его запроса для обеспечения возможности реакции на следующие события, и послать команды завершения в контроллер прерываний. Вызывая процедуру обработки, процессор автоматически сохраняет в стеке значение всех флагов и сбрасывает флаг IF, что запрещает маскируемые прерывания. При возврате из этой процедуры (по инструкции IRET) процессор восстанавливает сохраненные флаги, в том числе и установленный (до прерывания) IF, что снова разрешает прерывания. Если во время работы обработчика прерываний требуется реакция на иные прерывания (более приоритетные), то в обработчике должна присутствовать инструкция STI. Особенно это касается длинных обработчиков; здесь инструкция STI должна вводиться как можно раньше, сразу после критической (не допускающей прерываний) секции. Следующие прерывания того же или более низкого уровня приоритета контроллер прерываний будет обслуживать только после получения команды завершения прерывания EOI (End Of Interrupt).

В IBM PC-совместимых компьютерах применяется два основных типа контроллеров прерываний:

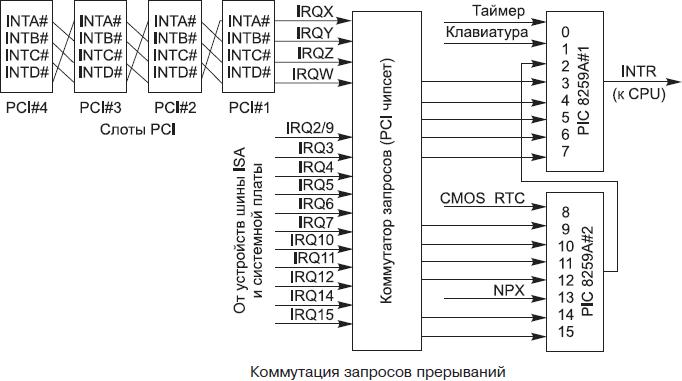

Традиционная схема формирования запросов прерываний с использованием пары PIC изображена на рисунке ниже.

На входы контроллеров прерываний поступают запросы от системных устройств (клавиатура, системный таймер, CMOS-таймер, сопроцессор), периферийных контроллеров системной платы и карт расширения. Традиционно все линии запросов, не занятые перечисленными устройствами, присутствуют на всех слотах шины ISA/ EISA. Эти линии обозначаются как IRQx и имеют общепринятое назначение (см. таблицу ниже). Часть этих линий отдается в распоряжение шины PCI. В таблице отражены и приоритеты прерываний — запросы расположены в порядке их убывания. Номера векторов, соответствующих линиям запросов контроллеров, система приоритетов и некоторые другие параметры задаются программно при инициализации контроллеров. Эти основные настройки остаются традиционными для обеспечения совместимости с программным обеспечением, но различаются для ОС реального и защищенного режимов. Так, например, в ОС Windows базовые векторы для ведущего и ведомого контроллеров — 50h и 58h соответственно.

*1 Запросы прерываний 0, 1, 8 и 13 на шины расширения не выводятся.

*2 Указаны номера векторов при работе в реальном режиме процессора.

*3 Указаны номера векторов при работе в ОС Windows.

Каждому устройству, для поддержки работы которого требуются прерывания, должен быть назначен свой номер прерывания. Назначения номеров прерываний выполняются с двух сторон: во-первых, адаптер, нуждающийся в прерываниях, должен быть сконфигурирован на использование конкретной линии шины (джамперами или программно). Во-вторых, программное обеспечение, поддерживающее данный адаптер, должно быть проинформировано о номере используемого вектора. В процессе назначения прерываний может участвовать система PnP для шин ISA и PCI, для распределения линий запросов между шинами служат специальные параметры CMOS Setup. Современные ОС имеют возможность изменить назначение запросов относительно распределения, сделанного через CMOS Setup.

После того как произведено конфигурирование системы прерываний (проинициализирован контроллер прерываний, устройствам назначены линии запросов и установлены указатели на процедуры обработки), отработка маскируемых аппаратных прерываний происходит следующим образом:

- устройство по событию прерывания возбуждает назначенную ему линию запроса прерывания;

- контроллер принимает сигналы запросов от источников прерываний (сигналы IRQx) и при наличии незамаскированного запроса подает сигнал общего запроса прерывания (сигнал INTR) процессору x86;

- процессор, реагируя на запрос (когда прерывания флагом IF разрешены), сохраняет в стеке содержимое регистра флагов и адрес возврата, после чего формирует шинный цикл INTA (Interrupt Acknowledge, подтверждение прерывания), который доводится до контроллера прерываний;

- в момент получения сигнала INTA контроллер прерываний фиксирует состояние своих входов запросов — к этому моменту их состояние могло измениться: могли появиться новые запросы или пропасть запрос от «нетерпеливого» устройства. Контроллер анализирует поступившие запросы в соответствии с запрограммированной схемой приоритетов и посылает процессору вектор прерывания, соответствующий самому приоритетному незамаскированному запросу, присутствующему на входе контроллера в момент подачи шинной команды INTA. При этом контроллер выполняет и некоторые действия в соответствии с установленной приоритетной политикой, учитывающие, какой именно вектор был послан (какой из запросов пошел на обслуживание);

- получив вектор прерывания, процессор по его номеру вызывает соответствующую процедуру обработки прерывания. Если данный вектор прерывания используется не только для аппаратных прерываний, но и для исключений и/или программных прерываний, то процедура в первую очередь должна определить, к какому из этих типов относится данное событие. Для этого процедура может обратиться к контроллеру PIC (прочитать регистр ISR) и проанализировать состояние регистров процессора. Дальнейшие шаги рассматриваются для случая, когда обнаружено аппаратное прерывание;

- процедура обработки прерывания должна идентифицировать источник прерывания — определить устройство, его вызвавшее. В случае разделяемого использования несколькими устройствами данного номера запроса (следовательно, и вектора) идентифицировать источник прерывания можно только последовательными обращениями к регистрам каждого из этих устройств. При этом следует учитывать возможность поступления запросов от нескольких устройств одновременно или в процессе обработки прерывания от одного из них;

- процедура должна обслужить устройство-источник прерывания — выполнить «полезные» действия, связанные с событием, о котором и сигнализировало устройство. Это обслуживание должно обеспечить и снятие сигнала запроса прерывания от данного устройства. В случае разделяемых прерываний источников может быть и несколько, и все они требуют обслуживания;

- если обработка прерывания занимает значительное время, в течение которого требуется реакция системы на более приоритетные запросы, то после критической секции в обработчик включают инструкцию STI, устанавливающую флаг разрешения прерываний (IF) в процессоре. С этого момента возможны вложенные прерывания, прерывающие работу данного обработчика другой, более приоритетной процедурой;

- процедура обработки прерывания должна послать контроллеру команду завершения обработки прерывания EOI (End Of Interrupt), по которой контроллер разрешит последующий прием сигнала с обслуженного входа и менее приоритетных. Это должно быть сделано после снятия сигнала прерывания от обслуженных устройств, иначе контроллер после EOI пошлет повторный запрос. Обработчик прерывания, для которого запрос поступил от ведомого контроллера, должен послать EOI как ведомому, так и ведущему контроллеру. Участок обработчика, начинающийся от подачи команды EOI до завершения (инструкции IRET), должен быть непрерываемым, то есть он является критической секцией. Если обработчик разрешал вложенные прерывания, то перед подачей команды EOI должна присутствовать инструкция CLI, запрещающая прерывания;

- завершается обработка прерывания инструкцией IRET, по которой процессор возвращается к выполнению прерванного потока инструкций, предварительно извлекая из стека содержимое регистра флагов. При этом аппаратные прерывания снова окажутся разрешенными.

Эта последовательность описана применительно к обычному контроллеру прерываний (PIC), в системах с APIC меняется способ доставки вектора прерывания от контроллера к процессору, а в прерываниях MSI меняется способ доставки сигнала от устройства к контроллеру APIC. Эти нюансы описаны в последующих разделах.

Мы подошли к моменту, когда без изучения прерываний дальнейшее изучение микроконтроллеров будет делом сложным. Но и сами прерывания являются одной из самых сложных для изучения тем.

Поэтому соберитесь и запаситесь терпением. Прерываниям будет посвящено несколько статей, в которых мы рассмотрим и аппаратные, и программные вопросы. И, разумеется, особенности реализации прерываний в различных семействах микроконтроллеров.

Кроме того, будет полезно вспомнить статью " Микроконтроллеры для начинающих. Часть 2. Процессор микроконтроллера ". В ней показано, в частности, как формируется адрес команды, которую будет исполнять процессор. А так же статью " Микроконтроллеры для начинающих. Часть 3. Процессор микроконтроллера. Тактирование и синхронизация. ". Здесь показано, как организована совместная работа узлов процессора.

Что такое прерывания

Прежде всего, нам надо разобраться, что же такое прерывания. Собственно говоря ответ на этот вопрос кроется в самом термине. Прерывание действительно прерывает нормальное выполнение программы. А управление получает процедура обработки (обслуживания) прерывания, которую кратко называют ISR - Interrupt service routine.

После завершения обработки прерывания выполнение программы продолжается как обычно, с того самого места, в котором прерывание возникло.

Очень похоже на вызов подпрограмм? Да, похоже. Но есть одно важнейшее отличие - программа не должна знать, что прерывание вообще возникало. Программа не должна зависеть от того, возникло прерывание, или нет. За исключением случаев, когда программист такую зависимость предусматривает в явном виде.

А это означает, что переход к обработке прерывания требует дополнительных действий, которые могут выполняться или аппаратно, или программно.

Программные прерывания, синхронные

В микроконтроллерах, тех, что мы рассматриваем, программные прерывания есть только в STM8. Это команда TRAP. Но в микроконтроллерах вообще, тем более, в микропроцессорах, может быть несколько различных программных прерываний.

Программные прерывания всегда синхронные. То есть, они возникают синхронно с ходом выполнения программы, всегда в одном и том же месте - при выполнении команды прерывания.

Программные прерывания можно рассматривать как простой вызов подпрограммы, но адрес этой подпрограммы всегда предопределен и изменить его нельзя. И нельзя передать такой подпрограмме параметры, иначе чем заранее предусмотренные программистом переменные, обычно, глобальные.

Поскольку программные прерывания вызываем мы сами, не требуется сохранение состояния (контекста) процессора. Но поведение конкретного процессора при обработке программных прерываний нужно искать в документации.

Мы не будем рассматривать программные прерывания в рамках данного цикла статей.

Аппаратные прерывания, асинхронные

Сегодня аппаратные прерывания есть в подавляющем большинстве микроконтроллеров. Но исключения все таки есть, например, линейка BaseLine микроконтроллеров PIC.

Аппаратные прерывания всегда асинхронные. То есть, момент их возникновения никак не связан с выполнением программы. Может возникнуть вопрос, как так не связан, а, например, АЦП? Мы же сами запрашиваем преобразование, а значит, возникающее при завершении преобразования прерывание вызвано именно нами, синхронно.

Нет, совсем не синхронно и не нами. Да, мы сами запросили преобразование. Но сколько для преобразования потребуется времени мы не знаем, количество тактов преобразования может зависеть от многих параметров. Поэтому и прерывание все равно возникнет асинхронно.

Аппаратные прерывания могут быть вызваны и внутренними модулями микроконтроллера, и внешними цепями (через специальный вход INT). Кроме того, аппаратные прерывания могут возникать и при выполнении программы, команды. Например, деление на 0. И это тоже асинхронное прерывание.

Приоритеты прерываний

Некоторые аппаратные прерывания могут быть более важными, чем другие. Например, готовность байта полученного из канала связи более важна, чем нажатие кнопки. При этом говорят о приоритете прерываний.

Уровней приоритета может быть несколько. Но возможно и полное отсутствие деления на приоритеты. Если одновременно возникает несколько запросов прерывания, то обрабатываться они будут в порядке убывания приоритета. Реализуется приоретизация аппаратно.

Прерывание может возникнуть во время обработки другого прерывания. В этом случае говорят о вложенности прерываний.

Вложенные прерывания

Процедура обработки прерывания тоже может быть прервана новым прерыванием, но только если его приоритет выше, чем у обрабатываемого. То есть, мы получаем обработку прерывания внутри обработки другого прерывания. Это и есть вложенность.

В большинстве случаев с вложенными прерываниями проблем не возникает. После завершения обработчика более высокого приоритета управление вернется в прерванный обработчик.

Контроллер прерываний

Теперь становится понятным, что обработка прерываний не такой простой процесс. Запуск процедуры обработки прерывания, безусловно, будет процессор. Но вот разбираться с приоритетами, запретами (маскированием) прерываний, другой вспомогательной (но важной!) работой будет специальный модуль - контроллер прерываний. Этот контроллер может быть и очень простым, и очень сложным. И может быть выполнен как в виде модуля внутри микроконтроллера, так и быть внешней микросхемой.

И сегодня основное внимание я буду уделять именно контроллеру прерываний.

Контроллер прерываний

И начнем мы с самого простого случая. Сегодня он скорее гипотетический, но зато позволит начать разбираться с тем, что лежит в самой глубине процессов

Единственный источник прерываний

Сейчас мы будем рассматривать собственно процессор. Причем процессор имеющий единственный вход запроса прерывания.

Простейший контроллер прерываний с единственным источником, фиксированным адресом обработчика, без приоритетов. Иллюстрация моя Простейший контроллер прерываний с единственным источником, фиксированным адресом обработчика, без приоритетов. Иллюстрация мояЯ не стал показывать всю функциональную схему процессора. Она есть в статьях, ссылки на которые я дал ранее. Здесь же я показал только регистр адреса команды PC и дополнительные узлы, которые используются для обработки прерывания.

Но сначала о регистре PC. Как Вы уже знаете, этот регистр автоматически инкрементируется для перехода к следующей команде. Так же, в него можно загрузить адрес из команд перехода и вызова. Разумеется, этот регистр можно и прочитать.

Я показал, что запись и чтение регистра выполняется через ALU, подписав соответствующие цепи. Все остальные сигналы просто идут к/от других узлов процессора, которые нам сегодня не важны.

Триггер IE_TRIG отвечает за разрешение/запрет прохождения запроса прерывания в процессор. Он может быть частью регистра состояния процессора или частью иного регистра. В данном случае, если он установлен, прерывания разрешены, а если сброшен запрещены.

Триггер INT_TRIG отвечает за хранение запроса прерывания, так как я показал, что вход INT, собственно вывод на который поступает запрос из внешнего мира, является не потенциальным, а импульсным.

Как все это работает. Когда на вход INT поступает импульс запроса прерывания в INT_TRIG записывается 1 (триггер устанавливается). И это выполняется независимо от того, разрешены прерывания или нет. Если прерывания запрещены, то обработка просто будет отложена до момента разрешения. Триггер будет хранить запрос.

На вход процессора сигнал запроса прерывания IF попадет лишь в том случае, если триггер IE_TRIG будет установлен. То есть, если прерывания будут разрешены.

Теперь в игру вступает процессор. И первым делом он запрещает прерывания сбросив IE_TRIG. Теперь нам не важно состояние INT_TRIG поэтому сбрасывается и он. Заодно это позволяет зафиксировать запрос прерывания, который может придти во время обработки текущего прерывания. Далее, обязательно, сохраняет регистр PC.

Выполнив всю дополнительную работу, например, сохранив состояние процессора, процессор записывает в PC адрес процедуры обработки прерывания. Когда процедура обработки завершится она выполнит не команду RET (возврат), а специальную команду IRET (возврат из прерывания).

Теперь процессор снова выполняет всю дополнительную работу, например, восстанавливает состояние процессора. После чего можно восстановить регистр PC. Остается разрешить прерывания.

Теперь программа продолжит работать с того места, где ее выполнение было прервано.

В документации и книгах часто пишут, что восстанавливается состояние разрешения обработки прерываний. Это верно, но не совсем точно. Дело в том, что если уж мы попали в обработчик прерывания, значит прерывания точно были разрешены. И мы можем просто установить IE_TRIG без дополнительных раздумий.

А теперь начнем усложнять нашу задачу. Для начала увеличим количество источников прерывания, но оставим единственный обработчик.

Несколько источников прерываний, единственный обработчик

Ярким представителем такого подхода являются микроконтроллеры PIC, за исключением BaseLine и PIC18.

Контроллер прерываний для нескольких источников, но с единственным обработчиком.Без приоритетов. Цепи сброса триггеров INT_REG не показаны. Иллюстрация моя Контроллер прерываний для нескольких источников, но с единственным обработчиком.Без приоритетов. Цепи сброса триггеров INT_REG не показаны. Иллюстрация мояОсновное отличие здесь в замене INT_TRIG на INT_REG и появлении дополнительного регистра IE_REG. Кроме того, теперь у нас не IE_TRIG, а GIE_TRIG. Дело в том, что теперь он управляет глобальным разрешением/запретом прерываний. А вот запретить/разрешить конкретный источник мы можем через IE_REG.

В целом, обработка прерываний не изменилась. Автоматически сбрасывается GIE_TRIG, что запрещает все прерывания, глобально. IE_REG автоматически не изменяется, только программно, если это программист это предусмотрел.

А вот со сбросом INT_REG все сложнее и интереснее. Сбросить регистр целиком нельзя, можно только триггер соответствующий обрабатываемому запросу. Но как этот триггер найти? Ответ простой - никак.

Поэтому в подобных контроллерах запросы прерываний от источников не сбрасываются автоматически. Их обязательно нужно сбрасывать вручную.

А как мы можем найти источник запроса, вызвавшего прерывание? У нас ведь обработчик один на всех. Довольно просто - прочитав содержимое INT_REG и проанализировав его биты. Это позволит определить источник и вызвать соответствующую подпроцедуру обработки. Именно она потом и сбросит флаг запроса.

Кстати последовательность анализа битов INT_REG определяет и приоритетность прерывания. Такой вот дополнительный программный бонус. Считаете невозможным, так как прерывания запрещаются автоматически?

Возможно! Достаточно держать прерывания запрещенными глобально. При этом триггеры INT_REG будут фиксировать поступающие запросы. Теперь, разрешив в нужный момент прерывания (глобально) мы можем обработать их все сразу. В нужном нам порядке.

Безусловно, это далеко не универсальный метод. Но это и чистая теория, как может показаться. Дело в том, что несколько запросов (они же асинхронные!) могут придти одновременно. Кроме того, мы можем запрещать прерывания на время выполнения критических участков программы по необходимости. А после их разрешения получить как раз такую вот ситуацию.

Несколько источников, несколько обработчиков

Продолжаем усложнять нашу задачу. Давайте добавим отдельные обработчики для каждого источника прерывания. Это не так просто, как может показаться.

Но сначала нам надо вспомнить, что такое вектор прерывания. В своем первоначальном варианте вектором называлась ячейка памяти хранившая адрес обработчика. Содержимое этой ячейки загружалось в PC, что и приводило к переходу на обработчик. И мы могли спокойно изменять адрес обработчика, просто занеся его в вектор.

Однако, в микроконтроллерах (по крайней мере тех, что мы изучаем) вектор это просто определенный набор ячеек памяти команд на начало которого и передается управление. А программист размещает в векторе команду перехода на нужный обработчик.

Преобразовать номер прерывания (номер источника) в адрес перехода (вектора) достаточно легко. Например, можно сдвинуть номер вектора влево на два разряда и сбросить два младших разряда. И мы получим вектор позволяющий разместить 4 команды.

Фрагмент контроллера прерываний обеспечивающего для каждого источника свой обработчик. Иллюстрация моя Фрагмент контроллера прерываний обеспечивающего для каждого источника свой обработчик. Иллюстрация мояЯ не стал показывать всю функциональную схему контроллера прерываний, для наглядности. Что у нас здесь добавилось? Во первых, шифратор, причем шифратор приоритетный, что бы корректно обрабатывать ситуацию с несколькими конкурирующими запросами прерываний. Во вторых, мультиплексор, который определяет источник адреса для занесения в регистр PC.

Источниками адресам могут быть адрес команды из ALU, для команд перехода, или адрес вектора из нашего контроллера прерываний.

Запрос прерывания из источника с помощью приоритетного шифратора превращается в номер прерывания. У нас 4 источника, поэтому достаточно 2 бит адреса. Но вектор должен вмещать более одной команды. Поэтому номер вектора мы помещаем в биты 3 и 2 адреса, а биты 1 и 0 сбрасываем, что и показано на иллюстрации.

Это позволяет нам разместить в каждом векторе до 4 команд, а адрес вектора (адрес первой команды) будет равен номеру прерывания умноженному на 4.

В остальном обработка прерываний не изменилась. Но теперь у нас появилась возможность автоматически сбрасывать соответствующий триггер в INT_REG, ведь мы теперь знаем его номер. Я не буду показывать, как это выполняется на функциональной схеме.

Контроллер прерываний с приоритетами

Приоритетный шифратор в предыдущем случае не означает, что у прерываний есть приоритет. Да, он позволяет выбрать из нескольких прерываний одно, с наименьшим номером (наибольшим приоритетом). Но это не делает возможным прервать текущий обработчик прерывания с меньшим приоритетом.

Причина проста, при возникновении прерывания у нас прерывания запрещаются глобально. Я не буду приводить иллюстрацию, она сложна для начинающих, я просто расскажу, как это работает.

Вводится дополнительный регистр, который хранит приоритет текущего обрабатываемого прерывания. Причем, в общем случае, приоритет не равен номеру прерывания. Например, прерывания могут быть сгруппированы по несколько штук в пределах одного приоритета.

Прерывания не запрещаются глобально. Прерывания запрещаются для приоритета текущего прерывания и меньших приоритетов. При поступлении нового запроса специальный компаратор сравнивает его приоритет с текущим (хранится в специальном регистре, как я говорил). Если приоритет нового запроса выше, он поступает в процессор, что приводит к прерыванию текущего обработчика.

Причем это простейший случай. Могут быть предусмотрены дополнительные режимы работы. Например, циклическая смена приоритетов. Причем и приоритетов в группе, и групп приоритетов.

Когда мы будет изучать реализацию контроллеров прерываний в конкретных семействам микроконтроллеров, мы вернемся к приоретизации.

Заключение

Информация о ПК Общая информация о ПК ПрерываниеЗачастую во время работы ПК возникает ситуация, когда процессору не обходимо приостановить выполнение основной программы и обработать событие, возникшее в одном из устройств компьютера. Для решения этой проблемы используется механизм прерываний.

Прерывание (interrupt, INT) – это приостановка центральным процессором выполнения приоритетной программы для обработки события, которое поступило от одного из устройств.

Механизм прерываний реализован следующим образом:

- В случае возникновения события, требующего вмешательства ЦП, устройство, которое вызвало данное событие, посылает специальный сигнал – запрос на прерывание.

- Запрос на прерывание обрабатывается контроллером прерываний.

- Сигнал, после обработки контроллером прерываний, передается процессору. Процессор приостанавливает выполнение основной программы (сохраняя при этом текущее состояние своих регистров в оперативную память) и обрабатывает данное прерывание. После обработки прерывания процессор продолжает выполнять основную программу.

- В случае возникновение одного прерывания во время обработки процессором другого, выполнение прерываний будет согласно их приоритету.

Контроллер прерываний (Programmable Interrupt Controller, PIC) – это микросхема (или встроенный в процессор модуль), которая выполняет обработку запросов на прерывание от различных устройств.

Каждому прерыванию присваивают число, называемое номером прерывания. Некоторые из номеров прерывания зарезервированы за определенными устройствами, некоторые можно освободить и использовать для других устройств. Обозначается прерывание символом IRQ.

Классификация прерываний.

1. Немаскируемые прерывания (Non-Maskable Interrupt, NMI). Прерывания с высшим приоритетом. Прерывания данного типа обрабатываются в случаях возникновения аварийных ситуаций, вызванных ошибками в работе памяти или других устройств.

2. Маскируемые (аппаратные) прерывания. В эту группу относят прерывания от периферийных устройств. Обрабатываются контроллером прерываний. Стандартный контроллер прерываний позволяет обращаться к 16 прерываниям от различных устройств. Сегодня имеется возможность использовать расширенный контроллер прерываний APIC.

APIC (Advanced Programmable Interrupt Controller) – расширенный программируемый контроллер прерываний, позволяющий использовать 24 аппаратных прерываний вместо 16.

Примером аппаратного прерывания может быть сигнал от таймера, звуковой карты, нажатие клавиши клавиатуры.

Читайте также: