Как организовано электропитание центрального процессорного устройства цпу л

Обновлено: 01.07.2024

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

25–27 ноября, Онлайн, Беcплатно

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные: move , input , outptut , load и store .

- Команды перехода: goto , if . goto , call и return .

- Команда останова: halt .

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

- LOAD_A 8 . Это команда сохраняет в ОЗУ данные, скажем, <1100 1000> . Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкцию load_A — поместить данные 1000 (последние 4 бита команды) в регистр A .

- LOAD_B 2 . Ситуация, аналогичная прошлой. Здесь помещается число 2 ( 0010 ) в регистр B .

- ADD B A . Команда суммирует два числа (точнее прибавляет значение регистра B в регистр A ). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистр A .

- STORE_A 23 . Сохраняем значение регистра A в ячейку памяти с адресом 23 .

Вот такие операции нужны, чтобы сложить два числа.

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Как центральный процессор может сокращать собственное энергопотребление? Основы этого процесса — в статье.

Центральный процессор (CPU) спроектирован на бесконечно долгую работу при определенной нагрузке. Практически никто не проводит вычисления круглые сутки, поэтому большую часть времени он не работает на расчетном максимуме. Тогда какой смысл держать его включенным на полную мощность? Здесь стоит задуматься об управлении питанием процессора. Эта тема включает в себя оперативную память, графические ускорители и так далее, но я собираюсь рассказать только про CPU.

Если вы знаете про C-состояния (C-states), P-состояния (P-states) и то, как процессор переходит между ними, то, возможно, в этой статье вы не увидите ничего нового. Если это не так, продолжайте читать.

Я планировал добавить реальные примеры из ОС Linux, но статья становилась все больше, так что я решил приберечь это для следующей статьи.

Основные источники информации, использованные в этом тексте:

Особенности CPU

Согласно официальной странице продукта, мой процессор поддерживает следующие технологии:

- состояния простоя (Idle States);

- усовершенствованная технология Intel® SpeedStep (Enhanced Intel® SpeedStep Technology).

Теперь выясним, что значит каждое из этих определений.

Как снизить энергопотребление процессора во время его работы?

На процессорах для массового использования (мы не берем в расчет вещи, которые возможны при их проектировании) для снижения потребляемой энергии можно реализовать один из сценариев:

- Сократить энергопотребление подсистемы (ядра или другого ресурса, такого как тактовый генератор или кэш) путем отключения питания (уменьшив напряжение до нуля).

- Снизить энергопотребление путем снижения напряжения и/или таковой частоты подсистемы и/или целого процессора.

Второй вариант требует чуть больше объяснений. Энергопотребление интегральной схемы, которой является процессор, линейно пропорционально тактовой частоте и квадратично напряжению.

Примечание для тех, кто разбирается в цифровой электронике: Pcpu = Pdynamic + Pshort circuit + Pleak. При работающем процессоре Pdynamic является наиболее важной составляющей, именно эта часть зависит линейно от частоты и квадратично от напряжения. Pshort circuit пропорционально частоте, а Pleak — напряжению.

Более того, напряжение и тактовая частота связаны линейной зависимостью.

Высокая производительность требует повышенной тактовой частоты и увеличения напряжения, что еще больше влияет на энергопотребление.

Каков предел энергопотребления процессора?

Это во многом зависит от процессора, но для процессора E3-1245 v5 @ 3.50 ГГц расчетная тепловая мощность (Thermal Design Power, TDP) составляет 80 ватт. Это среднее значение, которое процессор может выдерживать бесконечно долго (Power Limit, PL1 на изображении ниже). Системы охлаждения должны быть рассчитаны на это значение, чтобы быть надежными. Фактическое энергопотребление процессора может быть выше в течение короткого промежутка времени (состояния PL2, PL3, PL4 на изображении ниже). TDP измеряется при нагрузке высокой вычислительной сложности (худший случай), когда все ядра работают на базовой частоте (3.5 ГГц).

Как видно на изображении выше, процессор в состоянии PL2 потребляет больше энергии, чем заявлено в TDP. Процессор может находиться в этом состоянии до 100 секунд, а это достаточно долго.

Состояния питания (C-states) vs состояния производительности (P-states)

Состояния питания (C-states) vs состояния производительности (P-states)

Вот два способа снизить энергопотребление процессора:

- отключить некоторые подсистемы;

- снизить напряжение/частоту.

P-состояния описывают второй случай. Подсистемы процессора работают, но не требуют максимальной производительности, поэтому напряжение и/или тактовая частота для этой подсистемы может быть снижена. Таким образом, P-состояния, P[X], обозначают, что некоторая подсистема (например, ядро), работает на заданной паре (частота, напряжение).

Так как большинство современных процессоров состоит из нескольких ядер, то С-состояния разделены на С-состояния ядра (Core C-states, CC-states) и на С-состояния процессора (Package C-states, PC-states). Причина появления PC-состояний очень проста. Существуют компоненты с общим доступом (например, общий кэш), которые могут быть отключены только после отключения всех ядер, имеющих доступ к этому компоненту. Однако мы в роли пользователя или программиста не можем взаимодействовать с состояниями пакета напрямую, но можем управлять состояниями отдельных ядер. Таким образом, управляя CC-состояниями, мы косвенно управляем и PC-состояниями.

Состояния нумеруются от нуля по возрастанию, то есть C0, C1… и P0, P1… Большее число обозначает большее энергосбережение. C0 означает, что все компоненты включены. P0 означает максимальную производительность, то есть максимальные тактовую частоту, напряжение и энергопотребление.

С-состояния

Вот базовые С-состояния (определенные в стандарте ACPI).

- C0: Active, процессор/ядро выполняет инструкции. Здесь применяются P-состояния, процессор/ядро могут работать в режиме максимальной производительности (P0) или в режиме энергосбережения (в состоянии, отличном от P0).

- C1: Halt, процессор не выполняет инструкций, но может мгновенно вернуться в состояние С0. Поскольку процессор не работает, то P-состояния не актуальны для состояний, отличных от С0.

- C2: Stop-Clock, схож с C1, но требует больше времени для возврата в C0.

- С3: Sleep. Возврат в C0 требует ощутимо большего времени.

Примечание: Из-за технологии Intel® Hyper-Threading существуют также С-состояния потоков. Хотя отдельный поток может работать с С-состояниями, изменения в энергопотреблении происходят, только когда ядро входит в нужное состояние. В данной статье тема C-состояний на потоках рассматриваться не будет.

Вот описание состояний из даташита:

Примечание: LLC обозначает Last Level Cache, кэш последнего уровня и обозначает общий L3 кэш процессора.

Визуальное представление состояний:

Источник: Software Impact to Platform Energy-Efficiency White Paper

Последовательность C-состояний простыми словами:

- Нормальная работа при C0.

- Сначала останавливается тактовый генератор простаивающего ядра (С1).

- Затем локальные кэши ядра (L1/L2) сбрасываются и снимается напряжение с ядра (С3).

- Как только все ядра отключены, общий кэш (L3/LLC) ядер сбрасывается и процессор (почти) полностью может быть обесточен. Я говорю «почти», потому что, по моим предположениям, какая-то часть должна быть активна, чтобы вернуть процессор в состояние С0.

Однако если ядро работает (C0), то единственное состояние, в котором может находиться процессор, — C0. С другой стороны, если ядро полностью выключено (C8), процессор может находиться в C0, если другое ядро работает.

Примечание: Intel Software Developer’s Manual упоминает про суб-C-состояния (sub C-state). Каждое С-состояние состоит из нескольких суб-С-состояний. После изучения исходного кода модуля ядра intel_idle я понял, что состояния C1 и C1E являются состоянием С1 с подтипом 0 и 1 соответственно.

Число подтипов для каждого из восьми С-состояний (0..7) определяется с помощью инструкции CPUID. Для моего процессора утилита cpuid выводит следующую информацию:

Я создал гистограмму, представленную ниже, из исходного кода драйвера intel_idle для моего процессора (модель 0x5e). Подписи горизонтальной оси:

Имя C-состояния: специфичное для процессора состояние: специфичное суб-состояние.

Вертикальная ось обозначает задержку выхода и целевые резидентные значения из исходного кода. Задержка выхода используется для оценки влияния данного состояния в реальном времени (то есть сколько времени потребуется для возвращения в С0 из этого состояния). Целевое резидентное значение обозначает минимальное время, которое ядро должно находиться в данном состоянии, чтобы оправдать энергетические затраты на переход в это состояние и обратно. Обратите внимание на логарифмический масштаб вертикальной оси. Задержки и минимальное время нахождения в состоянии увеличивается экспоненциально с увеличением номера состояния.

Константы задержок выхода и целевых резидентных значении C-состояний в исходном коде intel_idle

Примечание: Хотя состояния С9 и С10 включены в таблицу, они имеют 0 суб-состояний и поэтому не используются в моем процессоре. Остальные процессоры из семейства могут поддерживать эти состояния.

Состояния питания ACPI

Прежде чем говорить про P-состояния, стоит упомянуть про состояния питания ACPI. Это то, что мы, пользователи, знаем, когда используем компьютер. Так называемые глобальные системные состояния (G[Х]) перечислены в таблице ниже.

Источник: ACPI Specification v6.2

Также существует специальное глобальное состояние G1/S4, Non-Volatile Sleep, когда состояние системы сохраняется на энергонезависимое хранилище (например, диск) и затем производится выключение. Это позволяет достичь минимального энергопотребления, как в состоянии Soft Off, но возвращение в состояние G0 возможно без перезагрузки. Оно более известно как гибернация.

Существует несколько состояний сна (Sx). Всего таких состояний шесть, включая S0 — отсутствие сна. Состояния S1-S4 используются в G1, а S5, Soft Off, используется в G2. Краткий обзор:

- G0/S0: Компьютер работает, не спит.

- G1: Sleeping.

- G1/S1: Power on Suspend. Состояние системы сохраняется, питание процессора и кэшей поддерживается.

- G1/S2: Процессор отключен, кэши сброшены.

- G1/S3: Standby или Suspend to RAM (STR). Оперативная память остается практически единственным компонентом с питанием.

- G1/S4: Hibernation или Suspend to Disk. Все сохраняется в энергонезависимую память, все системы обесточиваются.

![]()

Вот поддерживаемые состояния ACPI.

![]()

Комбинации состояний ACPI G/S и С-состояний процессора

Приятно видеть все комбинации в таблице:

![]()

В состоянии G0/S0/C8 системы процессора запущены, но все ядра отключены.

В G1 (S3 или S4) некорректно говорить про С-состояния (это касается как CC-состояний, так и PC-состояний), так как процессор полностью обесточен.

Для G3 не существует S-состояний. Система не спит, она физически отключена и не может проснуться. Ей необходимо сначала получить питание.

Как программно запросить переход в энергосберегающее С-состояние?

Современный (но не единственный) способ запросить переход в энергосберегающее состояние — это использовать инструкцию MWAIT или инструкцию HLT. Это инструкции привилегированного уровня, и они не могут быть выполнены пользовательскими программами.

Инструкция MWAIT (Monitor Wait) заставляет процессор перейти в оптимизированное состояние (C-состояние) до тех пор, пока по указанному (с помощью другой инструкции, MONITOR) адресу не будет произведена запись. Для управления питанием MWAIT работает с регистром EAX. Биты 4-7 используются для указания целевого С-состояния, а биты 0-3 указывают суб-состояние.

Примечание: Я думаю, что на данный момент только AMD обладает инструкциями MONITORX/MWAITX, которые, помимо мониторинга записи по адресу, работают с таймером. Это еще называется Timed MWAIT.

Инструкция HLT (halt) останавливает выполнение, и ядро переходит в состояние HALT до тех пор, пока не произойдет прерывание. Это означает, что ядро переходит в состояние C1 или C1E.

Что вынуждает ядро входить в определенное С-состояние?

Как отмечалось ранее, переходы между глубокими С-состояниями имеют высокие задержки и высокие энергетические затраты. Таким образом, такие переходы должны выполняться с осторожностью, особенно на устройствах, работающих от аккумуляторов.

Возможно ли отключить С-состояния (всегда использовать С0)?

Это возможно, но не рекомендуется. В даташите (секция 4.2.2, страница 64) есть примечание: «Долгосрочная надежность не гарантируется, если все энергосберегающие состояния простоя не включены». Поэтому вам не стоит отключать С-состояния.

Как прерывания влияют на процессор\ядро в состоянии сна?

Когда происходит прерывание, соответствующее ядро пробуждается и переходит в состояние С0. Однако, например Intel® Xeon® E3-1200 v5, поддерживает технологию Power Aware Interrupt Routing (PAIR), у которой есть два достоинства:

- для энергосбережения прерывание может быть переадресовано работающему ядру, чтобы не будить спящее ядро;

- для производительности прерывание может быть переадресовано от работающего на полную мощность ядра к простаивающему (С1) ядру.

P-состояния

P-состояния подразумевают, что ядро в состоянии С0, потому что ему требуется питание, чтобы выполнять инструкции. P-состояния позволяют изменять напряжение и частоту ядра (другими словами рабочий режим), чтобы снизить энергопотребление. Существует набор P-состояний, каждое из которых соответствует разных рабочим режимам (пары напряжение-частота). Наиболее высокий рабочий режим (P0) предоставляет максимальную производительность.

Процессор Intel® Xeon® E3–1200 v5 позволяет контролировать P-состояния из операционной системы (Intel® SpeedStep Technology) или оставить это оборудованию (Intel® Speed Shift Technology). Вся информация ниже специфична для семейства Intel® Xeon® E3-1200 v5, но я полагаю, это в той или иной степени актуально и для других современных процессоров.

P-состояния, управляемые операционной системой

В этом случае операционная система знает о P-состояниях и конкретном состоянии, запрошенным ОС. Проще говоря, операционная система выбирает рабочую частоту, а напряжение подбирается процессором в зависимости от частоты и других факторов. После того, как P-состояние запрошено записью в моделезависимый регистр (подразумевается запись 16 бит в регистр IA32_PERF_CTL), напряжение изменяется до автоматически вычисленного значения и тактовый генератор переключается на заданную частоту. Все ядра имеют одно общее P-состояние, поэтому невозможно установить P-состояние эксклюзивно для одного ядра. Текущее P-состояние (рабочий режим) можно узнать, прочитав информацию из другого моделезависимого регистра — IA32_PERF_STATUS.

Смена P-состояния мгновенна, поэтому в секунду можно выполнять множество переходов. Это отличает от переходов C, которые выполняются дольше и требуют энергетических затрат.

P-состояния, управляемые оборудованием

В этом случае ОС знает об аппаратной поддержке P-состояний и отправляет запросы с указанием нагрузки. В запросах не указывается конкретное P-состояние или частота. На основе информации от ОС, а также других факторов и ограничений оборудование выбирает подходящее P-состояние.

Я хочу рассказать об этом подробнее в следующей статье, но сейчас я поделюсь с вами своими мыслями. Мой домашний компьютер работает в этом режиме, я узнал это, проверив IA32_PM_ENABLE. Максимальный (но не гарантированный) уровень производительности — 39, минимальный — 1. Можно предположить, что существует 39 P-состояний. На данный момент уровень 39 установлен ОС как минимальный и как максимальный, потому что я отключил динамическое изменение частоты процессора в ядре.

Заметки про Intel® Turbo Boost

Поскольку TDP (расчетная тепловая мощность) — это максимальная мощность, которую процессор может выдержать, то процессор может повышать свою частоту выше базовой, при условии что энергопотребление не превысит TDP. Технология Turbo Boost может временно повышать энергопотребление до границы PL2 (Power Limit 2) на короткий промежуток времени. Поведение Turbo Boost может быть изменено через подсказки оборудованию.

Применима ли эта информация о C-состояниях и P-состояниях к мобильным и встраиваемым процессорам?

Для примера, недавний MacBook Air с процессором i5-5350U в основном поддерживает возможности, описанные выше (но я не уверен про P-состояния, контролируемые оборудованием). Я также смотрел документацию ARM Cortex-A, и, хотя там применяются другие термины, механизмы управления питанием выглядят похоже.

Как это все работает, например, на Linux?

На этот вопрос я отвечу в другой статье.

Как я могу узнать состояние процессора?

Существует не так много приложений, которые могут выводить эту информацию. Но вы можете использовать, например, CoreFreq.

Неотъемлемой частью любой системы ЭЦ являются источники электропитания, назначение которых бесперебойно обеспечивать системы электрической энергией требуемого вида и качества. Поэтому источники электропитания в новых системах ЭЦ существенно изменились: уменьшились их габариты, повысился КПД за счет применения наиболее рациональных интегральных микросхем, использования высокочастотного преобразования энергии постоянного тока и экономичных импульсных методов регулирования.

Система питания МПЦ Ebilock-950 соответствует общим для российских железных дорог принципам построения систем питания ЭЦ. Основными составляющими системы электропитания являются: вводный щит, на который подается питание от двух фидеров; специальная панель контроля и переключения фидеров; источник бесперебойного питания с изолирующим трансформатором; распределительный щит, с которого разводится питание по объектам централизации — в контейнеры объектных контроллеров, на устройства центрального процессора, для питания аппаратуры автоматизированных рабочих мест ДСП и электромеханика СЦБ, на стативы с релейным оборудованием. Обобщенная структурная схемы системы электропитания МПЦ и отдельного модуля показаны на рис. 2.50. Вместе с тем в организации питания устройств ЭЦ на базе процессорной техники имеются некоторые отличия.

Параметры электрических сетей не всегда соответствуют норме, поэтому актуален вопрос о гарантированном питании в случае возникновения неполадок электросети. Основными неполадками сетевого питания являются: авария сетевого напряжения (полное пропадание напряжения); долговременные и кратковременные подсадки и всплески напряжения; высоковольтные импульсные помехи; высокочастотный шум; выбег частоты.

Применение двух независимых фидеров питания позволяет значительно снизить вероятность полного пропадания сетевого напряжения, но остается полная зависимость от качества этого напряжения. Для обеспечения должного качества электропитания широкое распространение получили источники бесперебойного питания ИБП. Они позволяют гарантировать параметры питающего напряжения в жестких пределах (напряжение ± 1 %, частота ±0,1 %), избавиться от всякого рода высокочастотных и низкочастотных помех. В случае полного пропадания питающего напряжения ИБП способен поддерживать автономную работу системы в течение нескольких часов.

Существует также дополнительный режим работы ИБП, называемый «обход» (bypass), который заключается в питании нагрузки отфильтрованным входным сетевым напряжением в обход основной схемы преобразования ИБП. Различают автоматический и ручной режимы burras. Автоматический переход в режим burras производится устройством управления ИБП в случае перегрузки на его выходе или при неполадках в его жизненно важных узлах. Таким образом нагрузка защищается не только от изъянов питающего напряжения, но и от неполадок в самом ИБП. Ручное переключение в режим burras предусмотрено для возможности проведения сервисного обслуживания ИБП или его замены в «горячем» режиме, т.е. без перерыва питания нагрузки.

Центральный процессор Ebilock-950 является системой с дублированной структурой. Он имеет два абсолютно идентичных комплекта аппаратуры, один из которых находится в «горячем» резерве и включается в работу в случае сбоя или выхода из строя другого комплекта. Каждый комплект имеет свой блок питания 220 В, который вырабатывает все необходимые напряжения. Для повышения надежности системы левый и правый комплекты запитываются от различных фаз. Такое решение позволяет избежать полной остановки системы в случае пропадания одной из фаз питающего напряжения, так как система безопасно переключится на резервный комплект. Питание АРМ ДСП и АРМ ШН осуществляется по такому же принципу.

Система Ebilock-950 является распределенной, поэтому контейнеры с объектными контроллерами могут располагаться на значительном расстоянии от центрального поста. Для повышения надежности каждый контейнер получает питание с распределительного щита центрального поста по двум силовым кабелям, проложенным в разных траншеях. Такое решение требует установки в каждом контейнере вводного щита, способного контролировать фидеры и в случае необходимости производить переключение нагрузки с одного фидера на другой с использованием АВР. Дизель-генераторный агрегат (ДГА) Gesan—DP 63 (номинальная мощность 63 кВА) и панель управления, установленные в контейнере, обеспечивают работу системы автоматического ввода резерва (АВР) электропитания трехфазной сети 380 В, 50 Гц (см. рис. 2.50). ДГА установлен в комплексный контейнер, осуществляющий климат-контроль, коммутацию с внешними фидерами, охрану и пожарную безопасность ДГА и шкафа с аппаратурой. Электрическая система ДГА состоит из панели ручного управления и панели автоматического управления. В панель ручного управления вмонтированы: контроллер, тахометр, вольтметр, амперметр, лампа, счетчик моточасов, автоматический выключатель, переключаемый вольтметр, датчики температуры, заряда батареи, давления масла и уровня топлива. Основной элемент панели — контроллер GPM-2 — служит для управления запуском ДГА, его работой и остановкой. Кроме того, он отвечает за подачу сигналов тревоги и выполнение аварийных остановок ДГА. В панель автоматического управления вмонтированы аналогичные приборы и контроллер GESO. Этот контроллер осуществляет следующие режимы: автоматический (автотест с/без нагрузки) и ручной (ручной старт, переключение на генератор, стоп). Все ДГА с панелью автоматического управления снабжены системой подогрева для ускорения пуска двигателя и повышения быстродействия в целом. Система подогрева состоит из бака, встроенного в систему охлаждения двигателя, и нагревательного элемента с регулируемым термостатом.

![]()

В каждом контейнере может находиться несколько шкафов объектных контроллеров. В каждом шкафу размещаются до четырех полок с контроллерами и источник питания PSU, который вырабатывает все напряжения, необходимые для работы контроллеров. Источники питания системы объектных контроллеров выпускаются трех типов: PSU51 — источник питания стрелочных электроприводов, формирующий рабочие напряжения для питания двигателей стрелочных приводов, элементов внешней логики и дополнительных устройств; PSU61 — источник питания светофоров, обеспечивающий питание светофорных ламп и элементов внешней логики; PSU71 — источник питания внутренней логики системы.

Поскольку источники питания непосредственно влияют на безопасность движения поездов, к ним предъявляются высокие требования по функциональным характеристикам, электрическим параметрам и показателям надежности. Источники питания (системы объектных контроллеров) СОК в соответствии с требованиями ГОСТ 29192 -— 91 относятся к категории 2 — технические средства силовой электрической цепи, к классу 2.4—преобразователи электрической энергии, к подклассу 2.2.4 — источники вторичного питания для технических средств сигнальных и информационных цепей. Источники питания PSU51 и PSU61 в установившемся режиме имеют следующие технические возможности: обеспечивают независимую коммутацию входной и выходной обмоток трансформатора в соответствии со схемами «звезда» и «треугольник» и вырабатывают необходимые уровни напряжений и токов: ток холостого хода составляет не более 0,5 А; разница тока по отдельным фазам с первичной стороны источника питания при холостом ходе — не более 30 %; при полной нагрузке ИП СОК имеет КПД не менее 90 %. Источник питания PSU71 при выходном токе 6 А обеспечивает необходимую защиту от динамических перепадов напряжения. Из-за жесткой электромагнитной обстановки в местах эксплуатации ИП СОК к ним предъявляются высокие требования по электромагнитной совместимости. Подавление сетевых помех в источнике PSU71 выполняют фильтры. Для питания шкафа объектных контроллеров могут применяться два типа источников питания: трехфазный или однофазный (с учетом питания стрелочных электроприводов).

Распределение напряжений по контроллерам происходит следующим образом. Постоянное напряжение 24 В, питающее контроллеры, подается на специализированную плату, через которую питание распределяется по разъемам на задней стенке. Все другие напряжения, необходимые различным контроллерам для управления объектами (стрелками, светофорами, релейными интерфейсами), подаются непосредственно на платы. Каждый тип напряжения имеет несколько предохранителей, по одному на каждую плату в контроллере. При срабатывании предохранителя только одна плата остается без питания.

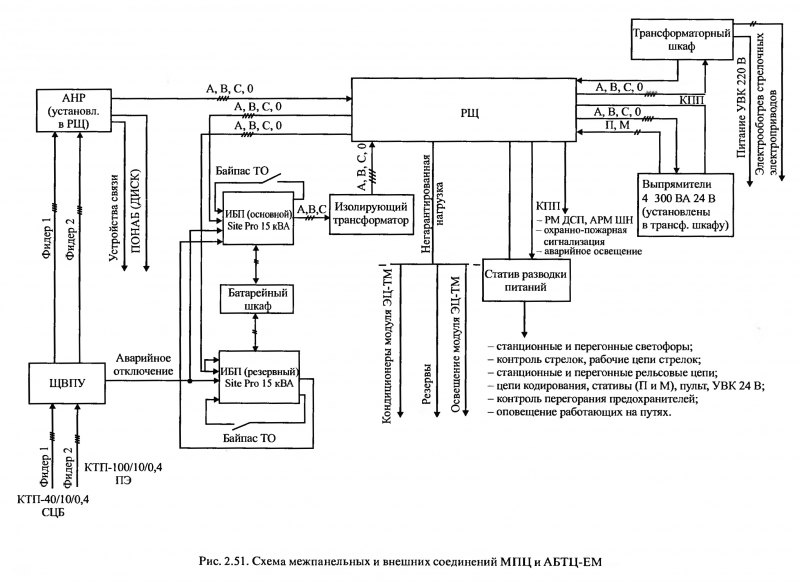

Питание устройств микропроцессорной системы ЭЦ-ЕМ осуществляется также от двух независимых источников питания с применением ИБП (схема межпанельных соединений питающей установки показана на рис. 2.51). Контроль фидеров питания выведен на резервный пульт-табло прямопроводного управления и контроля. Подключение устройств ЭЦ-ЕМ к источникам питания осуществляется через устройства электропитания, которые состоят из щита выключения питания ЩВПУ (щит выключения питания управляемый) в помещении ДСП, щита автоматического распределения нагрузки с АВР, источника бесперебойного питания ИБП и распределительного щита РЩ.

![]()

Схема электроснабжения транспортабельного модуля промежуточной станции, оборудованной системой ЭЦ-МПК, представлена на рис. 2.52. Система электропитания состоит из двух трансформаторных подстанций: КТП-25/27, подключаемой к линии ДПР напряжением 27,5 кВ, и СТП-10/27, подключаемой к линии СЦБ. К модулю прокладываются кабели марки АВБбШв-1 в земляной траншее на глубине 0,7 м от планировочной отметки земли. Пересечения кабельной линии с линиями связи и СЦБ и с железнодорожными путями выполнены в асбоцементных трубах. Заземляющие устройства этих подстанций выполнены в соответствии с нормативными документами и не превышают 5 Ом. Заземление подстанций СТП, в том числе и используемых для питания релейных шкафов входных светофоров, выполнено присоединением к нейтральной точке ближайшего дроссель-трансформатора двумя стальными проводниками диаметром 12 мм (выравнивающий контур при этом не выполняется).

![]()

Центра́льный проце́ссор (ЦП; CPU — англ. céntral prócessing únit , дословно — центральное вычислительное устройство) — исполнитель машинных инструкций, часть аппаратного обеспечения компьютера или программируемого логического контроллера, отвечающий за выполнение операций, заданных программами.

Современные ЦП, выполняемые в виде отдельных микросхем (чипов), реализующих все особенности, присущие данного рода устройствам, называют микропроцессорами. С середины 1980-х последние практически вытеснили прочие виды ЦП, вследствие чего термин стал всё чаще и чаще восприниматься как обыкновенный синоним слова «микропроцессор». Тем не менее, это не так: центральные процессорные устройства некоторых суперкомпьютеров даже сегодня представляют собой сложные комплексы больших (БИС) и сверхбольших (СБИС) интегральных схем.

Изначально термин Центральное процессорное устройство описывал специализированный класс логических машин, предназначенных для выполнения сложных компьютерных программ. Вследствие довольно точного соответствия этого назначения функциям существовавших в то время компьютерных процессоров, он естественным образом был перенесён на сами компьютеры. Начало применения термина и его аббревиатуры по отношению к компьютерным системам было положено в 1960-е годы. Устройство, архитектура и реализация процессоров с тех пор неоднократно менялись, однако их основные исполняемые функции остались теми же, что и прежде.

Ранние ЦП создавались в виде уникальных составных частей для уникальных, и даже единственных в своём роде, компьютерных систем. Позднее от дорогостоящего способа разработки процессоров, предназначенных для выполнения одной единственной или нескольких узкоспециализированных программ, производители компьютеров перешли к серийному изготовлению типовых классов многоцелевых процессорных устройств. Тенденция к стандартизации компьютерных комплектующих зародилась в эпоху бурного развития полупроводниковых элементов, мейнфреймов и миникомпьютеров, а с появлением интегральных схем она стала ещё более популярной. Создание микросхем позволило ещё больше увеличить сложность ЦП с одновременным уменьшением их физических размеров. Стандартизация и миниатюризация процессоров привели к глубокому проникновению основанных на них цифровых устройств в повседневную жизнь человека. Современные процессоры можно найти не только в таких высокотехнологичных устройствах, как компьютеры, но и в автомобилях, калькуляторах, мобильных телефонах и даже в детских игрушках. Чаще всего они представлены микроконтроллерами, где помимо вычислительного устройства на кристалле расположены дополнительные компоненты (интерфейсы, порты ввода/вывода, таймеры, и др.). Современные вычислительные возможности микроконтроллера сравнимы с процессорами персональных ЭВМ десятилетней давности, а чаще даже значительно превосходят их показатели.

Содержание

Архитектура фон Неймана

Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом.

Д. фон Нейман придумал схему постройки компьютера в 1946 году.

Важнейшие этапы этого процесса приведены ниже. В различных архитектурах и для различных команд могут потребоваться дополнительные этапы. Например, для арифметических команд могут потребоваться дополнительные обращения к памяти, во время которых производится считывание операндов и запись результатов. Отличительной особенностью архитектуры фон Неймана является то, что инструкции и данные хранятся в одной и той же памяти.

Этапы цикла выполнения:

- Процессор выставляет число, хранящееся в регистресчётчика команд, на шину адреса, и отдаёт памяти команду чтения;

- Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности;

- Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её;

- Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды;

- Снова выполняется п. 1.

Данный цикл выполняется неизменно, и именно он называется процессом (откуда и произошло название устройства).

Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм полезной работы процессора. Очерёдность считывания команд изменяется в случае, если процессор считывает команду перехода — тогда адрес следующей команды может оказаться другим. Другим примером изменения процесса может служить случай получения команды останова или переключение в режим обработки аппаратного прерывания.

Команды центрального процессора являются самым нижним уровнем управления компьютером, поэтому выполнение каждой команды неизбежно и безусловно. Не производится никакой проверки на допустимость выполняемых действий, в частности, не проверяется возможная потеря ценных данных. Чтобы компьютер выполнял только допустимые действия, команды должны быть соответствующим образом организованы в виде необходимой программы.

Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора. Частота тактовых импульсов называется тактовой частотой.

Конвейерная архитектура

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

- получение и декодирование инструкции (Fetch)

- адресация и выборка операнда из ОЗУ (Memory access)

- выполнение арифметических операций (Arithmetic Operation)

- сохранение результата операции (Store)

После освобождения k -й ступени конвейера она сразу приступает к работе над следующей командой. Если предположить, что каждая ступень конвейера тратит единицу времени на свою работу, то выполнение команды на конвейере длиной в n ступеней займёт n единиц времени, однако в самом оптимистичном случае результат выполнения каждой следующей команды будет получаться через каждую единицу времени.

![n\cdot m]()

Действительно, при отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по прежнему необходимо выполнять выборку, дешифрацию и т. д.), и для исполнения m команд понадобится единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени.

Факторы, снижающие эффективность конвейера:

- простой конвейера, когда некоторые ступени не используются (напр., адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами);

- ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд, out-of-order execution);

- очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов).

Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода.)

Суперскалярная архитектура

Способность выполнения нескольких машинных инструкций за один такт процессора. Появление этой технологии привело к существенному увеличению производительности.

x86 (хотя уже много лет эти процессоры являются CISC только по внешней системе команд).

Джоном Коком (John Cocke) изСамая распространённая реализация этой архитектуры представлена процессорами серии MIPS и Alpha.

Многоядерные процессоры

Содержат несколько процессорных ядер в одном корпусе (на одном или нескольких кристаллах).

Процессоры, предназначенные для работы одной копии операционной системы на нескольких ядрах, представляют собой высокоинтегрированную реализацию системы «Мультипроцессор».

Двухядерность процессоров включает такие понятия, как наличие логических и физических ядер: например двухядерный процессор Intel Core Duo состоит из одного физического ядра, которое в свою очередь разделено на два логических. Процессор Intel Core 2 Quad состоит из четырёх физических ядер, что существенно влияет на скорость его работы.

10 сентября 2007 года были выпущены в продажу нативные (в виде одного кристалла) четырёхьядерные процессоры для серверов AMD Quad-Core Opteron, имевшие в процессе разработки кодовое название AMD Opteron Barcelona [1] . 19 ноября 2007 вышел в продажу четырёхьядерный процессор для домашних компьютеров AMD Quad-Core Phenom [2] . Эти процессоры реализуют новую микроархитектуру K8L (K10).

27 сентября 2006 года Intel продемонстрировала прототип 80-ядерного процессора [3] . Предполагается, что массовое производство подобных процессоров станет возможно не раньше перехода на 32-нанометровый техпроцесс, а это в свою очередь ожидается к 2010 году.

На данный момент массово доступны двух- и четырехядерные процессоры, в частности Intel Core 2 Duo на 65 нм ядре Conroe (позднее на 45 нм ядре Wolfdale) и Athlon64X2 на базе микроархитектуры K8. В ноябре 2006 года вышел первый четырёхъядерный процессор Intel Core 2 Quad на ядре Kentsfield, представляющий собой сборку из двух кристаллов Conroe в одном корпусе. Потомком этого процессора стал Intel Core 2 Quad на ядре Yorkfield (45 нм), архитектурно схожем с Kentsfield но имеющем больший обьем кэша и рабочие частоты.

Компания AMD пошла по собственному пути, изготовляя четырехядерные процессоры единым кристаллом (в отличие от Intel, процессоры которой представляют собой фактически склейку двух двухядерных кристаллов). Несмотря на всю прогрессивность подобного подхода первый «четырёхядерник» фирмы, получивший название AMD Phenom X4, получился не слишком удачным. Его отставание от современных ему процессоров конкурента составляло от 5 до 30 и более процентов в зависимости от модели и конкретных задач.

На настоящий момент (1-2 квартал 2009 года) обе компании обновили свои линейки четырёхядерных процессоров. Intel представила семейство Core i7, состоящее из трех моделей, работающих на разных частотах. Основными изюминками данного процессора является использование трехканального контроллера памяти (типа DDR-3) и технологии эмулирования восьми ядер (полезно для некоторых специфических задач). Кроме того, благодаря общей оптимизации архитектуры удалось значительно повысить производительность процессора во многих типах задач. Слабой сторной платформы, использующей Core i7 является ее чрезмерная стоимость, так как для установки данного процессора необходима дорогая материнская плата на чипсете Intel-X58 и трехканальный набор памяти типа DDR3, также имеющий на данный момент высокую стоимость.

Компания AMD в свою очередь представила линейку процессоров Phenom II X4. При её разработке компания учла свои ошибки: был увеличен объем кэша (явно недостаточный у первого «Фенома»), а производство процессора было переведено на 45 нм техпроцесс, позволивший снизить тепловыделение и значительно повысить рабочие частоты. В целом AMD Phenom II X4 по производительности стоит вровень с процессорами Intel предыдущего поколения (ядро Yorkfield) и весьма значительно отстает от Intel Core i7. Однако, принимая во внимание умеренную стоимость платформы на базе этого процессора, его рыночные перспективы выглядят куда более радужно чем у предшественника.

Кэширование

Кэширование — это использование дополнительной быстродействующей памяти (кэш-памяти) для хранения копий блоков информации из основной (оперативной) памяти, вероятность обращения к которым в ближайшее время велика.

Различают кэши 1-, 2- и 3-го уровней. Кэш 1-го уровня имеет наименьшую латентность (время доступа), но малый размер, кроме того кэши первого уровня часто делаются многопортовыми. Так, процессоры AMD K8 умели производить 64 бит запись+64 бит чтение либо два 64-бит чтения за такт, AMD K8L может производить два 128 бит чтения или записи в любой комбинации, процессоры Intel Core 2 могут производить 128 бит запись+128 бит чтение за такт. Кэш 2-го уровня обычно имеет значительно большие латентности доступа, но его можно сделать значительно больше по размеру. Кэш 3-го уровня самый большой по объёму и довольно медленный, но всё же он гораздо быстрее, чем оперативная память.

Параллельная архитектура

Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных ни требовалось обработать, каждый его байт должен будет пройти через центральный процессор, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана.

Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах.

Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна):

Технология изготовления процессоров

История развития процессоров

Параллельно развиваются микропроцессоры, взявшие за основу стековую вычислительную модель.

Современная технология изготовления

![]()

В современных компьютерах процессоры выполнены в виде компактного модуля (размерами около 5×5×0,3 см) вставляющегося в ZIF-сокет. Большая часть современных процессоров реализована в виде одного полупроводникового кристалла, содержащего миллионы, а с недавнего времени даже миллиарды транзисторов. В первых компьютерах процессоры были громоздкими агрегатами, занимавшими подчас целые шкафы и даже комнаты, и были выполнены на большом количестве отдельных компонентов.

В начале 1970-х годов благодаря прорыву в технологии создания БИС и СБИС (больших и сверхбольших интегральных схем), микросхем, стало возможным разместить все необходимые компоненты ЦП в одном полупроводниковом устройстве. Появились так называемые микропроцессоры. Сейчас слова микропроцессор и процессор практически стали синонимами, но тогда это было не так, потому что обычные (большие) и микропроцессорные ЭВМ мирно сосуществовали ещё по крайней мере 10-15 лет, и только в начале 80-х годов микропроцессоры вытеснили своих старших собратьев. Надо сказать что переход к микропроцессорам позволил потом создать персональные компьютеры, которые теперь проникли почти в каждый дом.

Первый микропроцессор Intel 4004 был представлен 15 ноября 1971 года корпорацией Intel. Он содержал 2300 транзисторов, работал на тактовой частоте 108 кГц и стоил 300$.

За годы существования технологии микропроцессоров было разработано множество различных их архитектур. Многие из них (в дополненном и усовершенствованном виде) используются и поныне. Например Intel x86, развившаяся вначале в 32 бит IA32 а позже в 64 бит x86-64. Процессоры архитектуры x86 вначале использовались только в персональных компьютерах компании IBM (IBM PC), но в настоящее время всё более активно используются во всех областях компьютерной индустрии, от суперкомпьютеров до встраиваемых решений. Также можно перечислить такие архитектуры как Alpha, SPARC, MIPS (RISC — архитектуры) и EPIC-архитектура).

Большинство процессоров используемых в настоящее время являются Intel-совместимыми, то есть имеют набор инструкций и пр., как процессоры компании Intel, AMD и 8086, i286 (в русском компьютерном сленге называется «двойка», «двушка»), i386 («тройка», «трёшка»), i486 («четвёрка»), Pentium II, Pentium III, Pentium 4, Core 2 Duo, Itanium и др. AMD имеет в своей линейке процессоры Amx86 (сравним с Intel 486), Sempron (сравним с Intel Celeron), Athlon 64, Athlon 64 X2,

Будущие перспективы

В ближайшие 10-20 лет, скорее всего, изменится материальная часть процессоров ввиду того, что технологический процесс достигнет физических пределов производства. Возможно, это будут:

Квантовые процессоры

Процессоры, работа которых всецело базируется на квантовых эффектах. В настоящее время ведутся работы над созданием рабочих версий квантовых процессоров.

Российские микропроцессоры

Разработкой микропроцессоров в России занимается ЗАО «МЦСТ». Им разработаны и внедрены в производство универсальные RISC-микропроцессоры с проектными нормами 130 и 350 нм. Завершена разработка суперскалярного процессора нового поколения Эльбрус. Основные потребители российских микропроцессоров — предприятия ВПК.

Читайте также: