Логическими элементами какого устройства компьютера являются сумматор и полусумматор

Обновлено: 03.07.2024

Тема: Логические основы компьютера.

1. Основы логики.

Логика – наука о законах и формах мышления.

Высказывание (суждение) – некоторое предложение, которое может быть истинно (верно) или ложно.

Утверждение – суждение, которое требуется доказать или опровергнуть.

Рассуждение – цепочка высказываний или утверждений, определенным образом связанных друг с другом.

Умозаключение – логическая операция, в результате которой из одного или нескольких данных суждений получается (выводится) новое суждение.

Логическое выражение – запись или устное утверждение, в которое, наряду с постоянными, обязательно входят переменные величины (объекты). В зависимости от значений этих переменных логическое выражение может принимать одно из двух возможных значений: ИСТИНА (логическая 1) или ЛОЖЬ (логический 0).

Сложное логическое выражение – логическое выражение, составленное из одного или нескольких простых (или сложных) логических выражений, связанных с помощью логических операций.

2. Логические элементы компьютера. Схемы логических элементов и их таблицы истинности.

Как при строительстве дома применяют различного рода типовые блоки – кирпичи, рамы, двери и т.п., так и при разработке компьютера используют типовые электронные схемы. Каждая схема состоит из определенного набора типовых электронных элементов.

Электронным элементом называется соединение различных деталей, в первую очередь – диодов и транзисторов, а также резисторов и конденсаторов, в виде электрической схемы, выполняющей некоторую простейшую функцию.

Электронный элемент, реализующий логическую функцию, называется логическим элементом.

Логический элемент компьютера – это часть электронной логической схемы, которая реализует элементарную логическую функцию.

Тысячи микроскопических электронных переключателей в кристалле интегральной схемы сгруппированы в системы, выполняющие логические операции, т.е. операции с предсказуемыми результатами, и арифметические операции над двоичными числами. Соединенные в различные комбинации, логические элементы дают возможность компьютеру решать задачи, используя язык двоичных кодов.

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и др. (называемые также вентилями), а также триггер, регистр, сумматор.

Триггер – это логическая схема, способная сохранять одно из двух состояний до подачи нового сигнала на вход. Это, по сути, разряд памяти, способный хранить 1 бит информации.

Регистр – это устройство, состоящее из последовательности триггеров. Регистр предназначен для хранения многоразрядного двоичного числового кода, которым можно представлять и адрес, и команду, и данные.

Сумматор – это устройство, предназначенное для суммирования двоичных кодов.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния «1» и «0» в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению «истина» («1»), а низкий – значение «ложь («0»).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности – это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значениями истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

Знания из области математической логики можно использовать для конструирования электронных устройств. Нам известно, что 0 и 1 в логике не просто цифры, а обозначение состояний какого-то предмета нашего мира, условно называемых "ложь" и "истина". Таким предметом, имеющим два фиксированных состояния, может быть электрический ток.

Логический элемент компьютера - это часть электронной логической схемы, которая реализует элементарную логическую функцию.

Логические элементы имеют один или несколько входов и один выход, через которые проходят электрические сигналы, обозначаемые условно 0, если "отсутствует" электрический сигнал, и 1, если "имеется" электрический сигнал.

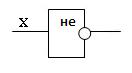

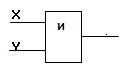

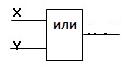

При проектировании и разработке ЭВМ выбирается набор элементов, из которых составляются схемы функциональных устройств. Элементы интегральных схем, реализующие логические операции над двоичными переменными называют логическими элементами. На принципиальных электрических схемах логические элементы изображаются прямоугольниками с обозначением входов и выходов (рис. 21).

Рис. 21. Логические элементы НЕ, И, ИЛИ

На логических элементах построены чуть более сложные логические микросхемы. Это триггеры, регистры и сумматоры.

Триггер – это основной элемент ЭВМ устройство, имеющее два устойчивых состояния, 0 и 1.

Триггер используется для хранения одного бита информации. Из логических элементов и триггеров создаются схемы узлов ЭВМ, функционально предназначенные для выполнения операций запоминания, преобразования, пересылки машинных слов или их частей. К ним относятся регистр, сумматор, счетчик, дешифратор, мультиплексор, таймер и т.д.

Пример. Сколько триггеров достаточно для запоминания 1 бита информации?

Решение. Для запоминания 1 бита информации достаточно 1 триггера забудем, что число является отрицательным. Ответ: Х = –25.

Регистр – узел ЭВМ, предназначенный для хранения одного машинного слова. Он представляет совокупность триггеров, число которых соответствует числу разрядов в слове и схем, обеспечивающих выполнение ряда операций:

4. сброс (установка в 0),

5. передача и прием слова,

6. сдвиг слова и т.д.

В соответствии с типом хранящегося машинного слова регистрам присваиваются наименования, например, регистр команд, индексный регистр, регистр адреса и т.д.

Сумматор - узел АЛУ, посредством которого осуществляется суммирование чисел.

Все математические операции в микропроцессорах сводятся к одной – к сложению.

Таблица состояний логических операций

| a | b | a & b | a | b | a ^ b | имп. | экв. |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 |

Примечание 1. Порядок вычисления логических выражений в языках программирования меняют посредствам скобок.

Примечание 2. Схемотехника – научно-техническое направление, охватывающее проблемы анализа и синтеза электронных устройств радиотехники, связи, автоматики, вычислительной техники и др. в целях обеспечения оптимального выполнения ими заданных функций и расчета параметров, входящих в них элементов.

Предусматривающая поддержку лишь четырех логических операций: "НЕ", "И", "ИЛИ", "Исключающее ИЛИ". Импликация и эквиваленция – не используются (реализуются более простыми операциями).

Базовые логические элементы реализуют три основные логические операции: «И», «ИЛИ», «НЕ».

Логический элемент «НЕ» (инвертор) представлен на рисунок 21.

Простейшим логическим элементом является инвертор, выполняющий функцию отрицания. Если на вход поступает сигнал, соответствующий 1, то на выходе будет 0. И наоборот.

У этого элемента один вход и один выход. На функциональных схемах он обозначается:

Рис. 21. Логический элемент «НЕ» (инвертор)

Говорят также, что элемент «НЕ» инвертирует значение входной двоичной переменной.

Логический элемент «И» (конъюнктор) выдает на выходе значение логического произведения входных сигналов.

Он имеет один выход и не менее двух входов (рис. 22). На функциональных схемах он обозначается:

Рис. 22. Логический элемент «И» (конъюнктор)

Сигнал на выходе конъюнктора появляется тогда и только тогда, когда поданы сигналы на все входы. На элементарном уровне конъюнкцию можно представить себе в виде последовательно соединенных выключателей. Известным примером последовательного соединения проводников является елочная гирлянда: она горит, когда все лампочки исправны. Если же хотя бы одна из лампочек перегорела, то гирлянда не работает.

Логический элемент «ИЛИ» (дизъюнктор) выдает на выходе значение логической суммы входных сигналов. Он имеет один выход и не менее двух входов (рис.23). На функциональных схемах он обозначается:

Рис. 23. Логический элемент «И» (конъюнктор)

Сигнал на выходе дизъюнктора не появляется тогда и только тогда, когда на все входы не поданы сигналы.

На элементарном уровне дизъюнкцию можно представить себе в виде параллельно соединенных выключателей.

Примером параллельного соединения проводников является многорожковая люстра: она не работает только в том случае, если перегорели все лампочки сразу.

Пример. Составьте логическую схему для логического выражения: F=A\/B/\ A.

1. Две переменные – А и В.

2. Две логические операции: 1-/\, 2-\/.

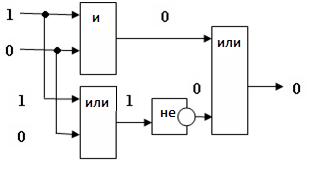

Пример. Постройте логическую схему, соответствующую логическому выражению F=А/\В\/(В\/А). Вычислить значения выражения для А=1, В=0.

1. Переменных две: А и В;

2. Логических операций три: /\ и две \/; А/\В\/ (В\/ А).

3. Схему строим слева направо в соответствии с порядком логических операций:

4. Вычислим значение выражения: F=1 /\ 0 \/ (0 \/ 1)=0.

Решение логических задач

Разнообразие логических задач очень велико. Способов их решения тоже немало. Но наибольшее распространение получили следующие три способа решения логических задач:

· средствами алгебры логики;

· с помощью рассуждений.

Познакомимся с ними поочередно.

Решение логических задач средствами алгебры логики.

Обычно используется следующая схема решения:

1. изучается условие задачи;

2. вводится система обозначений для логических высказываний;

3. конструируется логическая формула, описывающая логические связи между всеми высказываниями условия задачи;

4. определяются значения истинности этой логической формулы;

5. из полученных значений истинности формулы определяются значения истинности введённых логических высказываний, на основании которых делается заключение о решении.

Пример. Трое друзей, болельщиков автогонок "Формула-1", спорили о результатах предстоящего этапа гонок.

- Вот увидишь, Шумахер не придет первым, - сказал Джон. Первым будет Хилл.

- Да нет же, победителем будет, как всегда, Шумахер, - воскликнул Ник. - А об Алези и говорить нечего, ему не быть первым.

Питер, к которому обратился Ник, возмутился:

- Хиллу не видать первого места, а вот Алези пилотирует самую мощную машину.

По завершении этапа гонок оказалось, что каждое из двух предположений двоих друзей подтвердилось, а оба предположения третьего из друзей оказались неверны. Кто выиграл этап гонки?

Решение. Введем обозначения для логических высказываний: Ш - победит Шумахер; Х - победит Хилл; А - победит Алези.

Реплика Ника "Алези пилотирует самую мощную машину" не содержит никакого утверждения о месте, которое займёт этот гонщик, поэтому в дальнейших рассуждениях не учитывается.

Зафиксируем высказывания каждого из друзей: Джон: Ш/\Х, Ник: Ш/\А, Питер: Х.

Учитывая то, что предположения двух друзей подтвердились, а предположения третьего неверны, запишем и упростим истинное высказывание

Высказывание Ш /\ А/\ Х истинно только при Ш=1, А=0, Х=0.

Ответ. Победителем этапа гонок стал Шумахер.

Решение логических задач табличным способом.

При использовании этого способа условия, которые содержит задача, и результаты рассуждений фиксируются с помощью специально составленных таблиц.

Пример. "Симфонический оркестр". В симфонический оркестр приняли на работу трёх музыкантов: Брауна, Смита и Вессона, умеющих играть на скрипке, флейте, альте, кларнете, гобое и трубе.

1. Смит самый высокий;

2. играющий на скрипке меньше ростом играющего на флейте;

3. играющие на скрипке и флейте и Браун любят пиццу;

4. когда между альтистом и трубачом возникает ссора, Смит мирит их;

5. Браун не умеет играть ни на трубе, ни на гобое.

Определите, на каких инструментах играет каждый из музыкантов, если каждый владеет двумя инструментами?

Решение. Составим таблицу и отразим в ней условия задачи, заполнив соответствующие клетки цифрами 0 и 1 в зависимости от того, ложно или истинно соответствующее высказывание. Так как музыкантов трoе, инструментов шесть и каждый владеет только двумя инструментами, получается, что каждый музыкант играет на инструментах, которыми остальные не владеют.

Из условия 4 следует, что Смит не играет ни на альте, ни на трубе, а из условий 3 и 5, что Браун не умеет играть на скрипке, флейте, трубе и гобое. Следовательно, инструменты Брауна — альт и кларнет. Занесем это в таблицу, а оставшиеся клетки столбцов "альт" и "кларнет" заполним нулями:

| скрипка | флейта | альт | кларнет | гобой | труба | |

| Браун | 0 | 0 | 1 | 1 | 0 | 0 |

| Смит | 0 | 0 | 0 | |||

| Вессон | 0 | 0 |

Из таблицы видно, что на трубе может играть только Вессон.

Из условий 1 и 2 следует, что Смит не скрипач. Так как на скрипке не играет ни Браун, ни Смит, то скрипачом является Вессон. Оба инструмента, на которых играет Вессон, теперь определены, поэтому остальные клетки строки "Вессон" можно заполнить нулями:

| скрипка | флейта | альт | кларнет | гобой | труба | |

| Браун | 0 | 0 | 1 | 1 | 0 | 0 |

| Смит | 0 | 0 | 0 | 0 | ||

| Вессон | 1 | 0 | 0 | 0 | 0 | 1 |

Из таблицы видно, что играть на флейте и на гобое может только Смит.

| скрипка | флейта | альт | кларнет | гобой | труба | |

| Браун | 0 | 0 | 1 | 1 | 0 | 0 |

| Смит | 0 | 1 | 0 | 0 | 1 | 0 |

| Вессон | 1 | 0 | 0 | 0 | 0 | 1 |

Ответ: Браун играет на альте и кларнете, Смит - на флейте и гобое, Вессон - на скрипке и трубе.

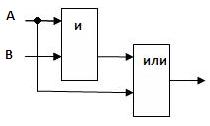

Поскольку любая логическая операция может быть представлена в виде комбинации трех базовых операций (И, ИЛИ, НЕ), любые устройства компьютера, производящие обработку или хранение информации, могут быть собраны из базовых логических элементов как из кирпичиков. Логический элемент И. На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического умножения (рис. 11). Логический элемент ИЛИ. На входы Аи В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического сложения (рис. 12). Логический элемент НЕ. На вход А логического элемента последовательно подаются два сигнала, на выходе получается последовательность из двух сигналов, значения которых определяются в соответствии с таблицей истинности логического отрицания (рис. 13). Сумматор. В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора является сумматор, который обеспечивает такое сложение. При сложении двоичных чисел образуется сумма в данном разряде, при этом возможен перенос в старший разряд. Обозначим слагаемые (А, В), перенос (Р) и сумму (S). Построим таблицу сложения одноразрядных двоичных чисел с учетом переноса в старший разряд (табл. 4).

Теперь, на основе полученного логического выражения, можно построить из базовых логических элементов схему полусумматора (рис. 14). Данная схема называется полусумматором, так как выполняет суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда. Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключен ко входу сумматора старшего разряда. Триггер. Важнейшей структурной единицей оперативной памяти компьютера, а также внутренних регистров процессора является триггер (рис. 15). Это устройство позволяет запоминать, хранить и считывать информацию (каждый триггер может хранить 1 бит информации). Для построения триггера достаточно двух логических элементов «ИЛИ» и двух элементов «НЕ».В обычном состоянии на входы триггера подан сигнал «О», и триггер хранит «О». Для записи «1» на вход S (установочный) подается сигнал «1». При последовательном рассмотрении прохождения сигнала по схеме видно, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе S исчезнет. Триггер запомнил «1», т. е. с выхода триггера Q можно считать «1». Чтобы сбросить информацию и подготовиться к приему новой, на вход R (сброс) подается сигнал «1», после чего триггер возвратится к исходному «нулевому» состоянию.7. РЕГИСТРЫ

Регистры - это устройства, выполняющие функции приема, хранения и передачи информации в виде т-разрядного двоичного кода.

Основным классификационным признаком регистров являются способ записи двоичного кода в регистр и его выдача, т.е. различают параллельные, последовательные (сдвигающие) и параллельно-последовательные регистры. Параллельный регистр выполняет операцию записи параллельным кодом. Последовательный регистр осуществляет запись последовательным кодом, начиная с младшего или старшего разряда, путем последовательного сдвига кода тактирующими импульсами. Параллельно-последовательные регистры имеют входы как для параллельной, так и для последовательной записи кода числа. Кроме того, сдвигающие регистры делятся на одно- и двунаправленные (реверсивные). Однонаправленные регистры осуществляют сдвиг кода влево или вправо,а двунаправленные - и влево, и вправо.

Основой построения регистров являются синхронные RS-триггеры или, предпочтительнее, В-триггеры. Принцип построения простейшего параллельного т-разрядного регистра показан на рис. 208.

В параллельном регистре цифры кода подаются на D-вход соответствующих триггеров. Запись осуществляется при подаче логической единицы на вход С. Код снимается с выходов Q. Параллельные регистры служат только для хранения информации в виде параллельного двоичного кода и для преобразования прямого кода в обратный и наоборот.

Последовательные регистры, помимо хранения информации, способны преобразовывать последовательный код в параллельный и наоборот. При построении последовательных регистров триггеры соединяются последовательно путем подключения выхода Q i-го триггера ко входу D i-го триггера, как это показано на рис. 209.

В последовательных регистрах принципиально необходимо, чтобы новый сигнал на выходе Q ш-го триггера возникал только после окончания синхросигнала. Для выполнения этого условия в последовательных регистрах необходимо применять двухступенчатые триггеры.

При действии каждого очередного тактового импульса код, содержащийся в регистре, сдвигается на один разряд. Для схемы, приведенной на рис.209, сдвиг кода происходит вправо (в сторону младших разрядов). Действительно, сигнал выхода Q i+1-го триггера действует на вход D i-го триггера, а сигнал выхода Q i-го триггера действует на вход D i-1-го триггера. При действии синхросигнала i-й триггер примет состояние i+1-го, а i-1-й - состояние i-го триггера, т.е., произойдет сдвиг кода вправо на один разряд.

Параллельный двоичный код одновременно снимается с выходов Q триггеров. Для сдвига кода влево необходимо, чтобы сигнал с выхода Q i-1-го триггера подавался на вход Q i-го (старшего) триггера.

Реверсивные регистры должны содержать логические схемы управления, обеспечивающие прохождение сигнала с выхода Q i-го триггера на вход D i-1-го триггера при сдвиге кода вправо и прохождение этого же сигнала на вход D i+1-го при реализации сдвига кода влево. Схема построения реверсивного регистра приведена на рис. 210.

Направление сдвига кода определяется подачей требуемых сигналов управления на соответствующие входы. Так, в схеме, показанной на рис. 210, при подаче на вход S0 напряжения логической единицы сдвиг кода будет происходить влево (в сторону старших разрядов), поскольку логическая схема управления 2И - 2И - 2ИЛИ будет разрешать прохождение сигналов с выходов Q i-го триггера на вход D i-го триггера, и наоборот, при подаче на вход S1 напряжения логической единицы будет разрешено прохождение сигнала с выхода Q i-го триггера на вход D i1-го триггера - будет реализовываться сдвиг кода вправо (в сторону младших разрядов).

Условно-графическое обозначение параллельного, сдвигового и реверсивного регистров приведено на рис. 211.

Выводы микросхем, показанных на рис. 211, следующие: D1-DN - входы D-триггеров соответствующих разрядов при записи информации в параллельном коде; Q1-QN - прямые выходы Q-триггеров; С - вход тактовых импульсов; R - вход обнуления; S0,S1 - входы управления направлением сдвига; VR - вход последовательного кода при сдвиге вправо (R - от англ. Right), при сдвиге кода влево применяется обозначение VL - (Left).

Основную массу регистров, применяемых на практике, представляют регистры сдвига, т.к. помимо операции хранения они могут осуществлять преобразование параллельного кода в последовательный и наоборот, прямого кода - в обратный и наоборот, выполнять арифметические и логические операции, временную задержку и деление частоты.

Типы и некоторые параметры регистров, содержащихся в основных сериях применяемых микросхем, приведены в таблице 31.

Условные обозначения регистров, приведенных в таблице 31, показаны на рисунках 212-247

Поскольку любая логическая операция может быть представлена в виде комбинации трех базовых операций (И, ИЛИ, НЕ), любые устройства компьютера, производящие обработку или хранение информации, могут быть собраны из базовых логических элементов как из кирпичиков. Логический элемент И. На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического умножения (рис. 11). Логический элемент ИЛИ. На входы Аи В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического сложения (рис. 12). Логический элемент НЕ. На вход А логического элемента последовательно подаются два сигнала, на выходе получается последовательность из двух сигналов, значения которых определяются в соответствии с таблицей истинности логического отрицания (рис. 13). Сумматор. В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора является сумматор, который обеспечивает такое сложение. При сложении двоичных чисел образуется сумма в данном разряде, при этом возможен перенос в старший разряд. Обозначим слагаемые (А, В), перенос (Р) и сумму (S). Построим таблицу сложения одноразрядных двоичных чисел с учетом переноса в старший разряд (табл. 4).

Теперь, на основе полученного логического выражения, можно построить из базовых логических элементов схему полусумматора (рис. 14). Данная схема называется полусумматором, так как выполняет суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда. Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключен ко входу сумматора старшего разряда. Триггер. Важнейшей структурной единицей оперативной памяти компьютера, а также внутренних регистров процессора является триггер (рис. 15). Это устройство позволяет запоминать, хранить и считывать информацию (каждый триггер может хранить 1 бит информации). Для построения триггера достаточно двух логических элементов «ИЛИ» и двух элементов «НЕ».В обычном состоянии на входы триггера подан сигнал «О», и триггер хранит «О». Для записи «1» на вход S (установочный) подается сигнал «1». При последовательном рассмотрении прохождения сигнала по схеме видно, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе S исчезнет. Триггер запомнил «1», т. е. с выхода триггера Q можно считать «1». Чтобы сбросить информацию и подготовиться к приему новой, на вход R (сброс) подается сигнал «1», после чего триггер возвратится к исходному «нулевому» состоянию.7. РЕГИСТРЫ

Регистры - это устройства, выполняющие функции приема, хранения и передачи информации в виде т-разрядного двоичного кода.

Основным классификационным признаком регистров являются способ записи двоичного кода в регистр и его выдача, т.е. различают параллельные, последовательные (сдвигающие) и параллельно-последовательные регистры. Параллельный регистр выполняет операцию записи параллельным кодом. Последовательный регистр осуществляет запись последовательным кодом, начиная с младшего или старшего разряда, путем последовательного сдвига кода тактирующими импульсами. Параллельно-последовательные регистры имеют входы как для параллельной, так и для последовательной записи кода числа. Кроме того, сдвигающие регистры делятся на одно- и двунаправленные (реверсивные). Однонаправленные регистры осуществляют сдвиг кода влево или вправо,а двунаправленные - и влево, и вправо.

Основой построения регистров являются синхронные RS-триггеры или, предпочтительнее, В-триггеры. Принцип построения простейшего параллельного т-разрядного регистра показан на рис. 208.

В параллельном регистре цифры кода подаются на D-вход соответствующих триггеров. Запись осуществляется при подаче логической единицы на вход С. Код снимается с выходов Q. Параллельные регистры служат только для хранения информации в виде параллельного двоичного кода и для преобразования прямого кода в обратный и наоборот.

Последовательные регистры, помимо хранения информации, способны преобразовывать последовательный код в параллельный и наоборот. При построении последовательных регистров триггеры соединяются последовательно путем подключения выхода Q i-го триггера ко входу D i-го триггера, как это показано на рис. 209.

В последовательных регистрах принципиально необходимо, чтобы новый сигнал на выходе Q ш-го триггера возникал только после окончания синхросигнала. Для выполнения этого условия в последовательных регистрах необходимо применять двухступенчатые триггеры.

При действии каждого очередного тактового импульса код, содержащийся в регистре, сдвигается на один разряд. Для схемы, приведенной на рис.209, сдвиг кода происходит вправо (в сторону младших разрядов). Действительно, сигнал выхода Q i+1-го триггера действует на вход D i-го триггера, а сигнал выхода Q i-го триггера действует на вход D i-1-го триггера. При действии синхросигнала i-й триггер примет состояние i+1-го, а i-1-й - состояние i-го триггера, т.е., произойдет сдвиг кода вправо на один разряд.

Параллельный двоичный код одновременно снимается с выходов Q триггеров. Для сдвига кода влево необходимо, чтобы сигнал с выхода Q i-1-го триггера подавался на вход Q i-го (старшего) триггера.

Реверсивные регистры должны содержать логические схемы управления, обеспечивающие прохождение сигнала с выхода Q i-го триггера на вход D i-1-го триггера при сдвиге кода вправо и прохождение этого же сигнала на вход D i+1-го при реализации сдвига кода влево. Схема построения реверсивного регистра приведена на рис. 210.

Направление сдвига кода определяется подачей требуемых сигналов управления на соответствующие входы. Так, в схеме, показанной на рис. 210, при подаче на вход S0 напряжения логической единицы сдвиг кода будет происходить влево (в сторону старших разрядов), поскольку логическая схема управления 2И - 2И - 2ИЛИ будет разрешать прохождение сигналов с выходов Q i-го триггера на вход D i-го триггера, и наоборот, при подаче на вход S1 напряжения логической единицы будет разрешено прохождение сигнала с выхода Q i-го триггера на вход D i1-го триггера - будет реализовываться сдвиг кода вправо (в сторону младших разрядов).

Условно-графическое обозначение параллельного, сдвигового и реверсивного регистров приведено на рис. 211.

Выводы микросхем, показанных на рис. 211, следующие: D1-DN - входы D-триггеров соответствующих разрядов при записи информации в параллельном коде; Q1-QN - прямые выходы Q-триггеров; С - вход тактовых импульсов; R - вход обнуления; S0,S1 - входы управления направлением сдвига; VR - вход последовательного кода при сдвиге вправо (R - от англ. Right), при сдвиге кода влево применяется обозначение VL - (Left).

Основную массу регистров, применяемых на практике, представляют регистры сдвига, т.к. помимо операции хранения они могут осуществлять преобразование параллельного кода в последовательный и наоборот, прямого кода - в обратный и наоборот, выполнять арифметические и логические операции, временную задержку и деление частоты.

Типы и некоторые параметры регистров, содержащихся в основных сериях применяемых микросхем, приведены в таблице 31.

Условные обозначения регистров, приведенных в таблице 31, показаны на рисунках 212-247

Читайте также: