Тип процессорной архитектуры с минимальным набором команд называется

Обновлено: 04.07.2024

Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть системы, которая видна программисту.

Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники являются архитектуры CISC и RISC. Известны также архитектуры MISC и VLIW

Лидером в разработке микропроцессоров с полным набором команд (CISC - Complete Instruction Set Computer) считается компания Intel со своей серией x86 и Pentium. Эта архитектура является практическим стандартом для рынка микрокомпьютеров.

Архитектура процессоров компании Intel основана на системе команд CISC (Complex Instruction Set Computer) – полной системе команд переменной длины. Команды процессора могут иметь длину от 8 до 108 бит, и процессор должен последовательно декодировать инструкцию после определения её границ. Первые процессоры для персональных компьютеров были скалярными устройствами ( то есть могли в каждый момент времени выполнять только одну команду), конвейерная обработка ( то есть одновременное выполнение нескольких команд на разных стадиях конвейера применялась лишь в больших ЭВМ).

Для CISC-процессоров характерно:

Ø сравнительно небольшое число регистров общего назначения;

Ø большое количество машинных команд, некоторые, из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов;

Ø большое количество методов адресации;

Ø большое количество форматов команд различной разрядности;

Ø преобладание двухадресного формата команд;

Ø наличие команд обработки типа регистр-память.

Позже появились процессоры, основанные на архитектуре RISC (Reduced Instruction Set Computer) – сокращённом наборе команд компьютера фиксированной длины, которая была оптимизирована для суперскалярных (с возможностью выполнения нескольких команд одновременно) конвейерных вычислений.

Зачатки этой архитектуры уходят своими корнями к компьютерам CDC6600, разработчики которых (Торнтон, Крэй и др.) осознали важность упрощения набора команд для построения быстрых вычислительных машин. Эту традицию упрощения архитектуры С. Крэй с успехом применил при создании широко известной серии суперкомпьютеров компании Cray Research.

Однако окончательно понятие RISC в современном его понимании сформировалось на базе трех исследовательских проектов компьютеров: процессора 801 компании IBM, процессора RISC университета Беркли и процессора MIPS Стенфордского университета.

Для RISC-процессоров характерно:

Ø архитектура, отделяющая команды обработки от команд работы с памятью;

Ø эффективная конвейерная обработка;

Ø система команд разрабатывалась таким образом, чтобы выполнение любой команды занимало небольшое количество машинных тактов (предпочтительно один машинный такт);

Ø логика выполнения команд, с целью повышения производительности, ориентировалась на аппаратную, а не на микропрограммную реализацию (чтобы упростить логику декодирования команд использовались команды фиксированной длины и фиксированного формата);

Ø наличие достаточно большого регистрового файла (в типовых RISC-процессорах реализуются 32 или большее число регистров по сравнению с 8 - 16 регистрами в CISC-архитектурах), что позволяет большему объему данных храниться в регистрах на процессорном кристалле большее время и упрощает работу компилятора по распределению регистров под переменные;

Ø для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки.

Ко времени завершения университетских проектов (1983-1984 гг.) обозначился также прорыв в технологии изготовления сверхбольших интегральных схем. Простота архитектуры и ее эффективность, подтвержденная этими проектами, вызвали большой интерес в компьютерной индустрии и с 1986 года началась, активная промышленная реализация архитектуры RISC. К настоящему времени эта архитектура прочно занимает лидирующие позиции на мировом компьютерном рынке рабочих станций и серверов.

Развитие архитектуры RISC в значительной степени определялось прогрессом в области создания оптимизирующих программаторов (компиляторов). Именно современная техника программирования позволяет эффективно использовать преимущества большего регистрового файла, конвейерной организации и большей скорости выполнения команд. Современные компиляторы используют также преимущества другой оптимизационной техники для повышения производительности, обычно применяемой в процессорах RISC: реализацию задержанных переходов и суперскалярной обработки, позволяющей в один и тот же момент времени выдавать на выполнение несколько команд. Архитектуры процессоров CISC и RISC развивались практически независимо, однако в отдельных модификациях процессоров AMD удалось совместить обе архитектуры. То есть микроядро процессора работает на основе инструкций RISC, а специальный блок интерпретирует команды CISC для обеспечения совместимости с программами для процессоров х86.

Minimum instruction set computer — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип простоты, изначальный для RISC-процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал и перегнал многие CISC процессоры по сложности. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд).

Very long instruction word — сверхдлинное командное слово. Архитектура процессоров с явно выраженным параллелизмом вычислений, заложенным в систему команд процессора. Являются основой для архитектуры EPIC. Ключевым отличием от суперскалярных CISC-процессоров является то, что для них загрузкой исполнительных устройств занимается часть процессора (планировщик), на что отводится достаточно малое время, в то время как загрузкой вычислительных устройств для VLIW-процессора занимается компилятор, на что отводится существенно больше времени (качество загрузки и, соответственно, производительность теоретически должны быть выше). Примером VLIW-процессора является Intel Itanium.

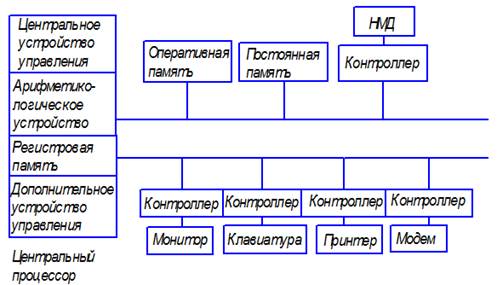

Центральный процессор в персональных компьютерах представляет собой микропроцессор, то есть, построен на одной микросхеме. В его состав входят:

•Центральное устройство управления - комплекс средств автоматического управления процессами передачи и обработки информации;

•Арифметико-логическое устройство - устройство, осуществляющее обработку информации и выработку признаков управляющих сигналов.

•Внутренняя память процессора:

-Постоянная память устройства управления.

Рис. 1 Обобщенная структурная схема ПК

Модули оперативной и постоянной памяти, связаны с микропроцессором напрямую. Остальные устройства (монитор, клавиатура, накопители на магнитных носителях и т.д.) связаны с микропроцессором через контроллеры ввода-вывода, которые, в свою очередь, связаны с микропроцессором через системную шину.

Микропроцессор является ядром ЭВМ. Он осуществляет обработку данных и функции управления системой. К функциям управления системой относятся:

•инициирование операций ввода-вывода;

•управление доступом к основной памяти;

•обработка системных событий – прерываний;

•организация многозадачных режимов работы.

Организация центрального процессора определяется архитектурой и принципами работы ЭВМ ( состав и форматы команд, организация памяти). Логическая структура включает ряд функциональных средств:

•средства обработки информации;

•средства управления системой и программами;

•управление интерфейсом и каналами.

Структурно эти средства разбиваются на центральное устройство управления, АЛУ, внутреннюю память и управляющие устройства, связанные с конкретными устройствами вычислительной машины.

Центральное устройство управления принимает и расшифровывает команды, формирует адреса команд и операндов, формирует последовательности управляющих сигналов и обеспечивает координацию работы всех функциональных узлов, посредством выработки синхронизирующих сигналов.

Внутренняя память входит в состав первого уровня и связана с АЛУ и другими блоками центрального процессора непосредственно и имеет скорость работы соизмеримую со скоростью работы блоков процессора.

•Управляющая память входит в состав центрального устройства управления и относится к классу постоянной памяти. Этот вид памяти используется для хранения микропрограмм. Ее отличает очень высокое быстродействие и небольшая емкость, определяющаяся количеством команд в системе команд центрального процессора.

•Регистровая память выполнена на триггерных элементах и входит в состав центрального процессора. Емкость ее невысока, скорость высокая, но меньше, чем у управляющей памяти. Основной характеристикой данного типа памяти является разрядность.

Понятие архитектуры процессора не имеет единого толкования, поскольку под ним понимаются две различные сущности. С программной позиции она представляет собой совместимость процессора с конкретным набором команд, его способность выполнять определённый набор кодов. То есть это способность программы, которая была собрана для архитектуры семейства x86, функционировать на всех x86-совместимых системах. На ARM системе такая программа работать не будет.

С аппаратной позиции архитектура процессора, называемая иногда микроархитектурой, является набором свойств, характерным для всего семейства процессоров и отражающим базовые особенности его внутренней организации. К примеру, микроархитектура процессоров Intel Pentium имела обозначение Р5, а процессоры Pentium 4 относились к NetBurst. После закрытия Intel микроархитектуры Р5 для производителей AMD разработала архитектуру К7 и К8 для процессоров Athlon, Athlon XP и Athlon 64 соответственно.

CISC

CISC-архитектура (Complex Instruction Set Computer) относится к процессорам с полным набором команд. Она имеет нефиксированную длину команд, отличается кодированием арифметических действий в единой команде и малым количеством регистров, большинство из которых выполняет только выделенную функцию.

CISC реализована во множестве типов микропроцессоров, таких как Pentium, которые выполняют большое количество разноформатных команд (порядка 200-300), применяя более десяти различных способов адресации. Командная система может включать несколько сотен команд различного уровня сложности или формата (от 1 до 15 байт).

Всё это делает возможным реализовывать эффективные алгоритмы для различных задач. В качестве примеров CISC-архитектуры, используемой преимущественно для десктопных версий, можно привести следующие процессоры:

- x86 (IA-32, сокращенное от "Intel Architecture, 32-bit") - ;

- x86_64 (AMD64);

- Motorola MC680x0;

- мейнфреймы zSeries.

В CISC-процессорах каждую из команд возможно заменить на аналогичную ей либо на группу выполняющих такую же функцию команд. Это формирует как достоинства, так и недостатки архитектуры: она обладает высокой производительностью благодаря возможности замены команд, но большей стоимостью в сравнении с RISC, что связано с усложнённой архитектурой, в которой существует множество сложных для раскодирования команд.

RISC-архитектура (Reduced Instruction Set Computer) относится к процессорам с сокращённым набором команд. В ней быстродействие увеличивается посредством упрощения инструкций: за счёт того, что их декодирование становится проще, уменьшается время исполнения. Изначально RISC-процессоры не обладали инструкциями деления и умножения и не могли работать с числами, имеющими плавающую запятую. Их появление связано с тем, что в CISC достаточно много способов адресации и команд использовались крайне редко.

Система команд в RISC состоит из малого числа часто применяемых команд одного формата, которые можно выполнить за единичный такт центрального процессора. Более сложные и редко применяемые команды выполняются на программном уровне. При этом, благодаря значительному увеличению скорости реализации команд, средняя производительность RISC-процессоров выше, чем у CISC.

Благодаря сокращению аппаратных средств, используемых для декодирования и реализации сложных команд, достигается значительное упрощение и снижение стоимости интегральных схем. В то же время возрастает производительность и снижается энергопотребление, что особенно актуально для мобильного сегмента. Эти же достоинства служат причиной использования во многих современных CISC-процессорах, например в последних моделях К7 и Pentium, RISC-ядра. Сложные CISC-команды заранее преобразуются в набор простых RISC-операций, которые оперативно выполняются RISC-ядром.

Характерными примерами RISC-архитектур являются:

- PowerPC;

- DEC Alpha;

- ARC;

- AMD Am29000;

- серия архитектур ARM;

- Atmel AVR;

- Intel i860 и i960;

- BlackFin;

- MIPS;

- PA-RISC;

- Motorola 88000;

- SuperH;

- RISC-V;

- SPARC.

RISC быстрее CISC, и даже при условии выполнения системой RISC четырёх или пяти команд вместо единственной, выполняемой CISC, RISC выигрывает в скорости, поскольку его команды выполняются в разы оперативнее. Однако CISC продолжает использоваться. Это связано с совместимостью: x86_64 продолжает лидировать в десктоп-сегменте, а поскольку старые программы могут функционировать только на x86, то и новые десктоп-системы должны быть x86(_64), чтобы дать возможность старым программам работать на новых устройствах.

Для Open Source это не проблема, ведь пользователь может найти в сети версию программы, подходящую для другой архитектуры. Однако создать версию проприетарной программы для другой архитектуры получится только у владельца исходного кода.

MISC

MISC-архитектура (Minimal Instruction Set Computer) является процессором с минимальным набором команд. Она отличается ещё большей простотой и используется для ещё большего снижения энергопотребления и итоговой стоимости процессора. MISC-архитектура применяется в IoT-сегменте и компьютерах малой стоимости вроде роутеров. Первой вариацией такого процессора стал MuP21.

В основе MISC-процессоров лежит укладка ряда команд в единое большое слово, что позволяет параллельно обрабатывать несколько потоков данных. MISC применяет стековую модель устройства и базовые слова языка Forth. Процессоры этой архитектуры отличаются малым числом наиболее востребованных команд и использованием длинных командных слов, что позволяет получить выполнение ряда непротиворечивых команд за единый цикл работы процессора. Порядок исполнения команд определяется так, чтобы максимально загрузить маршруты, пропускающие потоки данных.

Все вышеназванные архитектуры могут применять «спекулятивное исполнение команд», то есть исполнение команды заранее, когда ещё неизвестна её необходимость. Это позволяет увеличить производительность.

VLIW

VLIW-архитектура (Very Long Instruction Word) относится к микропроцессорам, применяющим очень длинные команды за счёт наличия нескольких вычислительных устройств. В отдельных полях команды присутствуют коды, которые обеспечивают реализацию различных операций. Одна команда в VLIW может исполнить одновременно несколько операций в разных узлах микропроцессора. Формированием таких длинных команд занимается соответствующий компилятор во время трансляции программ, которые написаны на высокоуровневом языке.

VLIW-архитектура, являясь достаточно перспективной для разработки нового поколения высокопроизводительных процессоров, реализована в некоторых современных микропроцессорах:

- Intel Itanium;

- AMD/ATI Radeon (с R600 до Northern Islands);

- серия «Эльбрус».

VLIW схожа с архитектурой CISC, имея собственный аналог спекулятивной реализации команд. Однако спекуляция выполняется не при работе программы, а при компиляции, что делает VLIW-процессоры устойчивыми к уязвимостям Spectre и Meltdown. Компиляторы в этой архитектуре привязаны к определённым процессорам. Так, в следующем поколении наибольшая длина одной команды может из 256 бит превратиться в 512 бит, и тогда придётся выбирать между обратной совместимостью со старым типом процессора и возрастанием производительности посредством компиляции под новый процессор. И в этом случае Open Sourсe даёт возможность получить программу под определённый процессор при помощи перекомпиляции.

Развитием указанных архитектур стали различные гибридные архитектуры. К примеру, современные x86_64 процессоры CISC-совместимы, однако имеют RISC-ядро. В этих CISC-процессорах CISC-инструкции переводятся в набор RISC-команд. Вероятно, в дальнейшем разнообразие гибридных архитектур только возрастёт.

Содержание

Общий обзор

На этом уровне определяются реализованные в микропроцессоре конкретного типа:

- архитектура памяти

- взаимодействие с внешними устройствами ввода/ вывода

- режимы адресации

- регистры

- машинные команды

- различные типы внутренних данных (например, с плавающей запятой, целочисленные типы и так далее)

- обработчики прерываний и исключительных состояний

Этот уровень расположен между уровнями микроархитектуры и операционной системы. Исторически этот уровень развился прежде всех остальных уровней и изначально был единственным. В наши дни этот уровень очень часто называют "архитектурой" машины, а иногда - "языком ассемблера".

Уровень архитектуры набора команд имеет особое значение: он является связующим звеном между программным и аппаратным обеспечением. Конечно, можно было бы сделать так, чтобы аппаратное обеспечение непосредственно выполняло программы, написанные на С, С++, Java или других языках высокого уровня, но это не очень хорошая идея. Преимущество компиляции перед интерпретацией было бы тогда потеряно. Кроме того, из чисто практических соображений компьютеры должны уметь выполнять программы, написанные на разных языках, а не только на одном.

Все разработчики считают, что нужно транслировать программы, написанные на различных языках высокого уровня, в некую общую для всех промежуточную форму - уровень архитектуры набора команд - и, соответственно, строить аппаратное обеспечение, которое сможет непосредственно выполнять программы этого уровня. Уровень архитектуры набора команд связывает компиляторы и аппаратное обеспечение. Это язык, который понятен и компиляторам, и устройствам. На рисунке 2 показана взаимосвязь компиляторов, уровня архитектуры набора команд и аппаратного обеспечения.

Когда появляется новая машина, первый вопрос, который задают все потенциальные покупатели: "Совместима ли машина с предыдущими версиями?" Второй вопрос: "Можно ли запустить на ней прежнюю операционную систему?" И третий вопрос: "Будут ли работать на этой машине прежние приложения и не потребуется ли заменять их новыми версиями?" Этот факт заставляет производителей компьютеров поддерживать один и тот же уровень команд в разных моделях или, по крайней мере, делать его обратно совместимым. Под обратной совместимостью мы понимаем способность новой машины выполнять старые программы без изменений. В то же время новая машина может поддерживать новые команды и иметь другие особенности, используемые новым программным обеспечением.

Какую архитектуру команд можно считать хорошей? Существуют два основных фактора. Во-первых, хорошая архитектура должна предлагать набор команд, которые можно эффективно реализовать не только в современной, но и в будущей технике. При плохо разработанной архитектуре команд процессор может строиться из большего числа вентилей, для выполнения программ может требоваться больший объем памяти и т. д. Проект, в котором должным образом учтены особенности конкретной техники, может стать основой для производства целого поколения компьютеров, прийти на смену которым сможет система с еще более совершенной архитектурой команд.

Во-вторых, хорошая архитектура команд должна обеспечивать предельную ясность в отношении того, какой именно должна быть откомпилированная программа. Регулярность и полнота вариантов - те черты, которые не всегда свойственны архитектуре команд. Эти черты особенно важны для компилятора, который не всегда может сделать оптимальный выбор из нескольких альтернатив, особенно если некоторые очевидные на первый взгляд альтернативы архитектурой команд не поддерживаются. Если говорить кратко, поскольку уровень архитектуры набора команд является промежуточным звеном между аппаратным и программным обеспечением, он должен быть приемлемым и для разработчиков аппаратного обеспечения (с точки зрения эффективной реализации), и для программистов (с точки зрения написания качественного кода). [2]

Классификация архитектур системы команд

Сложившуюся на настоящий момент ситуацию в области АСК иллюстрирует рисунок 3.

Среди мотивов, чаще всего предопределяющих переход к новому типу АСК, остановимся на двух наиболее существенных. Первый — это состав операций, выполняемых вычислительной машиной, и их сложность. Второй — место хранения операндов, что влияет на количество и длину адресов, указываемых в адресной части команд обработки данных.

По составу и сложности команд

Современная технология программирования ориентирована на языки высокого уровня, главная цель которых — облегчить процесс программирования. Но переход к ЯВУ породил серьезную проблему: сложные операторы, характерные для языков высокого уровня, существенно отличаются от простых машинных операций, реализуемых в большинстве вычислительных машин. Следствием такого несоответствия становится недостаточно эффективное выполнение программ. Проблема получила название семантического разрыва, а для ее разрешения разработчики вычислительных машин в настоящее время выбирают один из трех подходов и, соответственно, один из трех типов АСК:

- архитектура с полным набором команд: CISC (Complex Instruction Set Computer)

- архитектура с сокращенным набором команд: RISC (Reduced Instruction Set Computer);

- архитектура с командными словами сверхбольшой длины: VLIW (Very Long Instruction Word).

В CISC-архитектуре семантический разрыв преодолевается за счет расширения системы команд, дополнения ее сложными командами, семантически аналогичными операторам языков высокого уровня (ЯВУ). Для CISC-архитектуры типичны:

- наличие в процессоре сравнительно небольшого числа регистров общего назначения;

- большое количество машинных команд, часть из которых аппаратно реализуют сложные операторы ЯВУ;

- разнообразие способов адресации операндов;

- множество форматов команд различной разрядности;

- наличие команд, где обработка совмещается с обращением к памяти.

К типу CISC можно отнести практически все ВМ, выпускавшиеся до середины 1980-х годов, и значительную часть производящихся в настоящее время. Рассмотренный способ решения проблемы семантического разрыва вместе с тем ведет к усложнению аппаратуры вычислительных машин (ВМ), главным образом, устройства управления, что, в свою очередь, негативно сказывается на производительности ВМ в целом. Это обстоятельство побудило более внимательно проанализировать программы, получаемые после компиляции с ЯВУ. Был предпринят комплекс исследований, в результате которых обнаружилось, что доля дополнительных команд, эквивалентных операторам ЯВУ, в общем объеме программ не превышает 10–20%, а для некоторых наиболее сложных команд даже 0,2%. В то же время объем аппаратных средств, требуемых для реализации таких дополнительных команд, возрастает весьма существенно. Так, емкость микропрограммной памяти, хранящей микропрограммы выполнения всех команд ВМ, из-за введения сложных команд может увеличиваться на 60%

Анализ результатов упомянутых исследований привел к пересмотру традиционных решений, следствием чего стало появление RISC-архитектуры. Идея заключается в ограничении списка команд ВМ наиболее часто используемыми простейшими командами, оперирующими данными, размещенными только в регистрах процессоров. Обращение к памяти допускается лишь с помощью специальных команд чтения и записи. Резко уменьшено количество форматов команд и способов указания адресов операндов. Эти меры позволили существенно упростить аппаратные средства ВМ и повысить их быстродействие. Оказалось, что реализация сложных команд за счет последовательности из простых, но быстрых RISC-команд не менее эффективна, чем аппаратный вариант сложных команд в CISC-архитектуре. Элементы RISC-архитектуры впервые появились в вычислительных машинах CDC 6600 и супер-ЭВМ компании Cray Research. Достаточно успешно реализуется RISC-архитектура и в современных ВМ.

Помимо CISC- и RISC-архитектур, в общей классификации был упомянут еще один тип АСК — архитектура с командными словами сверхбольшой длины (VLIW). Концепция VLIW базируется на RISC-архитектуре, но в ней несколько простых RISC-команд объединяются в одну сверхдлинную команду и выполняются параллельно. В плане АСК архитектура VLIW сравнительно мало отличается от RISC. Появился лишь дополнительный уровень параллелизма вычислений.

По месту хранения операндов

Не меньшую роль при выборе АСК играет ответ на вопрос о том, где могут храниться операнды и каким образом к ним осуществляется доступ. С этих позиций различают следующие виды архитектур системы команд:

- стековую;

- аккумуляторную;

- регистровую;

- с выделенным доступом к памяти.

Выбор той или иной архитектуры влияет на принципиальные моменты: сколько адресов будет содержать адресная часть команд, какова будет длина этих адресов, насколько просто будет происходить доступ к операндам и какой, в конечном итоге, будет общая длина команд

Стековая архитектура

Стеком называется память, по своей структурной организации отличная от основной памяти ВМ. Стек образует множество логически взаимосвязанных ячеек (рис. 2.4), взаимодействующих по принципу «последним вошел, первым вышел» (LIFO, Last In First Out). Принцип действия стека проиллюстрирован на рисунке 4.

Мы где-то в начале статьи написали, что архитектур ы RISC и CISC очень похожи и грань между ними слегка размыта. Да, у обеих архитектур диаметрально противоположный подход к использованию процессора, но конкуренция тоже делает свое дело. Поэтому CISC и RISC стали «перенимать» друг у друга лучшие решения. К примеру, конвейеризация раньше никогда не была доступной в CISC, но именно этот процесс был способен «уничтожить» эту архитектуру на корню, поэтому создателям CISC нужно было срочно предпринять и сэмулировать конвейеризацию в своих процессорах. Что они и сделали: они «разбили» сложные инструкции CISC на более простые и назвали этот процесс «микрооперации». Это не конвейеризация и ничего общего с RISC-инструкциями не имеет, но работает по такому же принципу, что также ускоряет работу CISC-процессоров.

Конвейер в RISC практически постоянно заполнен инструкциями, а микрооперации в CISC не могут организовать постоянное заполнение конвейера, поэтому возникало очень много «пустот». Из-за этого разработчики CISC пошли на дополнительный трюк, так называемый гипертрединг. Гипертрединг позволил CISC-процессору выполнять сразу несколько потоков инструкций. В этом случае если один поток не способен «наполнить» конвейер, то для этого берутся инструкции из других потоков.

Разработчики RISC заметили, что гипертрединг — это хорошо. А в их архитектуре редко, но иногда проскакивает «пустота» в конвейере, поэтому они внедрили гипертрединг и в своих процессорах.

Такое «копирование функционала» сделало свое дело: архитектура RISC и архитектура CISC стали очень похожи. Но при этом многие специалисты пророчат светлое будущее именно архитектуре RISC.

Мы будем очень благодарны

если под понравившемся материалом Вы нажмёте одну из кнопок социальных сетей и поделитесь с друзьями.

Читайте также: