Lpc debug на материнской плате что это

Обновлено: 07.07.2024

Сегодня в персональном компьютере осталось только одно функциональное устройство, по которому можно проследить его генеалогию, — это интерфейс ISA, доставшийся ему по наследству от IBM PC AT. Большинство карт расширения выполняется по стандарту PCI, многие видеокарты подключаются по AGP. Однако производители карт расширения и материнских плат кивают друг на друга: если стандарт существует, то под него должны выпускаться карты; если выпускаются карты с интерфейсом ISA, то материнские платы должны его поддерживать. В спецификации PC98 наличие разъемов расширения стандарта ISA признается нежелательным. Однако для подсоединения таких устройств, как параллельные и последовательные порты, клавиатура, флоппи-диск, какой-нибудь интерфейс все же необходим. Поэтому разработчики микросхем для материнских плат вынуждены разводить ISA на кристалле, а чтобы добро не пропадало зря, — и выводить его наружу. Что же придет ему на смену?

Для подключения перечисленных выше устройств Intel предлагает новый стандарт — LPC (Low Pin Count, Малое Количество Контактов). Этот интерфейс, по утверждению представителей корпорации, будет встраиваться в будущие чипсеты для материнских плат. Такие намерения Intel означают, что, вероятнее всего, мы вскоре сможем в добровольно-принудительном порядке ознакомиться со стандартом LPC. Попробуем сделать это заранее и по собственной воле.

Введение нового стандарта преследует следующие цели:

- убрать из системы ISA и X-bus;

- снизить стоимость системы;

- обеспечить скорость обмена, не меньшую, чем по шине X-bus;

- предоставить те же типы циклов, что и X-bus;

- увеличить адресуемое пространство с традиционных 16 Мбайт до 4 Гбайт;

- значительно упростить временные диаграммы за счет синхронной природы интерфейса;

- обеспечить прозрачность для программного обеспечения и отсутствие конфликтов из-за ресурсов;

- обеспечить пригодность как для настольных, так и для мобильных систем;

- обеспечить функции управления потребляемой мощностью.

| Значение LAD[3:0] | Тип операции |

|---|---|

| 0 | Начало ввода/вывода или чтения/записи |

| 1 | Зарезервировано для последующего расширения |

| 10 | Разрешение для задатчика номер 1 |

| 11 | Разрешение для задатчика номер 2 |

| 0100-1110 | Зарезервировано для последующего расширения |

| 1111 | Принудительное прекращение цикла |

Следующее поле — CYCTYPE + DIR (Cycle Type / Direction, тип цикла и направление передачи), определяется текущим задатчиком. Это поле может иметь значения, указанные в табл. 3. Значение бита LAD[0] зарезервировано, и он всегда должен быть равен 0.

Поле SIZE (Размер) может принимать значения 00 при передаче 1 байта, 01 при передаче 2 байт и 11 при передаче 4 байт. Значение 10 зарезервировано. Это поле используется только при операциях прямого доступа; ввод/вывод и чтение/запись осуществляются побайтно. Поле ADDR имеет длину четыре периода тактовой частоты для операций ввода/вывода и восемь периодов для циклов обращения к памяти. Адреса передаются начиная со старшей тетрады, то есть при обращении к памяти первыми передаются биты 31:28, а последними — 3:0.

Поле CHANNEL используется в операциях прямого доступа к памяти и содержит в битах 0:2 номер канала, а в бите 3 — аналог сигнала Terminal Count шины ISA.

Поле DATA (Данные) имеет длину два периода тактовой частоты и содержит данные, передаваемые младшей тетрадой вперед. В одном цикле может содержаться одно, два или четыре поля DATA.

Поле передачи управления Turn Around, TAR, используется для передачи контроля над линиями LAD [3:0] второму участнику данного цикла, что необходимо при операциях чтения. Оно имеет продолжительность два периода тактовой частоты, на первом периоде текущий задатчик устанавливает на линиях LAD[3:0] значение 1111, на втором отключается, ожидая информацию от второго участника диалога.

Поле SYNC служит для синхронизации источника и приемника данных. Его вставляет ведомый участник цикла для того, чтобы подготовить для передачи запрошенные данные, или для размещения полученной информации. Полей SYNC в одном цикле может быть несколько, фактически столько, сколько нужно для подготовки. Значения поля SYNC приведены в табл. 4.

| LAD[3:0] | |

|---|---|

| 0 | Синхронизация достигнута |

| 0001-0100 | Зарезервировано |

| 101 | Короткое ожидание |

| 110 | Длительное ожидание, будет добавлено много полей SYNC |

| 0111-1000 | Зарезервировано |

| 1001 | Синхронизация достигнута, передача будет продолжена в следующем цикле (только при прямом доступе к памяти) |

| 1010 | Ошибка. В переданных данных содержится ошибка |

| 1011 — 1111 | Зарезервировано |

Значение 1010 — Ошибка необходимо потому, что все циклы должны иметь определенную длину, так что периферийное устройство обязано передать требуемое для данного цикла количество данных, но перед этим оно честно предупреждает задатчика о том, что эти данные имеют чисто фиктивный характер.

| Поле | Значение | Источник | Число тактов |

|---|---|---|---|

| START | 0 | Основной задатчик | 1 |

| CYCTYPE+DIR | 100 | Основной задатчик | 1 |

| ADDR | ХХХХ | Основной задатчик | 8 |

| TAR | 1111 | Основной задатчик | 2 |

| SYNC | 101 | Периферийное устройство | 3 |

| SYNC | 0 | Периферийное устройство | 1 |

| DATA | ХХХХ | Периферийное устройство | 2 |

| TAR | 1111 | Периферийное устройство | 2 |

| Всего тактов | 20 | ||

| Время доступа | 0,66 мкс | ||

| Скорость передачи | 1,5 Мбайт/с |

В табл. 5 приведены последовательность и характеристики полей в цикле чтения из памяти. Основной задатчик инициирует цикл, определяет тип цикла и направление передачи (чтение из памяти), адрес памяти и информирует об освобождении линий LAD[3:0]. Периферийное устройство во время подготовки данных передает поля SYNC со значением 0101. Когда данные готовы для передачи, устройство передает поле SYNC со значением 0000, две тетрады данных и информирует основного задатчика об освобождении линий LAD[3:0].

Количество полей синхронизации соответствует быстродействию памяти и может изменяться. В данном примере предполагалось наличие ППЗУ с временем доступа 120 нс (4*33 нс = 132 нс). Цикл записи построен примерно так же, но данные передает основной задатчик, а периферийное устройство — только поля SYNC и TAR. В поле SYNC устройство помещает значение либо 0000 (успешная запись), либо 1010 (ошибка при записи). Соответственно возможны варианты, когда устройство не буферизует данные, а выдает поля SYNC до момента реальной записи.

| Поле | Значение | Источник | Число тактов |

|---|---|---|---|

| START | 0 | Основной задатчик | 1 |

| CYCTYPE+DIR | 110 | Основной задатчик | 1 |

| ADDR | ХХХХ | Основной задатчик | 8 |

| DATA | ХХХХ | Основной задатчик | 2 |

| TAR | 1111 | Основной задатчик | 2 |

| SYNC | 0 | Периферийное устройство | 1 |

| TAR | 1111 | Периферийное устройство | 2 |

| Всего тактов | 17 | ||

| Время доступа | 0,56 мкс | ||

| Скорость передачи | 1,8 Мбайт/с |

В табл. 6 приведены последовательность и характеристики полей в цикле чтения из памяти. Совершенно аналогично происходит ввод/вывод при работе с портами, отличие состоит лишь в других значениях полей CYCTYPE+DIR. Для ознакомления с функциями работы с прямым доступом к памяти и управления потребляемой мощностью в табл. 7 приведены необязательные линии интерфейса LPC.

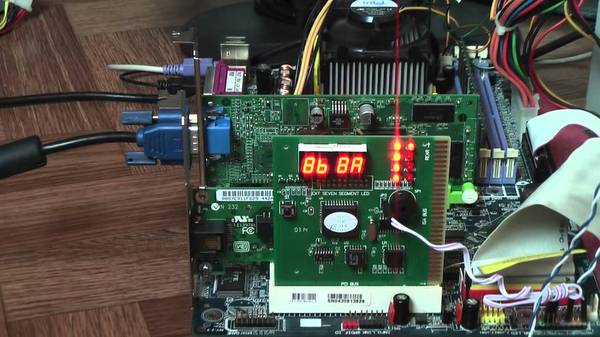

И начинаем с прошивки биоса. Не помогло? Подключаемся на внешку (может на CRT или на HDMI — должно появиться изображение). Затем подкидываем пост-карту. Многие считают что это лишняя трата времени, потому что пост может вообще ахинею показать, однако, в некоторых случаях, пост-карта позволяет существенно сузить круг поиска неисправности.

Находим в схеме, где у нас распаян LPC. Если он не идёт на mini PCI-E, то смотрим куда можно подпаять пост-карту (на некоторых платформах присутствует LPC Debug Port).

Немого поясню что же такое LPC. Это внутренняя низкоскоростная параллельно-последовательная шина для подключения к контроллеру ввода-вывода (ICH) низкоскоростных устройств (например микросхемы flash-BIOS и контроллера Super I/O, включающего в себя FDD, порт клавиатуры, LPT и COM-порты).

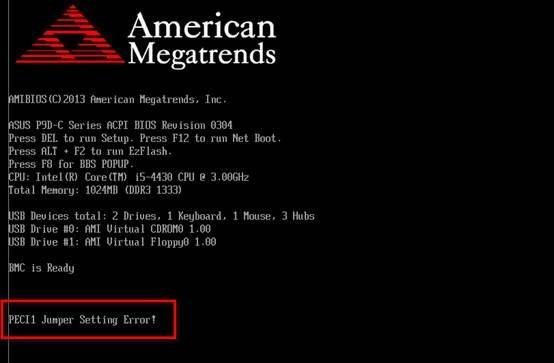

Итак, у нас есть пост код, остаётся его расшифровать. Данную информацию следует искать по производителю биоса или по вашей платформе. Не лишним будет проверить на форумах типовые неисправности вашей платформы (очень часто помогает).

Далее подкидываем проц и оперативку в разных вариациях (например одну планку в первом слоте, потом во втором, потом 2 планки сразу). Меряем сопротивления каналов RX/TX желательно на всех шинах (мерять надо относительно земли и относительно друг друга, RX не должен звониться накоротко с TX). Учитываем что на каждой шине своё сопротивление, отличие на отдельной шине более чем 50 Ом уже много и может означать что проблема скрыта на этом канале.

После меряем сопротивление относительно земли на кондесаторах под основными чипами (север, юг, видяха). На одинаковых кондёрах должно быть одинаковое сопротивление. Ну и, конечно, желательно скинуть всю переферию, дабы исключить всякие дохлые сетки или ещё что нибудь из этой категории.

Часто ноутбуки ломаются по причине выхода из строя USB (выломали USB и сигнальный контакт попал на 5В). Итог — дохлый юг. Стоит посмотреть "чистоту питаний" осциллографом и потребление платы, запитав её через ЛБП.

Не стоит забывать, что зачастую некоторые мосты находятся под клавиатурой, там где они подвергаются небольшим, но частым "встряскам". Можно применить «метод прогибов и прижимов» (без фанатизма). При этом смотреть, будет ли меняться поведение платы, будет ли проскакивать тот пост на котором плата стопорится.

Проверяем на отвал сокета. Берём сухую и чистую тряпочку, сминаем её и кладём под сокет слегка прижимая. Смотрим что, где и как греется. Наиболее частая ошибка начинающих мастеров — обнаружив, что при запуске начинает греться южный мост, они сразу решают что проблема в нем. Меняют его, а плата как не работала так и не работает.

А всё потому, что южный мост работает как сумасшедший, пока не пройдёт инит и далее его работа стабилизируется (потому и может за 3 секунды раскаляться). Поэтому, в процессе диагностики желательно повесить на его хотя бы небольшое пассивное охлаждение (чтобы он не сдох).

Если совсем ничего не помогло, можно воспользоваться диагностическим прогревом отдельных чипов (помогает убедится в неисправности чипа). Однако надо учитывать, что далеко не все чипы ведутся на прогрев, а некоторые вообще категорически нельзя греть. В любом случае, не перебарщивайте с прогревом и помните, что если чип заработал после прогрева то его ОБЯЗАТЕЛЬНО надо менять.

Чтобы наверняка продиагностировать поломку северного моста, нужно иметь полный сервис-мануал по данному мосту, а это "секретный" материал, к которому зачастую нет доступа. Без него можно только догадываться. В продаже можно найти специальное диагностическое оборудование, например диагностическую плату для проверки северного моста и каналов памяти. Ещё есть платы для проверки каналов связи процессора с северным мостом.

Так же не стоит забывать проверять LVDS шлейфа, подкидывать матрицы. Например на внешке есть изображение, а на матрице нет, то надо смотреть считывается ли EDID с матрицы и проверять приходит ли к ней питание. Часто бывает, что попросту нет подсветки.

Рассмотрим что такое LVDS (low-voltage differential signaling) . В переводе это "низковольтная дифференциальная передача сигналов", то есть способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары.

"Витая пара" тут имеет буквальное значение. То есть, если вы решили не менять повреждённый шлейф, а восстановить его, заменив провода, не забывайте что пары должны быть свиты друг с другом. Если этого не сделать, то получите артефакты на матрице. Кроме того шлейф должен быть должным образом экранирован.

Чтобы на матрице появилось изображение, необходимо запитать контроллер матрицы, после чего он начинает "общаться" с тем, что с ним должно общаться (север, видяха, мульт).

Предположим это будет видяха. Она определяет, что по такой-то шине подключён такой-то контроллер, считывает EDID и начинает выдавать туда изображение. Тут же смотрим есть ли сигнал регулировки подсветки (обычно с мульта).

Обращаю ваше внимание на то, что когда вы подкидываете шлейф, убедитесь что он подходит под эту модель, в противном случае есть шанс спалить что-нибудь серьёзное (типа видяхи). Бывает и такое, что люди тыкают в разъём шлейфа что попало, а по итогу хватаются за голову и не понимают в чем же дело и почему плата резко начала дымиться.

Напоследок рассмотрим назначение пинов на LVDS разъёме. Для примера воспользуемся разъёмом из схемы того же Asus k42jv, который был рассмотрен выше:

- AC_BAT_SYS - это наше высокое, идет на питание подсветки.

- +3VS - питание контроллера и прошивки матрицы

- +3VS_LCD - питание самой матрицы

- LVDS_EDID_DATA_CON и LVDS_EDID_CLK_CON - информационные каналы (считывание прошивки)

- LCD_BL_PWM_CON - регулировка яркости

- BL_EN_CON - включение подсветки

Далее идут пары LVDS , их кстати тоже следует измерять на разность сопротивлений и относительно земли, и относительно друг друга! Также на этом разъёме висит веб камера и микрофон.

Наверно на этом мы и закончим нашу тему. Попрошу не судить меня строго, возможно где-то и ошибся или не дописал чего то, буду очень рад если укажете на ошибки и, возможно, дополните.

Процедура старта компьютера называется POST (Power-On Self Test), в ходе ее происходит последовательная подготовка различных подсистем аппаратной платформы к запуску операционной системы. Простая идея, благополучно пережившая более десятка поколений процессоров, что применяется до сих пор, — перед выполнением каждого этапа, генерировать диагностический POST-код. В случае нестарта платформы его следует считать кодом ошибки, а по списку расшифровки POST-кодов сервисный инженер определит предполагаемую причину аварии.

POST-коды стали контрольными точками состояния компьютера, и благодаря этому используются в индустрии персональных платформ уже более 30 лет. За ними был закреплен диагностический порт с адресом 0080h, который оставаясь неизменным пережил даже BIOS и на законных правах теперь существует в UEFI. Казалось, что POST-диагностика останется неизменной еще много лет, однако концепция Legacy-free требует перехода к другим технологиям.

POST-диагностика в контексте эволюции шин

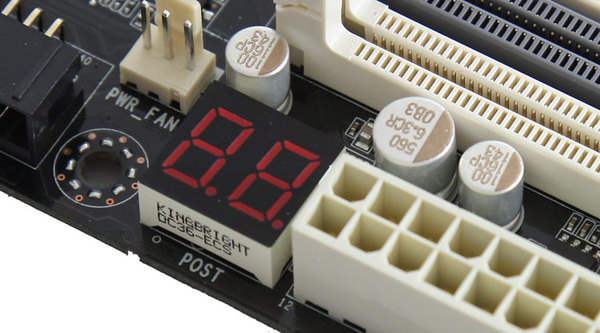

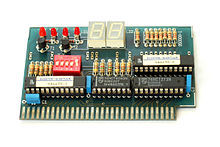

Рассмотрим принципы диагностики, используемые на персональных платформах, в свете эволюции шинных технологий. Для фиксации и отображения POST-кодов используется POST-карта. Простейшая POST-карта состоит из:

- адресного дешифратора, детектирующего вывод в порт 0080h;

- регистра-защелки, фиксирующего выведенный байт;

- дисплея, отображающего POST-код на индикаторе.

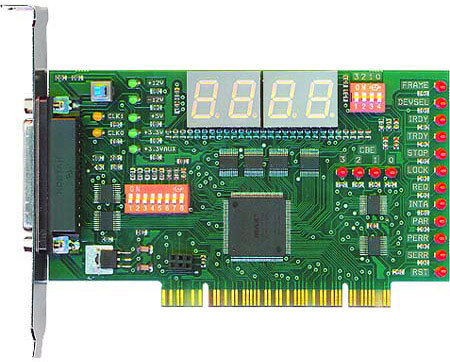

Первые POST-карты использовали ISA в качестве шины расширения. Начиная с 1999 года, ведущие разработчики системной логики стали предлагать решения, использующие наиболее продуктивную на тот момент PCI-шину. Продвинутые PCI POST-карты не ограничились формальным «переездом» порта 0080h на новую шину. Они использовали все архитектурные особенности PCI для реализации пошагового режима, расширенной разрядности самих диагностических кодов и т.п.

Дешевый ценовой сегмент заполнили устройства, преимущественно китайского производства, большинство из которых практически непригодны к эксплуатации, так как являются примером проектирования PCI-устройства с использованием идеологии ISA-шины.

Когда на основе программной модели PCI появилась шина PCI Express, казалось, что эволюция диагностических устройств обязательно последует в том же направлении. Но так не произошло. Почему? Во-первых, поменялась ситуация на рынке: мобильные решения агрессивно вытесняют настольные компьютеры. А для компактных систем слоты PCI Express даже в мини-формате — непозволительная конструктивная роскошь. Во-вторых, вспомним, что топология PCI Express обеспечивает соединение «точка-точка», которое затрудняет трансляцию циклов вывода в порт 0080h на каждый слот.

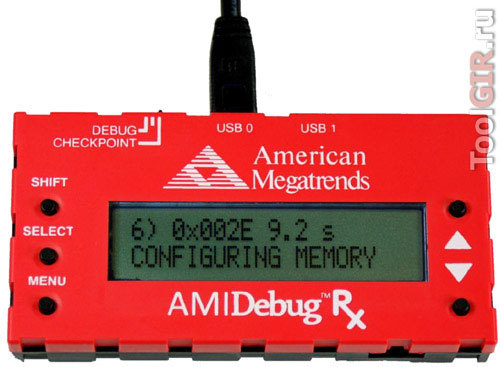

В сложившейся ситуации достойным кандидатом для организации диагностического порта оказалась шина USB. Дополнительным бонусом ее использования является мониторинг состояния платформы снаружи (без доступа к системной плате).

Bus Master как препятствие для POST-диагностики

Итак, разработчики вычислительных платформ начали рассматривать шину USB в качестве новой технологии для вывода диагностических кодов. Но тут возникла одна проблема.

Как известно, USB-контроллер является Bus Master устройством, способным взаимодействовать с оперативной памятью в обход центрального процессора. Это означает, что для выполнения заданной операции, например, чтения данных с USB-накопителя, в оперативной памяти формируется блок данных, описывающий для него задание. После этого контроллер считывает из памяти указанный блок, выполняет требуемую операцию и записывает в память статусную информацию, отражающую результаты выполнения. При передаче целевой информации, а в нашем примере это данные, читаемые с USB-флешки, контроллер универсальной последовательной шины также работает с ОЗУ самостоятельно.

Несомненно, такой подход повышает производительность, снижает загрузку центрального процессора и является хорошим примером интеллектуализации периферийного устройства. Но с точки зрения диагностики платформы мы получаем три проблемы:

- Вывод POST-кодов невозможен до момента инициализации подсистемы оперативной памяти;

- Вывод POST-кодов невозможен при неисправной или отсутствующей оперативной памяти;

- Процедура вывода POST-кодов, использующая режим Bus Master, имеет меньше шансов на безошибочное выполнение в случае неисправной платформы. Значит, сервисный инженер имеет меньше шансов увидеть диагностический код на экране POST-карты.

Архитектура USB Debug-порта в составе EHCI-контроллера

Задача, поставленная перед разработчиками USB Debug-порта очевидна из выше сказанного – реализовать некий специальный протокол работы контроллера USB, при котором режим Bus Master не используется, а данные для вывода в диагностический порт передаются контроллеру USB центральным процессором. И такой протокол был разработан. С его особенностями можно ознакомиться в презентации «USB 2.0 Debug Port» Джона Кейза , инженера компании Intel.

- Для работы в качестве DebugPort используется один из портов контроллера USB 2.0 EHCI. Функция опциональна, ее наличие декларируется структурой Debug Port Capability, расположенной в блоке конфигурационных регистров EHCI-контроллера. Указанная структура также содержит информацию, необходимую для локализации memory-mapped регистров контроллера Debug Port.

- Debug Port не использует режим Bus Master, поэтому для него не требуется оперативная память. Расписание транзакций и его дочерние структуры не используются.

- В регистрах memory-mapped I/O контроллера Debug Port реализован буфер, размером 8 байт. При отправке данных на Debug Device процессор заполняет буфер и дает команду на запуск операции. При чтении данных из Debug Device процессор ожидает завершения операции, после чего читает данные из буфера. Управление USB-операциями осуществляется программно, посредством регистра Debug Port Control / Status Register.

- Подключаемое устройство – Debug Port Device, должно соответствовать спецификации на такого рода периферию и поддерживать режим USB 2.0 High Speed (480 Mbit/s).

- Как следует из размера буфера, для работы Debug Port Device не должны использоваться передачи данных длиной более 8 байт. Базовая функциональность при взаимодействии устройства с хостом включает операции чтения структуры Debug Descriptor, описывающей конфигурацию Debug Device, которую обеспечивают каналы ввода (Bulk-In endpoint) и вывода (Bulk-Out endpoint) данных .

Особенности реализации

В модельном ряду чипсетов Intel возможность использовать Debug Port впервые появилась в 82801DB (ICH4) — южном мосте, входящем в ряд модификаций набора системной логики Intel 845. Так как архитектура Debug Port унифицирована и определяется спецификацией EHCI, используя программные инструменты для работы с конфигурационными регистрами, исследователь может определить наличие данной функциональности, даже не располагая документацией на чипсет.

Встречаются платформы, где южный мост поддерживает Debug Port, но в сеансе ОС мы не обнаруживаем структуру Debug Port Capability. Это связано с тем, что в ряде чипсетов, декларированием данной функциональности можно дополнительно управлять, посредством «теневых» конфигурационных регистров, которые инициализирует BIOS при старте платформы. В этом случае, без документации на чипсет уже не обойтись, иначе, мы зависим от того, в каком состоянии оставил BIOS ресурсы платформы при старте ОС.

С помощью программного обеспечения можно увидеть EHCI Debug Port в сеансе ОС, а заодно и определить, какой из USB-портов используется в данном качестве:

Структура Debug Port Capability для декларации отладочного порта

Debug Port в составе USB-контроллера

Новые профессии отладочных портов

Независимо от физической реализации средств отладки, интегрированных в персональные платформы, их применение не ограничивается контролем прохождения процедуры POST. Диагностический контроллер является одним из важнейших инструментов не только сервисных инженеров, но и разработчиков аппаратного и программного обеспечения. Приведем несколько примеров.

- Вывод отладочных кодов может происходить уже после завершения процедуры POST. При этом отладка распространяется на модули firmware, функционирующие в сеансе ОС. Контрольные точки могут быть реализованы в составе процедур UEFI Runtime Services, вызываемых в рабочем сеансе, а также в коде AML (ACPI Machine Language), находящимся в состав firmware и интерпретируемом ACPI-машиной операционной системы.

- Инициатором вывода контрольных точек может быть сама операционная система или приложения. Такая технология отладки особенно актуальна при написании драйверов уровня ядра (Kernel Mode Drivers), поскольку контекст, в котором они выполняются (Ring0), как правило не допускает вывода на экран штатными средствами.

Для систематизации номенклатуры отладочных устройств и методов их применения, в рамках интерфейса ACPI определена таблица DBGP (Debug Port) на смену которой, пришла таблица DBG2.

Применение таблиц DBGP и DBG2 превращает отладочные средства платформы в открытый ресурс, функциональность которого выходит за рамки самодиагностики.

Резюме

Диагностические коды будут доступны на USB-порте только в том случае, если разработчики BIOS обеспечили их вывод. К сожалению, большинство существующих на сегодня реализаций BIOS для персональных платформ не обладают такой функциональностью. Но Debug Port присутствует во всех чипсетах Intel, от ICH4 до современных PCH, в этом можно убедиться как по документации, так и путем просмотра конфигурационных регистров чипсета в сеансе операционной системы. Очевидна аналогия с «ружьем, висящим на стене», которое, как известно, обязательно должно выстрелить.

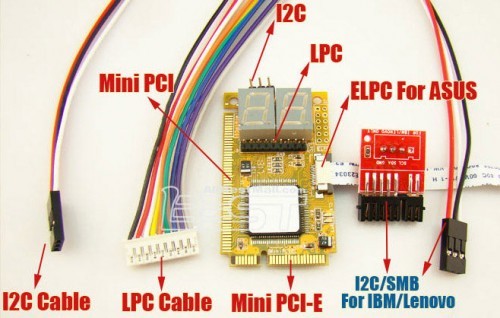

Один из вариантов диагностики материнских плат компьютеров — использование POSTкарт… Не буду описывать историю развития средств диагностики и их современные разновидности, рассмотрим частный случай — использование LPC. Интерфейс LPC (Low pin count) — использует, как видно из названия, уменьшенное количество линий для передачи информации. Для DEBUG-целей используется по-сути 7 линий: D0-D3, Frame, RST, CLK.

Некоторые производители матплат выводят эти линии (плюс землю и питание) на отдельный разъем (часто DEBUG-разъем есть в ноутбуках ASUS, Samsung). Некоторые выводят на неиспользуемые пины разъемов mini-pci, некоторые не выводят никуда — в таком случае для получения отладочной информации приходится припаивать эти самые 7 (с общим и питанием — 9) линий непосредственно к выводам мультиконтроллера (задача весьма непростая, требующая аккуратности), либо флешки БИОСа (да, были флешки которые подключались к мультиконтроллеру тоже при помощи LPC-интерфейса, т.е. он не только диагностический, а вполне себе полноценный интерфейс обмена данными). К флешке припаяться было легче, но такие флешки уже почти не встречаются, а вытеснены SPI-собратьями.

Я упоминал уже что иногда все нужные сигналы присутствуют на mini-pci разъеме — меняем вай-фай платку на post-карту и всё видим.. Но бывают еще варианты. Один из которых, достаточно простой, но судя по вопросам на форумах почему-то не всем очевидный, рассмотрю здесь подробно и с картинками.

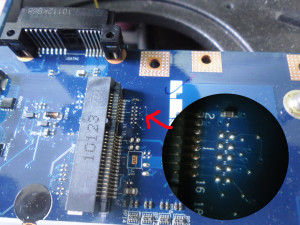

В качестве примера подвернулся Lenovo G555, платформа COMPAL LA-5972P. Схема без труда гуглится. Смотрим на стр. 31 и видим (выделил куда именно смотреть):

Итого как бы всё есть — D0-D3 на выводах 16, 14, 12, 10; frame — 8; RST — 17; CLC — 19.

Вставляем карту, включаем питание — и ничего: ни клок не мигает на карте, ни коды не идут…. Смотрим на ту же страницу схемы но в другое место:

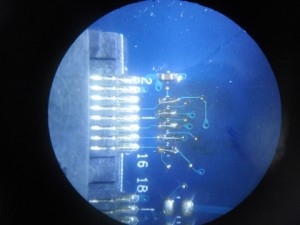

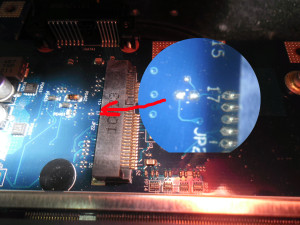

Берем указанные на схеме резисторы с нулевым сопротивлением с 5%-й точностью, и впаиваем. Если таких резисторов у вас нет (как и у меня), то можно обойтись «соплями» припоя, либо тонкими проводочками. Должно получиться примерно так:

Возле 17-го контакта (там у нас сигнал RESET) тоже видим площадки, поступаем аналогично:

А вот с 19-м немного засада…. Площадок возле разъема нет, а если посмотреть на схему — то резистора R973 нам тоже не хватает чтобы увидеть сигнал наличия тактовой частоты на пост-карте…. Не буду томить — площадка под него находится на другой стороне платы, найдена мультиметром.

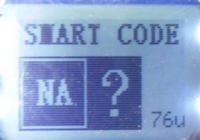

Впаиваем резитор-перемычку, вставляем пост-карту в слот от вайфая, нажимаем кнопку включения питания — и всё работает: видим POST-код 76, обозначающий в данном случае отсутствие оперативной памяти (не вставил):

Как бы и всё.. Ну, если уже рассказывать о конкретно этом случае, то кодов сначала у меня не было — был мертв 216-0752001. Поменял его на 216-0752003, коды пошли, всё заработало, клиент счастлив.

PS: Еще маленький «хинт», очевидный для тех кто смотрит схемы, но к сожалению это делают не все… Чтобы нажать на этой плате кнопку включения — необязательно подключать панель с кнопкой, что есть не очень удобно в разобранном состоянии… На плате такие вот площадки (J5):

Просто коротим их подручным токопроводящим предметом — и плата должна стартануть. Нарисовано это на 35-й странице схемы. В принципе в этой статье всё взято из схемы — как говорит детский стишок: «как хорошо уметь читать…».

POST карты не первое десятилетие используются для диагностики «железных» неисправностей компьютеров и материнских плат всевозможных форм-факторов. На данный момент этих карт создано очень много, практически для всех возможных ситуаций. Статья рассказывает о том, что такое POST карты и для чего их используют, как они работают, какие бывают и чем друг от друга отличаются.

После нажатия кнопки включения компьютера BIOS проводит поэтапную проверку и инициализацию всех элементов аппаратной части компьютера. Называется этот процесс: POST (англ. Power-On Self-Test – самотестирование после включения). Не только компьютеры, но и большинство современных электронных устройств имеют схожие системы.

BIOS сообщает статус (или результат) прохождения POST несколькими способами:

2. Звуковые сигналы. Наверное, все слышали короткий «биип» при включении компьютера – в большинстве BIOS это означает прохождение теста без ошибок и готовность к загрузке ОС. Другие варианты сигналов могут говорить об определенных проблемах с железом. Эти коды «азбуки Морзе» различаются у разных производителей и даже разных версий BIOS. Найти их обычно можно в книжке к материнке или соответствующих онлайн справочниках.

3. POST коды. В ходе каждого этапа процесса самотестирования BIOS отправляет текущий код на порт 80h (иногда 81h или другие), и если возникает ошибка, там остается или код операции, на которой произошел сбой, или код последней успешной операции. Считав этот код, можно определить на каком этапе произошла ошибка, и что могло ее вызвать. Это единственный из всех перечисленных способов, который позволяет идентифицировать проблемы на материнской плате, которая не подает видимых признаков жизни. По этой причине, он обычно используется для диагностики и ремонта непосредственно материнских плат.

Если первые два способа диагностики не требуют специального оборудования, разве что монитор и подключенный к материнской плате динамик (бывает, что его там нет), то для третьего способа вам понадобиться собственно POST карта.

Основная задача любой POST карты – это считать и отобразить текущий POST код. Считать его можно несколькими способами: по шинам ISA, PCI, LPC или через LPT порт. Есть и другие, более экзотические варианты (о них чуть позже). Кроме, собственно, отображения кода, хорошие POST карты имеют дополнительные диагностические возможности (индикаторы, режимы тестирования, встречаются даже со встроенным видеоадаптером).

Некоторые материнские платы (обычно Premium сегмента) имеют встроенный индикатор POST кодов.

Первыми POST картами были карты для шины ISA, существовавшей с 1981 по 199х годы. Используется она даже сейчас (хоть и весьма редко), в основном в промышленном и военном секторе – там, где осталось оборудование для этой шины.

Следующей массовой компьютерной шиной стала PCI. Сейчас это самая распространенная шина для настольных компьютеров. Естественно, для нее есть и POST карты всех возможных форм, размеров и функций. Самую простейшую, с обычным сегментным индикатором, можно купить за 2-3 бакса на любом Ebay, Ali и им подобным.

Еще один удобный вариант – это выносной индикатор. Он позволяет со всеми удобствами производить диагностику материнских плат, не вынимая их из системника. С одной стороны, если дело дошло до POST карты, то скорей всего материнку все же придется извлечь для ремонта, но с другой стороны – не всегда, да и POST карты просто удобный способ общей диагностики. На фото Sintech ST8679, китайская карточка с выносным многострочным LCD дисплеем.

Существуют POST карты для LPT порта – довольно простой и удобный способ диагностики для любого компьютера или ноутбука, имеющего этот самый LPT порт. Из-за технических особенностей, они не имеют возможностей, присущих картам для PCI, но это компенсируется простотой и доступностью. Требуют питание по USB (для этого и наличие порта на плате).

Однако LPT изживает свой век, и на современных компьютерах их уже почти не встретишь, соответственно, доживают свои дни и эти карты.

Служивший нам верой и правдой много лет PCI, постепенно вытесняет более современная PCI-Express. Немалое количество современных материнских плат вообще не имеют слота PCI (хотя и могут иметь саму шину). Но с PCI-E не все так просто. Во-первых, сама диагностика с помощью PCI-E на данный момент вещь мутная, хотя бы, из-за отсутствия адекватной информации. Во-вторых, с PCI-E все зависит от конкретного изготовителя – нет гарантии, что коды будут выводиться; если и выводятся, то нет гарантии, что по стандартному порту и в стандартном виде.

Одним из самых перспективных способов диагностики на сегодняшний день является USB. И главная тому причина – повсеместная распространенность этого интерфейса. Как мы уже выяснили, отсутствие того или иного разъема на материнской плате может стать преткновением для диагностики. И эту проблему как раз решает USB – парочку портов имеют буквально все компьютеры и ноутбуки, выпущенные за последние 15 лет.

Для такой диагностики необходимо наличие в системе USB Debug Port – это своего рода расширение USB, позволяющее передавать диагностическую информацию. В USB 3.0 реализация Debug Port получилась сподручней (подробней о Debug Port можно прочитать по ссылке). Кроме передачи POST кодов, Debug Port позволяет производить полноценную отладку кода BIOS и UEFI.

Было даже выпущено несколько устройств разными компаниями. NET20DC от Ajays (компания почти тут же обанкротилась, так как поставщики отказались поставлять им компоненты для сборки девайса). Insyde H2O DDT от Insyde Software (выпущен, вроде, в 2008 году, но информация об этом девайсе канула в лету даже на официальном сайте). Оба этих устройства скорее отладчики, хотя и имеют возможность захвата POST кодов.

С ноутбуками все немного сложней. Наиболее распространенные разъемы, которые можно использовать для диагностики – это mini PCI или Mini PCI-E (у более современных).

Опять же, есть вариант использования шины LPC. На материнских платах порта для подключения к этой шине вполне может не быть, поэтому придется напрямую подпаиваться к плате или контролеру.

Отдельные производители имеют свои способы диагностики, тут уж действительно «кто во что горазд». К сожалению, эта информация обычно является достоянием лишь производителя и его внутренних сервисных центров, поэтому все существующие варианты POST карт в общем доступе вряд ли найдутся.

Такое вот у POST карт интересное прошлое и насыщенное настоящее. Что их ждет в будущем? Поживем – увидим. Но реалии таковы, что в нынешнюю эпоху потребительства от девайсов зачастую избавляются раньше, чем они успевают сломаться. А если и ломаются, то оказываются в сервисных мастерских производителя, где уж явно должно быть подходящее диагностическое оборудование.

Can be found on some new ECS motherboards, such as ECS H61H-G11, intended for POST card connection. Uses mini-IDC connector with 2 mm pitch.

Карта во время работы не останавливается на кодах 25\26 (как часто бывает со многими безымянными картами из Поднебесной), помимо чтения стандартных "POST" кодов, читает "QiGuan Open Code" (если он есть, отображается на двух-символьном дисплее, см. руководство пользователя), имеет четырех-символьный дисплей для отображение "QiGuan Open Code" (отображает два двухзначных кода, см. руководство пользователя), и предлагает функцию проверки стабильности системы:

Приходит карта в аккуратной пластиковой коробочке упакованной в конверте вместе с документацией от предыдущих версий диагностических карт этого же производителя (можно скачать по ссылкам в секции "Документация").

Качество перевода руководства пользователя с китайского языка на английский можно оценить по следующему блоку (к сожалению, это практически стандарт у большинства китайских производителей, встретить качественно переведенное руководство — большая удача):

Мой образец оказался достаточно качественно собран: не пропаянных элементов и «перемычек» нет, флюс отмыт, однако, судя по отзывам покупателей, качество сборки может «плавать» от образца к образцу, некоторый элемент лотереи тут присутствует.

На новой плате имеется наклейка с QR-кодом следующего содержания:

+ Относительно не дорого.

+ Судя по отзывам «ремонтников» (у меня значимого опыта работы с этой картой еще нет) не плохо справляется со своей задачей, когда это возможно (передача кодов реализована на мат. плате)

+ Разнообразные варианты подключения (PCI\PCI-E\MiniPCI-E\LPC\EC)

Читайте также: